Johnson约翰逊计数器Verilog实现

描述

问题:实现 N 位 Johnson Counter。

当 N = 4 时,输出应该是

0000 -> 1000 -> 1100 -> 1110 ->

1111 -> 0111 -> 0011 -> 0001 ->

0000 -> ...

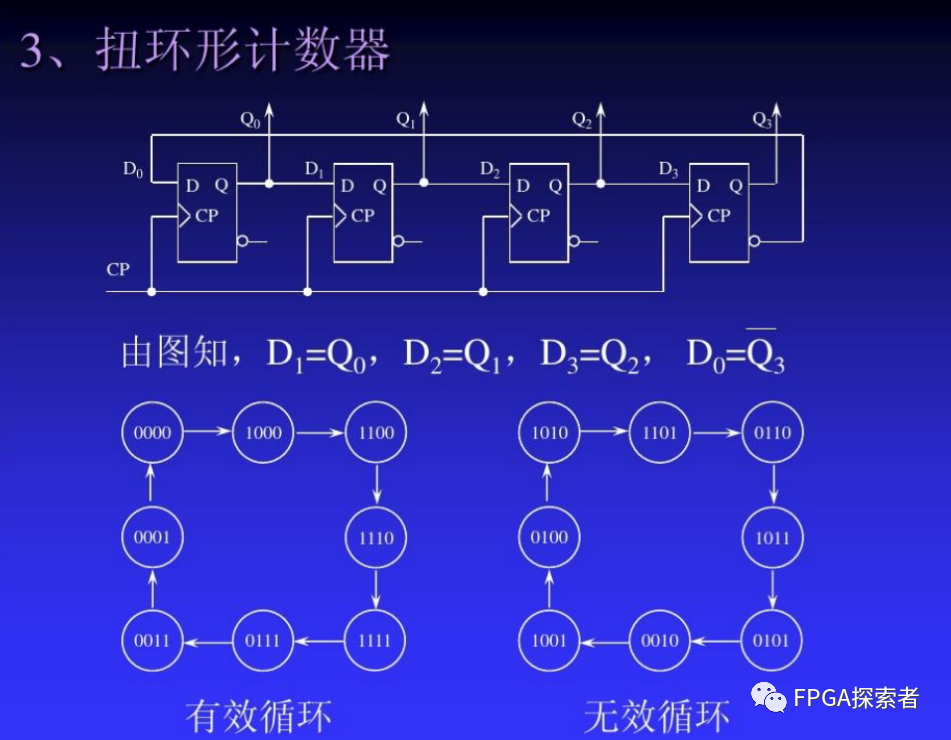

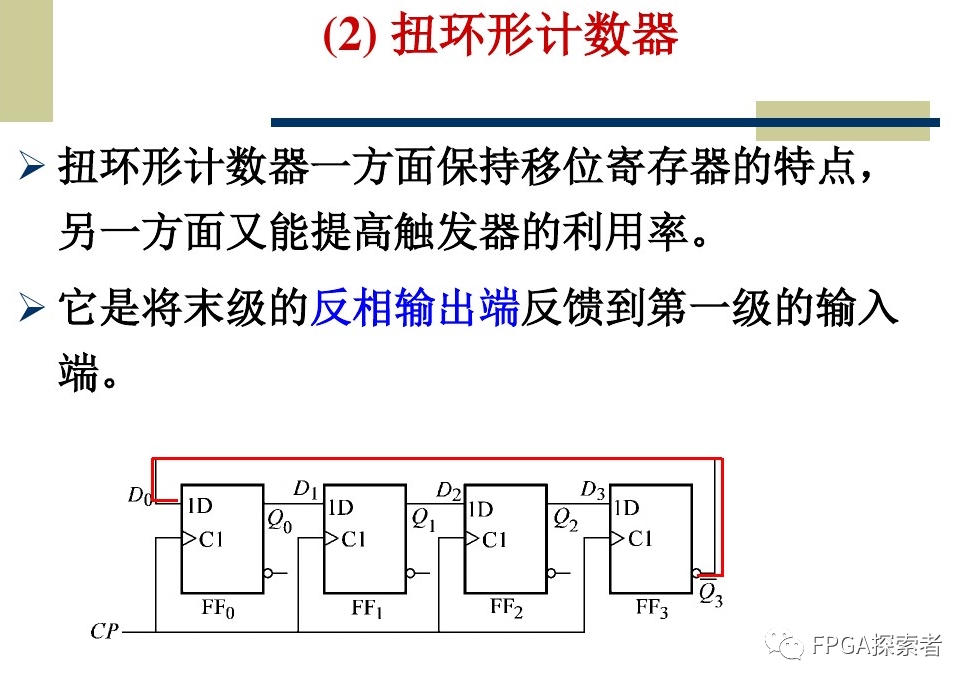

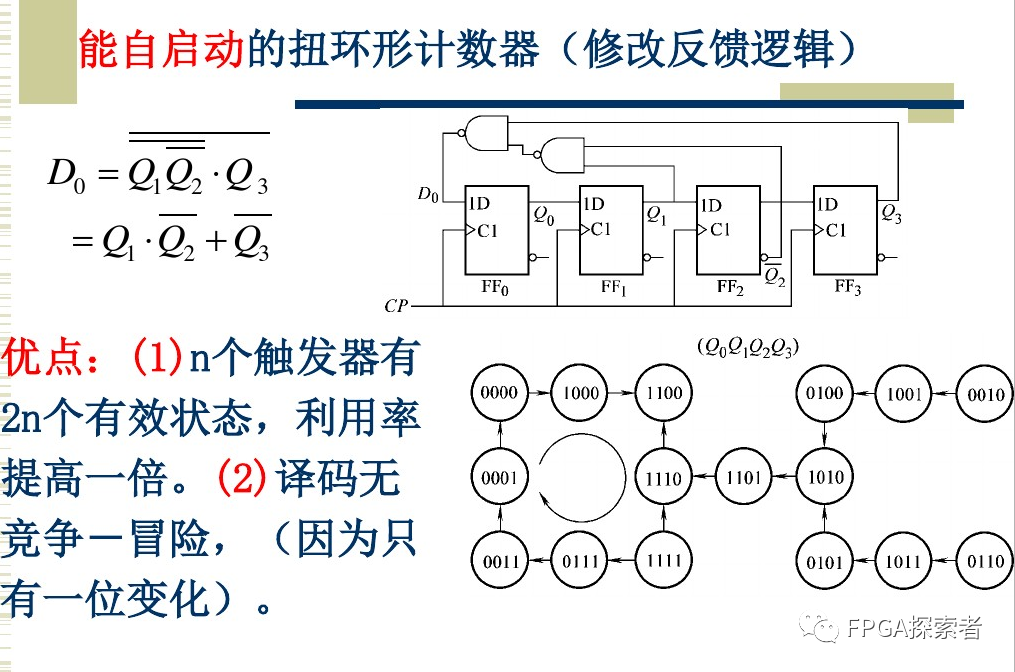

如下图所示,扭环形(约翰逊)计数器最后一个触发器的输出取反 ~Q3,然后输入回第一个触发器的输入 D(0) = ~Q(N-1),其余触发器的输入来自前级的输出 D(i+1) = Q(i)。

D(0) = ~Q(N-1)

D(i+1) = Q(i)

Johnson 约翰逊计数器Verilog 实现

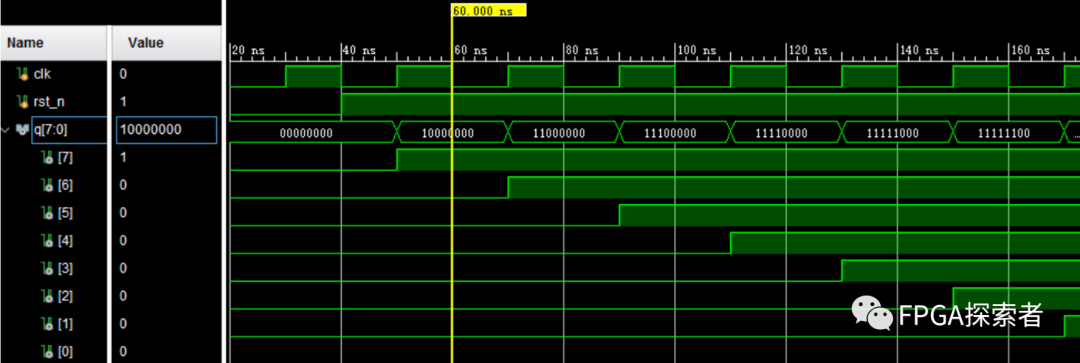

用 Verilog HDL 写一个 8-bit 的 Johnson 计数器,N = 8。

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q <= {N{1'b0}};else if(!q[0])q <= {1'b1,q[N-1:1]};elseq <= {1'b0,q[N-1:1]};endendmodule

仿真图:

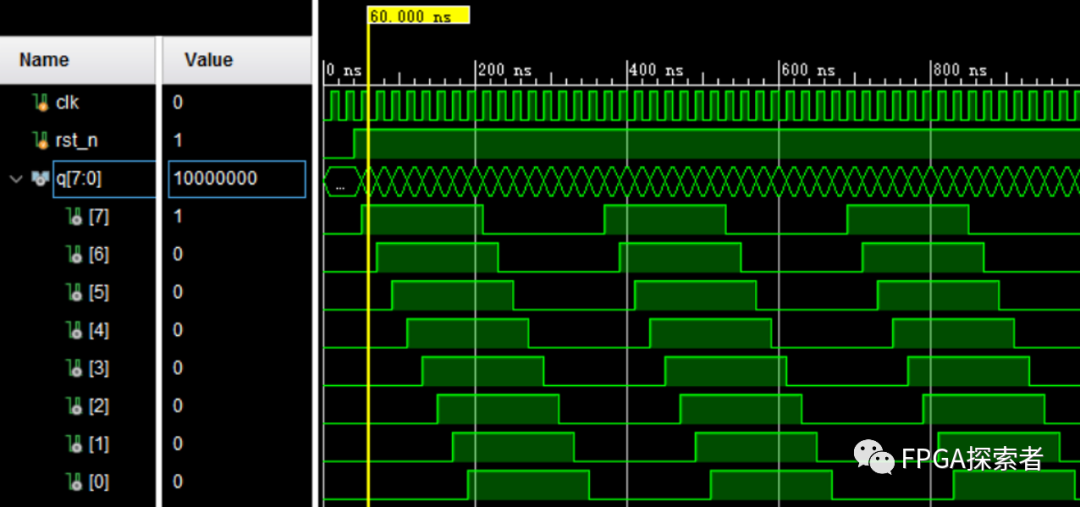

第二种:

module johnson#(parameter N=8)(input clk,input rst_n,output reg [N-1:0] q);always @ (posedge clk,negedge rst_n)beginif(!rst_n)q <= {N{1'b0}};elseq <= {~q[0], q[N-1:1]};endendmodule

Johnson 约翰逊计数器

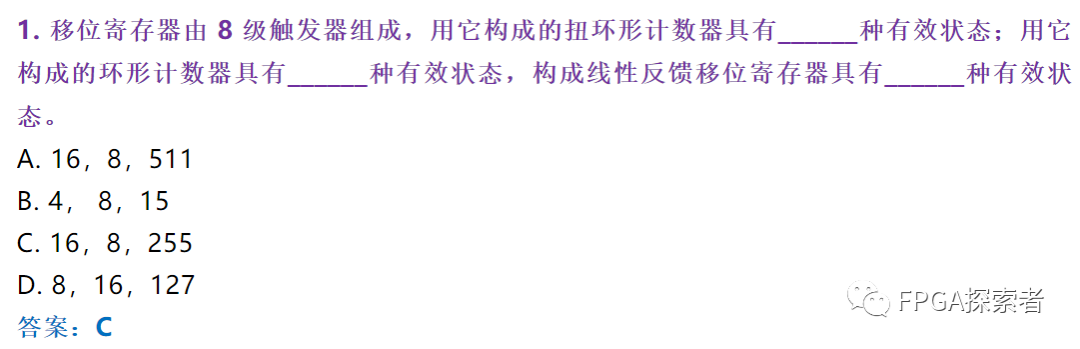

(1)扭环形计数器,约翰逊计数器,每次状态变化时仅有一个触发器发生翻转,译码不存在竞争冒险,在n(n≥3)位计数器中,使用2n个状态,有2^n-2n个状态未使用;

(2)环形计数器,正常工作时所有触发器中只有一个是1(或0)状态,计n个数需要n个触发器,状态利用率低;

(3)n个寄存器的线性反馈移位寄存器LFSR可以产生的最长的随机序列是2^n−1长度(即m序列)。LFSR常被用来生成m序列,也可产生和校验 CRC。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

5 级约翰逊十年计数器-HEF4017B_Q1002023-03-03 407

-

带 10 个解码输出的 Johnson 十进制计数器-74HC_HCT40172023-02-16 613

-

Verilog实现计数器在某个区间内循环计数,递增递减2022-04-07 6564

-

基于74HC595计数器移位寄存器的评估套件2020-07-29 1945

-

约翰逊戒指计数器的旋转运动和真值表发生器电路2019-06-26 10215

-

星巴克CEO凯文·约翰逊:瑞幸咖啡不太可能超越我们2019-02-13 697

-

一个连环无敌面试题--计数器2018-05-16 6996

-

十进制计数器/分频器2017-04-06 4037

-

高速数字设计(霍华德.约翰逊版)2016-05-16 5043

-

高速电路设计(霍华德.约翰逊版)2016-05-12 8177

-

C187 2-10进制计数器/脉冲分配器的应用线路图2010-10-19 3080

-

基于互相关分析的约翰逊噪声测温法研究2010-08-03 694

-

格雷码计数器的Verilog描述2009-08-03 805

-

约翰逊(johnson)计数器构成的程序脉冲发生器2009-03-29 2156

全部0条评论

快来发表一下你的评论吧 !