西门子EDA xPD技术助力制胜未来

描述

过去几年,芯片制程向着微型化持续推进,5nm乃至3nm的工艺制程层出不穷,逐渐逼近物理极限。同时,行业也普遍面对来自成本、风险、单片缩放的限制以及产品上市时间缩短,迭代压力增加等重重挑战,行业普遍认为先进封装会成为下一阶段半导体发展的重要方向,那么面向未来等先进封装之争,企业该如何掌握优于竞争对手的高效设计密码呢?

快30%

西门子EDA xPD技术助力制胜未来

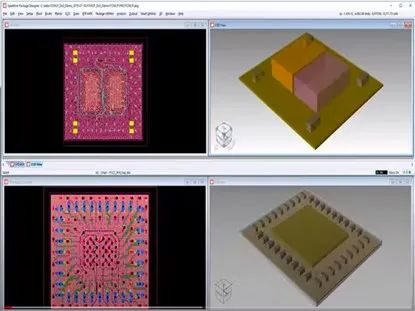

Xpedition Package Designer(xPD)是西门子 EDA面向先进封装和2.5异构装配的物理设计和验证解决方案,xPD在一个平台中,为复杂的封装和中介层技术提供强大的支持。xPD拥有创新的验证、设计自动化、优化和良率改善技术,可确保设计符合效能、可靠性及制造要求。

xPD解决方案,针对包括嵌入式桥在内的,有源和无源嵌入式器件提供全面支持。

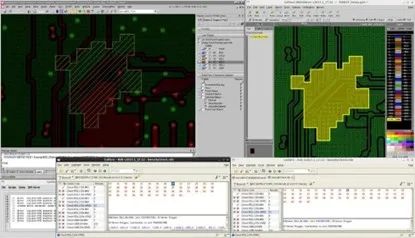

xPD解决方案具有Xpedition获得专利的自动交互式草图布线技术。

xPD的集成式3D环境,支持在2D和3D视图中实时查看编辑操作,无需使用特殊插件或单独的查看器。

为满足时间和性能的规范要求,需要专门调整走线,以达到匹配长度或时序预算。xPD提供了适用于高速调整的自动规划和交互功能,在调整图形的交互式编辑过程中,会自动更新阴影线填充和区域填充。

根据可用空间,经常需要在不同区域使用不同尺寸的过孔。xPD支持根据定义的走线区域,自动调整过孔大小的规则。当走线在走线区域之间过渡时,过孔会根据每个区域定义的规则动态变化,

除了针对约束执行标准动态设计规则检查之外,xPD还包括一个强大的几何引擎。能够检查复杂的工艺规则。

xPD还包括使用准静态场解算器,执行部分和完整封装寄生参数提取,以及生成IBIS封装模型的功能。设置和启动操作均在xPD环境中完成,简化了非分析专家的操作流程。

依照 IC 晶圆代工厂的方法和技巧,众多新兴领先的 HDAP 流程均要求金属区域的 GDSII 及类 IC 制造约束条件,以控制良率、处理Degassing hole和改善设计质量。当需要对设计进行验证和signoff时,xPD可与验证/signoff流程的黄金标准calibre实现独特集成。确保快速准确且高效地进行GDSII 光罩 Signoff。

想要了解更多xPD解决方案?xPD专题页面重磅上线。在这里您可以随时查阅xPD解决方案相关产品资料、白皮书、应用解决方案,或与专家直联。西门子EDA将强势助力,在未来高密度先进封装之争中脱颖而出,加快产品上市时间,实现降本增效,制胜未来!

审核编辑 :李倩

-

西门子EDA与北京开源芯片研究院达成战略合作2025-09-05 4638

-

西门子发布关于美国解除近期对中国EDA出口限制的声明2025-07-03 2395

-

西门子推出用于EDA设计流程的AI增强型工具集2025-06-30 2810

-

西门子EDA工具如何助力行业克服技术挑战2025-03-20 1969

-

西门子EDA新一代平台版本升级2025-02-27 982

-

是德科技与西门子EDA深化合作,共促无线与国防通信系统设计2024-10-30 1426

-

nepes采用西门子EDA先进设计流程,扩展3D封装能力2024-03-11 3188

-

EDA助力良率提升:紫光展锐与西门子的成功合作2024-01-26 1532

-

助推半导体创新需求,西门子EDA峰会揭秘AI工具链和创新平台2023-09-04 3418

-

加速创“芯” 西门子EDA技术峰会在沪举办2023-08-27 568

-

西门子收购Solido强势进军EDA领域2018-01-03 2139

-

西门子收购Mentor会对EDA工具用户带来哪些改变?2016-12-08 1522

-

EDA三巨头之一的Mentro被西门子收购 这个市场怎么了?2016-11-23 9141

全部0条评论

快来发表一下你的评论吧 !