Hermes3D进行倒装焊-金线(FC-BW)BGA封装的电磁场仿真流程简析

描述

为解决SOC片上系统的设计瓶颈,SiP(system in Package)微系统技术已成为最普遍的应用手段。SiP能在同一个封装基板上布局多个裸die,实现了系统间快速互联互通。 SiP的实现有两种形式,一种是传统BGA形式,它利用封装基板互连,可以通过ubump或wirebond进行die和基板连通;另一种是2.5D、3DIC先进封装形式,利用interposer(硅中介层)及TSV(硅通孔)实现水平RDL布局及垂直方向通孔连接。 本文介绍的是利用芯和半导体Hermes 3D软件,实现“倒装焊-金线(FC-BW)BGA封装的电磁场仿真”的应用。通过Hermes 3D快速的版图导入、bump添加、版图切割、端口添加等功能,便利地完成仿真工程的建立以及模型抽取。

Hermes 3D的FC-BW BGA仿真建模流程

1. 软件概述

Hermes 3D是一款针对各类封装和PCB的电磁场仿真平台。它支持主流版图文件导入,例如mcm、sip、brd、dxf、dwg、gds、ODB++、PADs等文件格式;支持版图在软件内自动或手动随意截取操作;采用3D FEM求解引擎,能对各类3D结构准确仿真建模;支持多种端口激励添加,例如lumped port、wave port、coax port、annular port等;支持HFSS工程脚本导出,方便用户横向对比仿真精度。

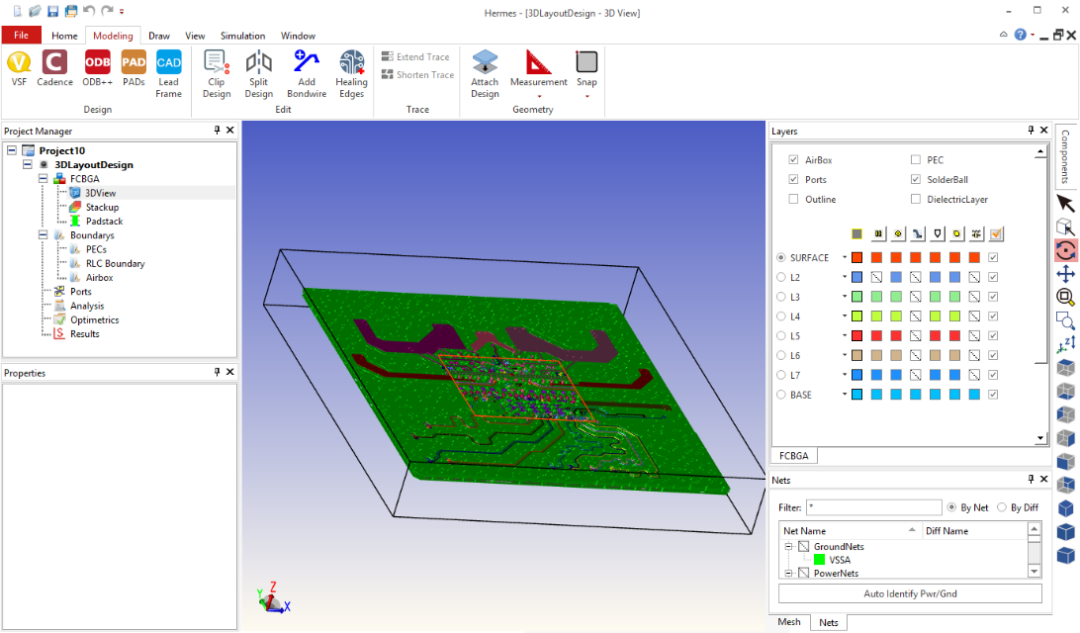

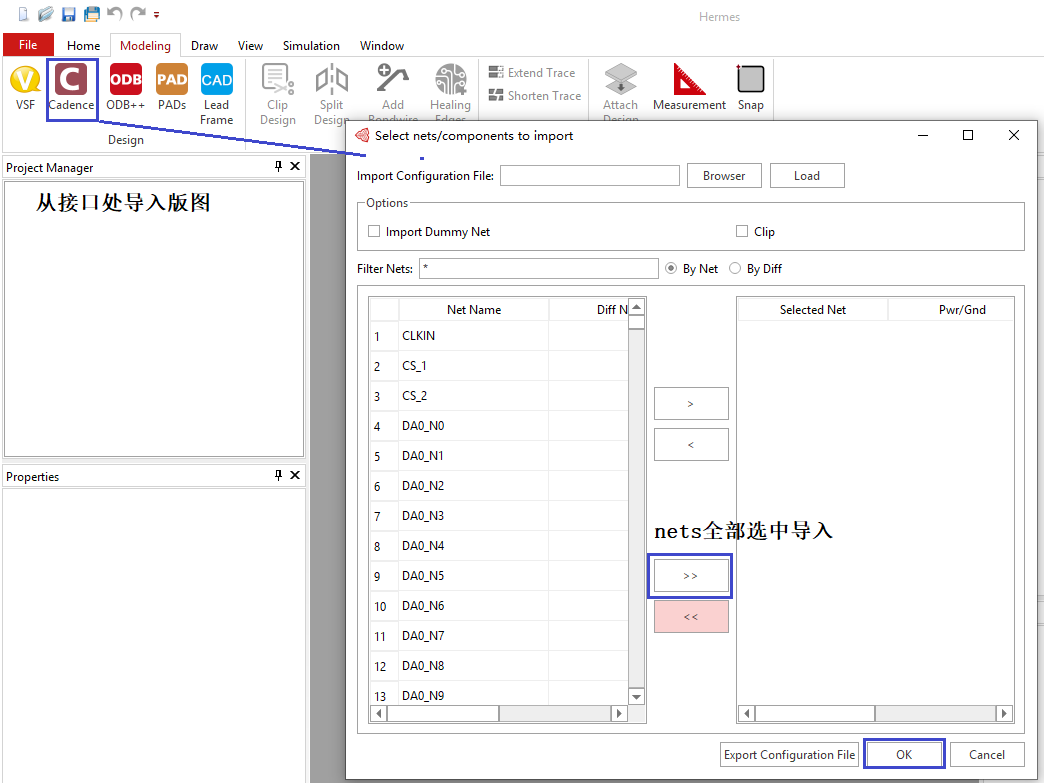

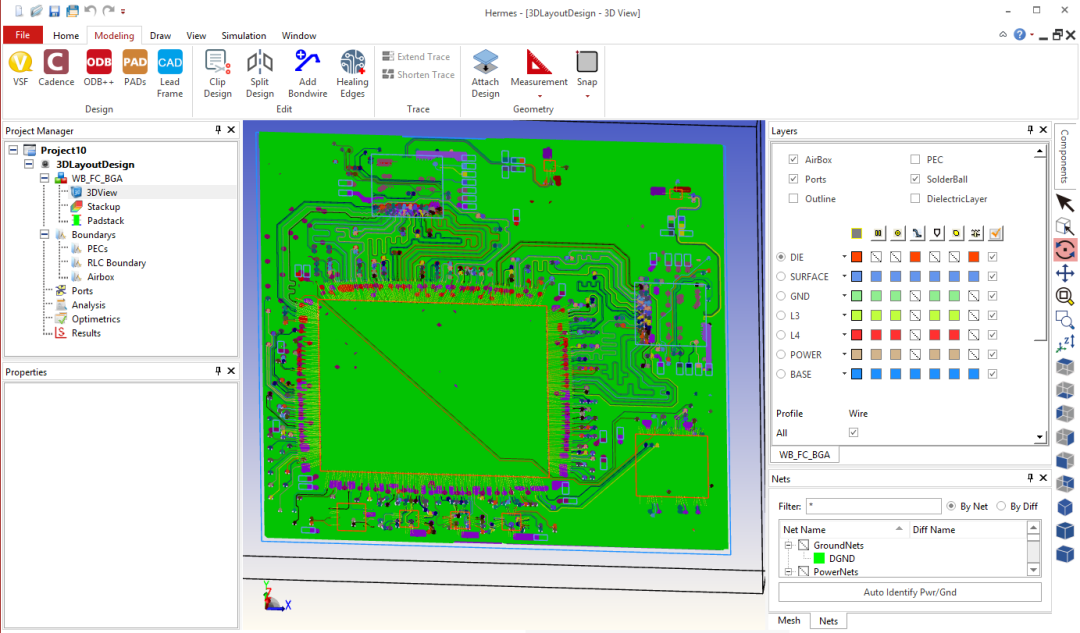

2. 导入FC-BW BGA版图文件

Hermes 3D能够快速导入.sip版图格式。其中,版图中的nets可以全部导入,也可以根据需求选择性导入。 当导入版图文件时,所有相关金属层、过孔、介质的材料信息也会一并导入,生成叠层文件,用于仿真求解。

本例中,有8个die通过金线和封装基板连接,其中两个die是flipchip形式,通过ubump和封装基板连接,因此结构属于FC-WB混合类型。

3. 仿真前设置

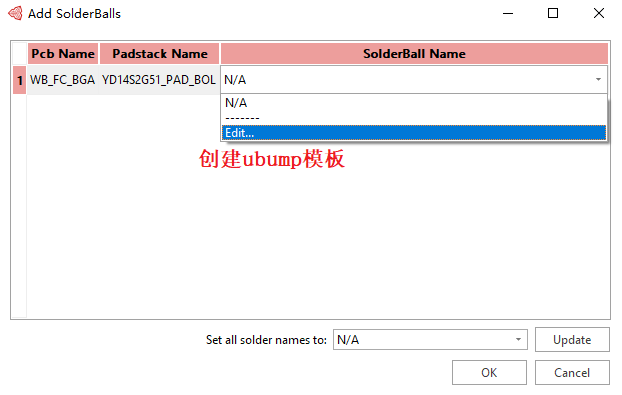

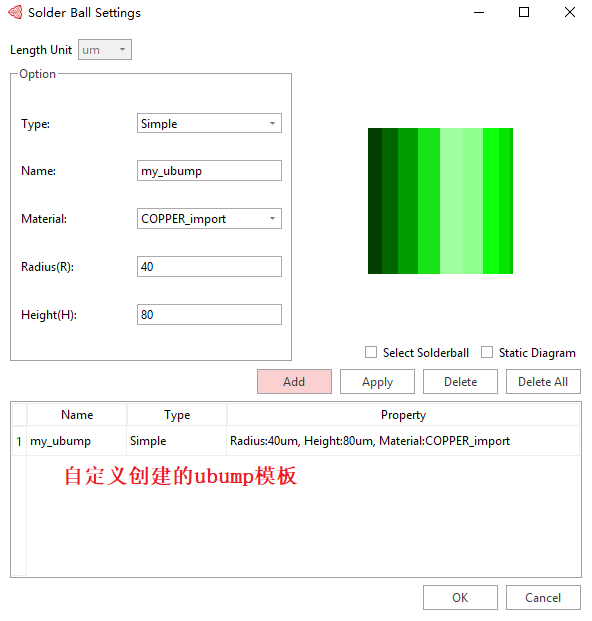

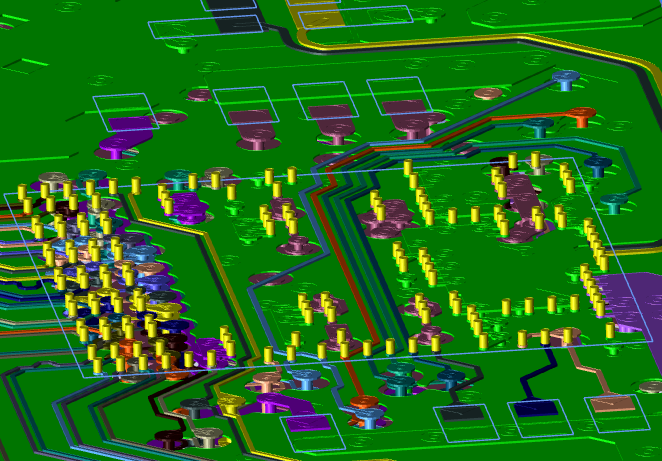

(1)添加FC结构的ubumpHermes 3D提供ubump自动添加功能,选中die结构,创建ubump模板,软件会在封装的finout位置添加对应的ubump结构。

首先找到FC连接的die名称:

点击Edit进入ubump创建窗口:

自定义ubump模板:

软件自动在finout位置布满ubump结构:

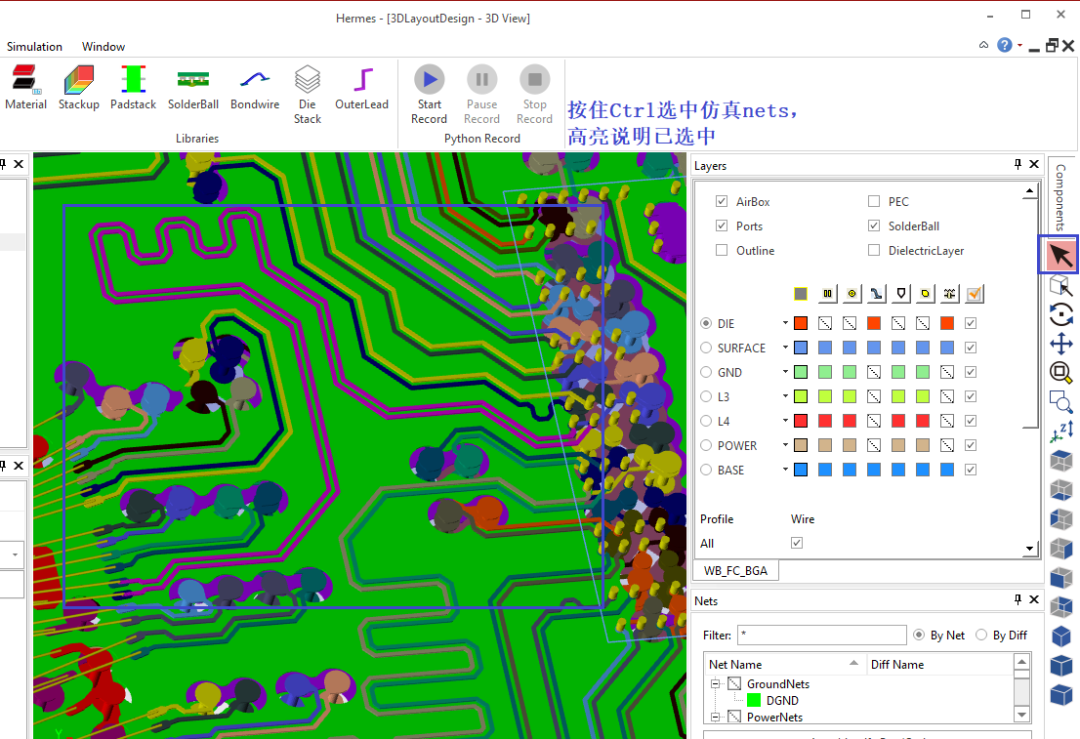

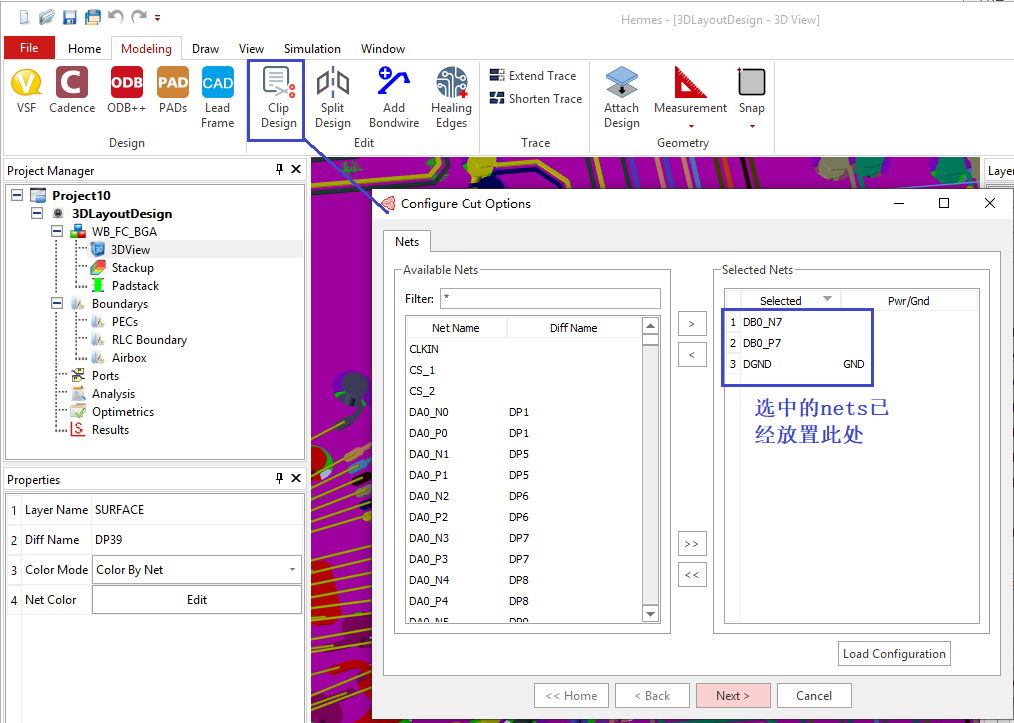

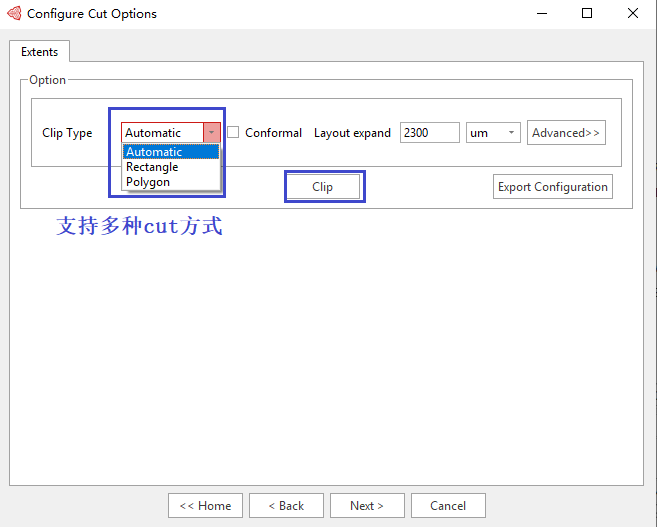

(2)按网络nets进行版图切割Hermes 3D支持信号网络选择,然后根据nets区域可自动进行版图切割,操作如下。 连续选择需要仿真的nets和参考地:

点击Clip Design,开始切割版图:

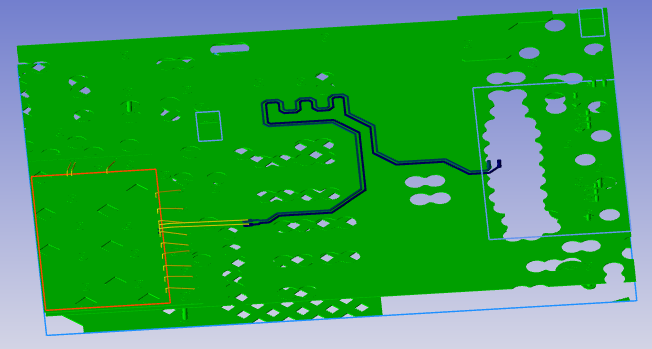

选择切割方式,开始切割:

最终根据选择nets,自动完成版图切割:

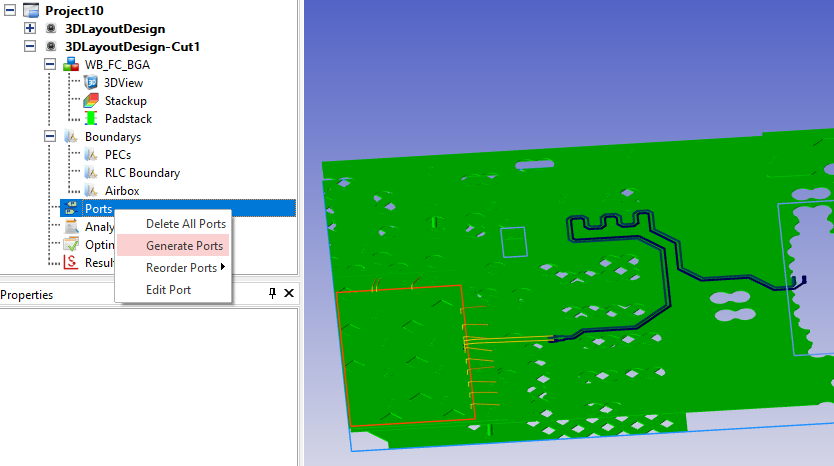

(3)激励端口添加

版图切割完成后,用户必须添加端口激励才能仿真。本文以差分nets添加激励端口为例,进行演示。

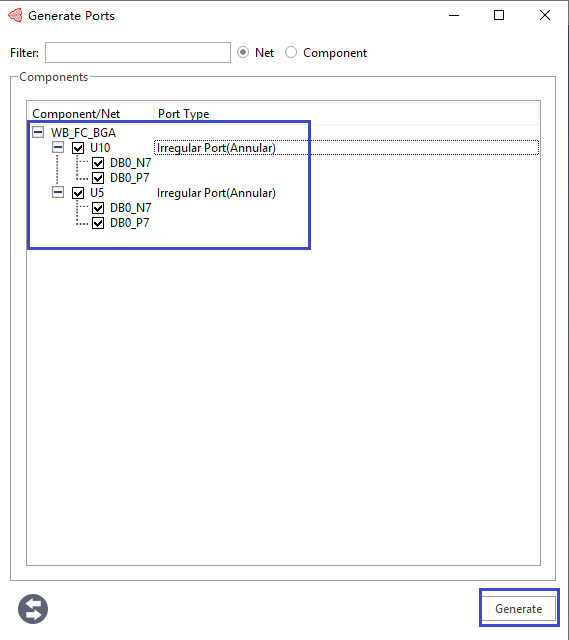

首先点击Generate Ports:

勾选nets相关的component,点击Generate生成激励ports:

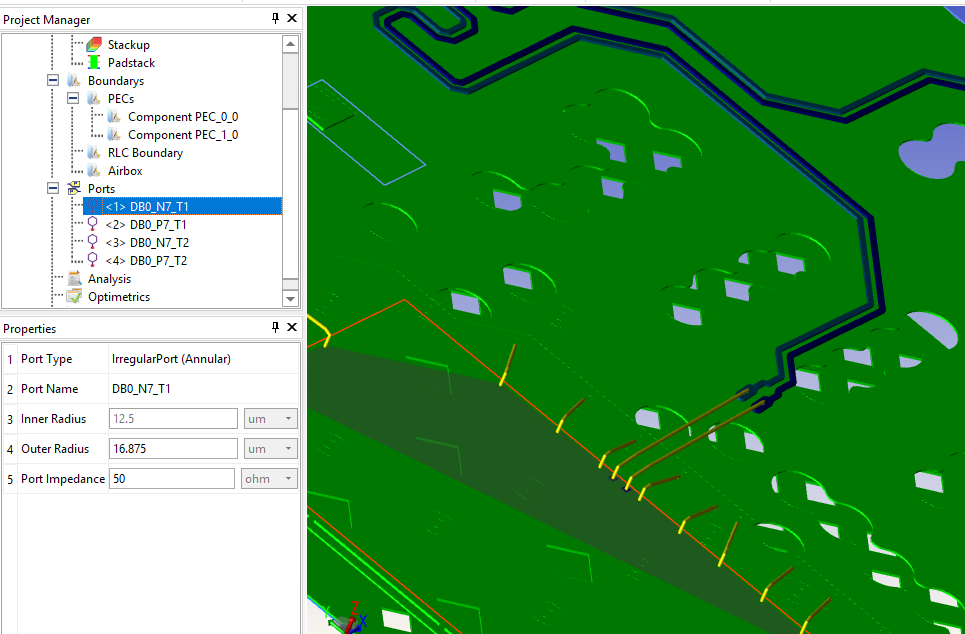

此时在ubump和wirebond端点处自动添加了环形激励端口,如下图所示:

(4)提交电磁场仿真

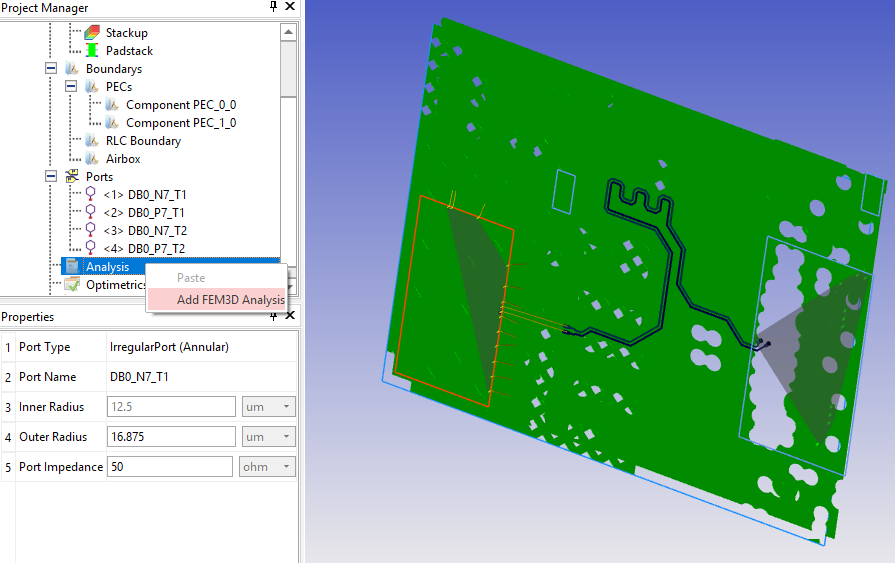

首先添加仿真分析类型:

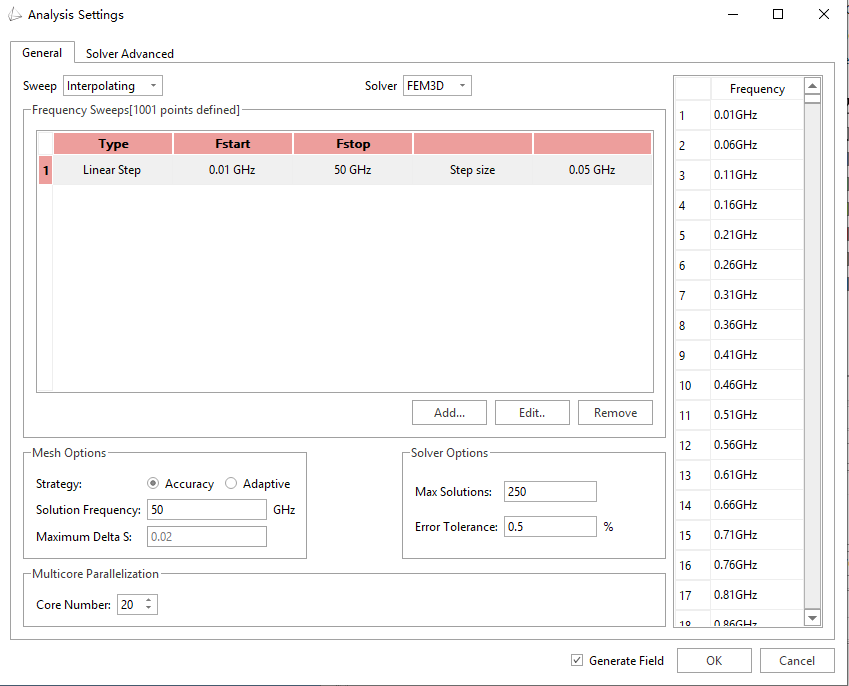

接着设置扫频范围:

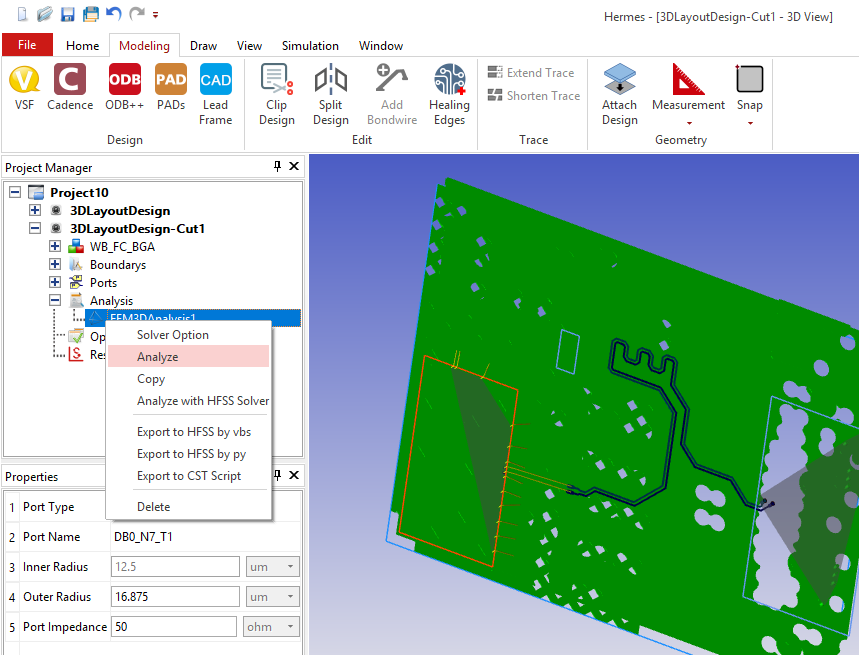

最后提交仿真任务:

4.仿真结果分析

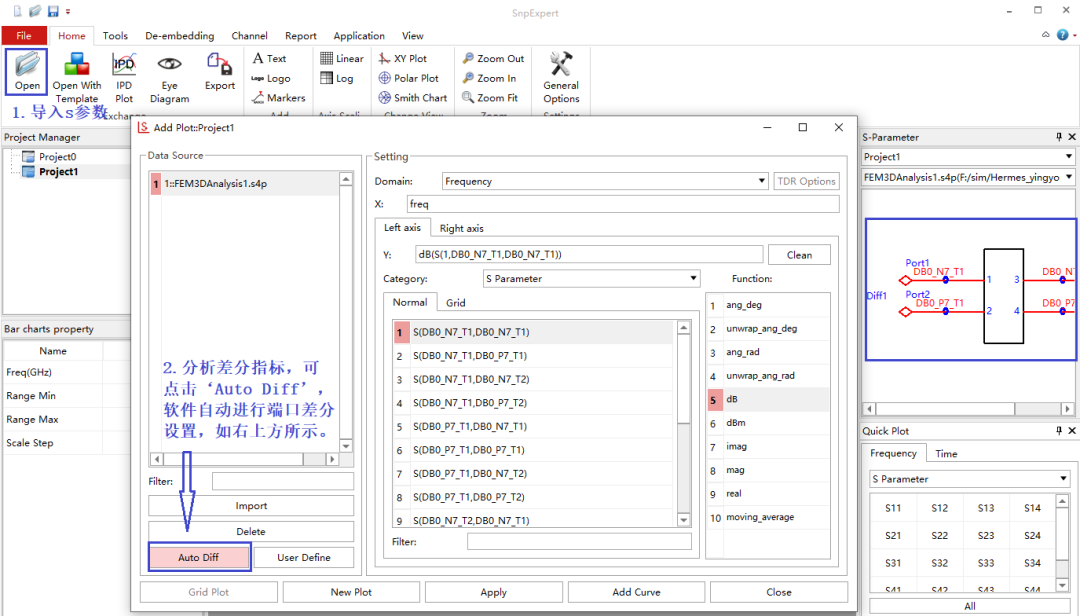

Hermes 3D完成BGA封装仿真后,用户可利用芯和半导体的s参数后处理工具SnpExpert进行结果查看和指标分析。 首先导入s参数,并完成差分端口配对:

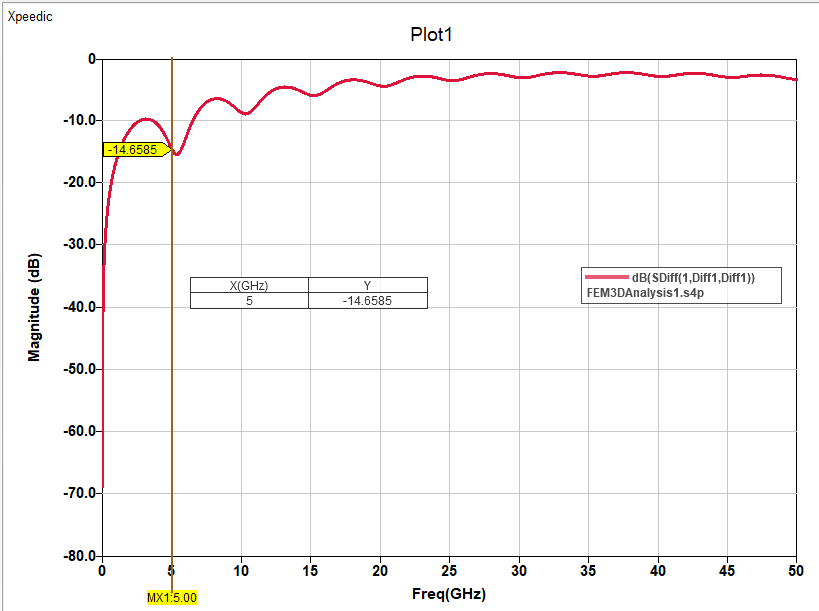

接着查看差分回波损耗:

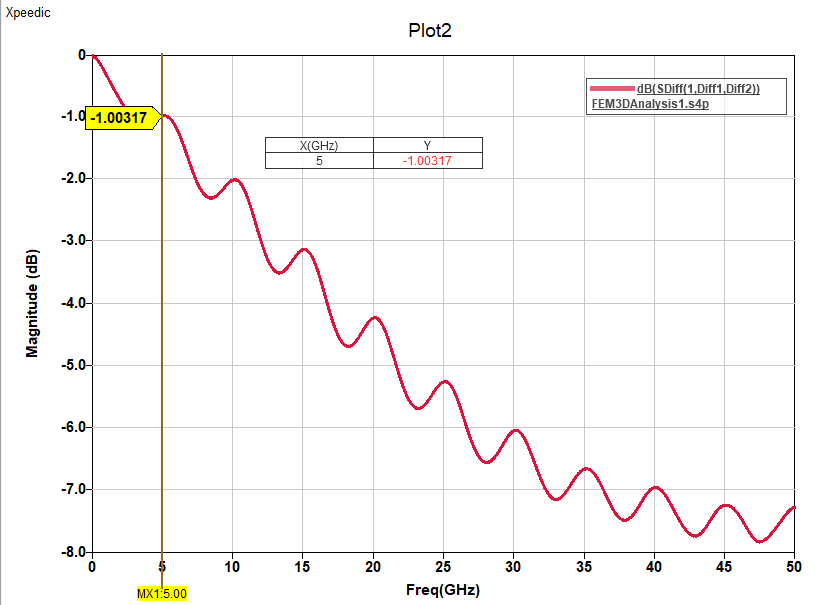

查看差分插入损耗:

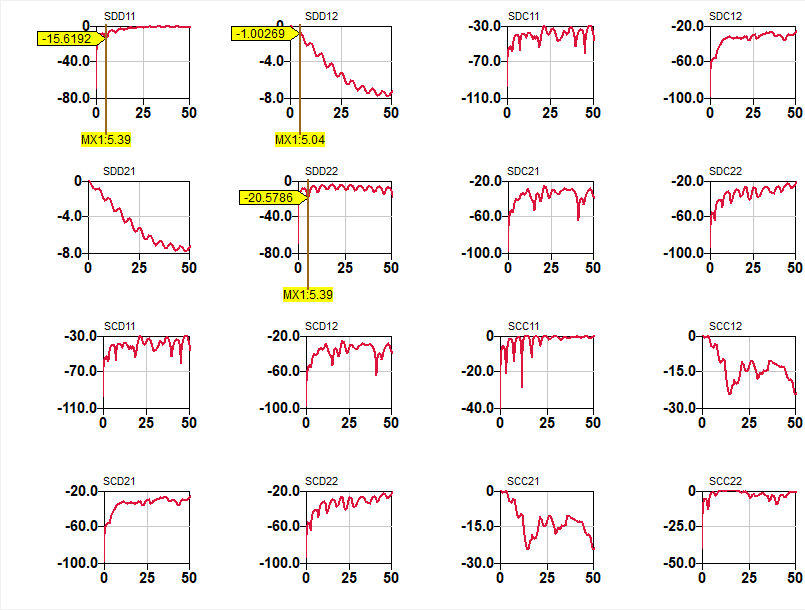

SnpExpert也支持Grid模式显示所有指标曲线结果:

总结本文通过实际案例介绍了Hermes 3D进行倒装焊-金线(FC-BW)BGA封装的电磁场仿真流程,并利用SnpExpert软件进行S参数分析。 Hermes 3D提供了向导式的建模流程,并简化了叠层建立与设置。这种方案不需要用户太过关注复杂的软件设置,不需要特别了解电磁场仿真原理,使得用户能够快速上手,并正确生成仿真模型。

原文标题:【应用案例】如何快速实现倒装焊-金线混合的BGA封装建模仿真?

文章出处:【微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

审核编辑:刘清

-

新能源汽车电子水泵电机电磁场仿真分析2025-07-17 681

-

HFSS高频电磁场仿真应用2016-04-22 8353

-

AR手持电磁场测量系统2018-09-25 3350

-

电磁场分析软件Infolytica的强大功能2019-06-27 3434

-

【技术】BGA封装焊盘的走线设计2023-03-24 3585

-

工程电磁场导论2008-09-16 1834

-

电磁场与电磁波pdf2008-10-30 2244

-

《电机内的电磁场》(第二版)2010-11-09 988

-

简析BGA封装技术与质量控制2010-03-30 1829

-

使用MATLAB实现电磁场仿真的报告免费下载2021-01-21 1251

-

射频微波器件的电磁场和电路协同仿真2021-06-04 1038

-

芯和半导体设计小诀窍 如何使用Hermes3D仿真ODB++格式文件2022-09-28 1852

-

倒装芯片球栅阵列工艺流程与技术2023-04-28 10912

-

如何使用Hermes平台的X3D实现对封装走线的RLGC提取呢?2023-10-10 1817

-

三大电磁场仿真软件有哪些2023-12-21 16327

全部0条评论

快来发表一下你的评论吧 !