基于GaN器件的驱动设计方案

电源/新能源

描述

氮化镓(GaN)器件具有类似硅的电性能,可以由硅MOSFET设计中使用的许多现成的驱动产品驱动。

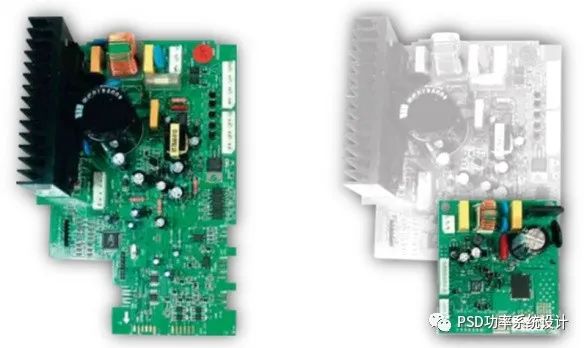

GaN具有低RDSon/VDSon、高电子迁移率和其他特性,从而实现更高效的设计。更高的开关频率允许设计师在效率和开关速度之间进行权衡,以实现应用优化设计。这些特性使解决方案更高效,运行更冷,体积更小四倍,成本比同等的基于Si的设计低10%-20%(图1)。

GaN的最佳应用是工作电压在48 V到600 V之间的应用,这使得它非常适合提供更紧凑、更冷的运行和更经济高效的硅基MOSFET替代品。

图1:氮化镓晶体管可以实现更高效、更冷的运行、紧凑和成本效率更高的设计

驱动要求

GaN的电学特性不同于硅器件。为了确保在低电压下启动整流器时,栅极和栅极的阻抗都很低,所以在低电压下启动整流器时必须小心。

矛盾的是,这些器件的开关速度可能太快,这可能会导致振铃,并将不需要的高频注入到它们所驱动的电路中。它们的高dV/dt可以通过在“硬”切换转换期间创建直通来降低效率。幸运的是,这是可以控制的。业界已经开发出几种方法来“规范化”GaN器件驱动特性:

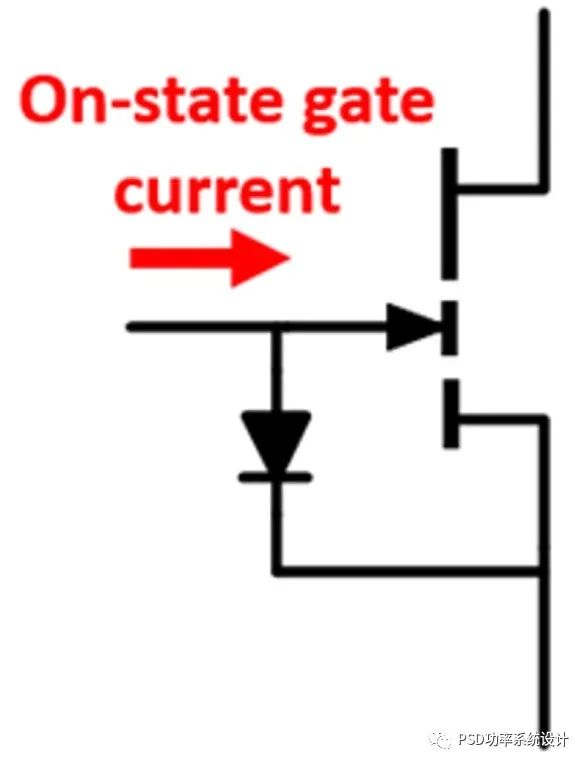

增强模式栅极注入晶体管(GIT):在GaN-GIT上添加一个p掺杂栅极,使其起到常闭器件的作用(图2)。这允许精确控制开/关开关速度,并可并联连接,以支持更高电流的应用。在消极方面,它们需要一个特殊的驱动电路,具有非常高的栅极电流要求,这会降低效率。

图2:增强模式GIT

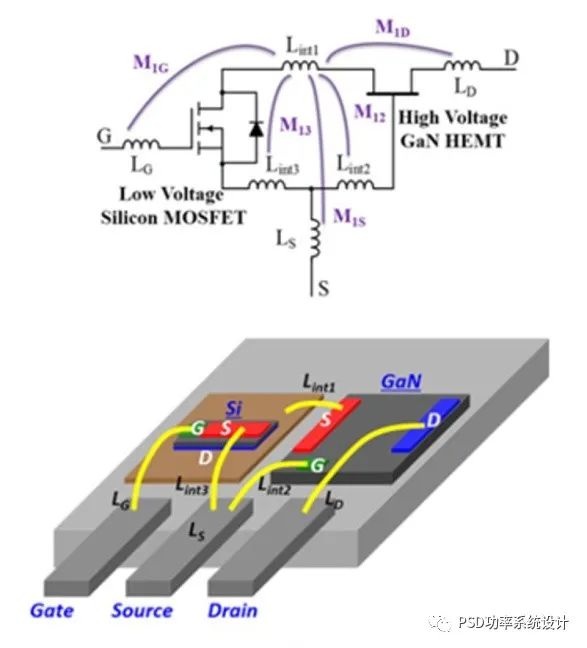

共源共栅GaN:这种方法通过将一个自然“关闭”的低电压、低RDSon硅MOSFET与耗尽型GaN HEMT晶体管(图3)串联在一起,来创建一个叠层共源共栅。这种复合器件可以由用于硅功率器件的相同栅极驱动器驱动,但有缺点。例如,性能受到硅MOSFET反向恢复和雪崩特性的限制,无法调整其开关速度。配置为并联运行可能很困难,需要外部噪声阻尼,通常是铁氧体磁珠。

图3:GaN晶体管与共源共栅结构的硅MOSFET共封装

带共封装驱动器的耗尽模式器件:几家公司通过将耗尽模式GaN器件与定制硅驱动器共封装,使其更易于使用,该驱动器允许器件模拟传统硅功率MOSFET的特性。这使得在封装中集成过流和过温保护成为可能,节省了空间和成本。但优势是以牺牲设计灵活性为代价的,因为驱动器值无法针对特定应用进行优化。此外,外部驱动器只允许调整开关的开启时间,使并联变得困难。

单片GaN+集成驱动器:这种方法将GaN功率器件和配套驱动电路集成在同一基板上。片上驱动器可以设计为向功率晶体管的栅极提供接近理想的信号电平,同时提供一个“硅友好”接口,该接口可与大多数MOSFET驱动器器件一起工作,并减少内部寄生。虽然这简化了设计,但它需要外部无源组件来实现功能解决方案。芯片驱动简单,没有OTP/OCP或其他保护电路。和具有共同封装驱动器的器件一样,只有它们的开启上升时间可以控制,并且很难配置为并行操作。

增强模式(E-mode )GaN

E-mode GaN解决了与早期GaN基功率器件相关的许多问题。该方法基于HEMT结构,该结构形成一个电压驱动且常关的固有E-mode 器件。

分立E-mode GaN功率器件的电气特性类似于设计人员熟悉的硅MOSFET,包括:

•与许多硅MOSFET驱动器兼容。

•设计灵活性可与分立硅MOSFET媲美。

•通过调整栅极电阻(RG)可以优化转换速率(开和关)。

•易于并行操作的配置。

•类硅特性,允许使用通用技术设计和测试应用。

这些是驱动GaN器件最常用的方法。由于GaN器件的行为与硅不完全相同,因此每种方法都必须加以考虑。

GaN Systems基于这些固有特性开发了先进的E-mode 产品,其器件结构坚固,超过了AEC-Q101和JEDEC可靠性标准,并符合JC-70和FIT标准。诸如坚固的栅极结构,可接受-20 V/+10 V的输入范围,可与单极(0 V/+6 V)和双极驱动电平(-3 V/+6 V和-6 V/+6 V)一起工作,同时提供强大的操作裕度,使这些产品与许多商用驱动IC兼容,这些IC用于电桥中基于MOSFET的设计,电源转换器和其他电源应用。

尽管现代E-mode GaN器件的使用要简单得多,但它们有几个不同于硅器件的独特特性:

•QG低于同类硅器件,提供更低的驱动损耗和更快的开关速度。

•通常需要+5 V/+6 V栅极偏置才能开启的功率晶体管具有更高的增益和更低的VGS。

•较低的栅极阈值电压VG(th),通常为1.5 V。

驱动E-mode GaN晶体管

看看E-mode GaN器件在选择和微调用于实际应用的栅极驱动电路方面的独特特性的实际意义。E-mode GaN设备驱动程序的主要设计目标:

•为开关提供正确的开启/关闭波形以及所需的电压(RDS(on)和IDS(max)是VGS的函数)。

•通过以下方式最大化切换性能:

o为GaN FET提供可靠、干净的开关波形。

o提供干净的栅极源和汇电流(IGS)。.

•控制功率器件的转换速率以降低EMC(GaN FET的di/dt,dv/dt可以通过改变RG 来控制)。

•实现精确的死区时间控制,将开关损耗降至最低。

•驱动电压注意事项。

GaN Systems E-mode晶体管可以使用仅正极VGS驱动器运行,该驱动器可提供VGS(OFF) = 0 V/VGS(on) = 6 V,这使它们成为低压或低功率应用的理想选择,或者在死区时间损耗最小化至关重要的场合。

当优先考虑高抗噪性和降低开关损耗时,首选提供VGS(OFF)的驱动配置。可以使用对称的+/-6 V或+6 V/-3 V驱动输入。

利用负驱动电压的影响进行系统权衡

应用负VDR(OFF)可降低关闭E型GaN晶体管所需的能量,随着工作电流的增加,这一点变得更加明显。非负驱动信号可用于低功率应用,而不会产生显著的开关损耗,但在大电流应用中,使用负VDR(OFF)关闭栅极变得至关重要。应用负VDR(OFF)可以在更高功率下提高功率级的效率,但必须与精确的死区时间控制结合使用,以实现最佳的系统效率。

GaN器件中死区时间损耗的管理

GaN HEMT没有体二极管。该器件的反向传导压降与VGS(OFF)成比例增加。在死区时间内,2DEG的行为就像一个二极管,VF = VTH(GD)+ VGS(OFF)+ ISD* RSD(ON)。

这些现象导致死区时间损失随着VGS(OFF)的增加而增加。如果驱动信号的死区时间低于某个阈值,设备在部分开关时间内不会处于零伏,开关电路电容器中的能量将在通道中消散。

随着零电压开关(ZVS)周期的缩短,器件的损耗急剧增加。因此,设计者必须推导出足够长的死区时间来防止零电压开关损耗,足够短的死区时间来保持GaN器件的高效运行。

带外部RG的开关速度控制

GaN器件的开关速度非常快,其输出波形(dv/dt)的急剧上升和下降边缘会产生不必要的高振幅谐波,从而产生EMI问题。与MOSFET一样,E-mode GaN晶体管的开关速度(on和off)可以通过调整与器件栅极(RG)串联的电阻来控制。这项技术对系统EMC优化很有价值。其他GaN实现,如集成驱动器和共源共栅配置,隔离了该栅极,从而将RG开关速度控制限制在循环的开启部分,或使其不可能。

并联的栅极驱动考虑因素

GaN Systems E-mode器件的并联操作非常简单,但必须通过添加分布式栅极电阻器(R3/R5=1-2Ω)和源极电阻器(R6/R7=1-2Ω)来防止并联器件的栅极之间的相互作用或栅极振铃。

这些指导原则在一个实验中得到了验证,其中四个GaN Systems GS6651T器件以并联配置运行,四个并联GS6651T在桥接电路的另一侧以自由轮模式运行。

对于这些测试,栅极电阻设置为RG_ON=4.55 Ω, RG_OFF = 1.25 Ω。测试电路的电源电压(VBUS)为400 V,栅极驱动输入(VGS) = +6.8 V/-5 V。当电路从空闲状态硬切换到全额定电流测量驱动电流时,产生了干净的波形(IDS_ON=231 A, IDS_OFF=240 A with ~200 V VDS margin)。

结论

E-mode GaN晶体管具有高效率和高性能,以及对硅友好的电气特性,使得使用许多与基于MOSFET的设计相同的驱动器,可以很容易地将它们整合到各种应用中。

审核编辑:汤梓红

-

德州仪器:GaN器件的直接驱动配置2020-08-04 2309

-

GaN转变充电器设计方案详解2021-04-07 4861

-

求告知LED驱动电源的设计方案2016-08-11 3584

-

未找到GaN器件2019-01-17 3021

-

基于GaN的开关器件2019-06-21 3603

-

GaN HEMT在电机设计中有以下优点2019-07-16 3328

-

直接驱动GaN晶体管的优点2020-10-27 1753

-

压电马达的驱动设计方案2021-03-04 2166

-

直接驱动GaN器件可实现更高的开关电源效率和更佳的系统级可靠性2023-02-14 1080

-

GaN器件在Class D上的应用优势2023-06-25 2443

-

TILED驱动设计方案详细资料2018-04-13 1257

-

基于GaN器件的驱动设计方案2019-11-18 6889

-

集成汽车 GaN 功率器件2022-08-03 1436

-

GaN驱动技术手册免费下载 氮化镓半导体功率器件门极驱动电路设计方案2025-03-13 55966

-

“芯”品发布 | 高可靠GaN专用驱动器,便捷GaN电源设计2025-11-11 1131

全部0条评论

快来发表一下你的评论吧 !