芯片制造的光刻支出如何随着各种节点缩小演变历程

制造/封装

描述

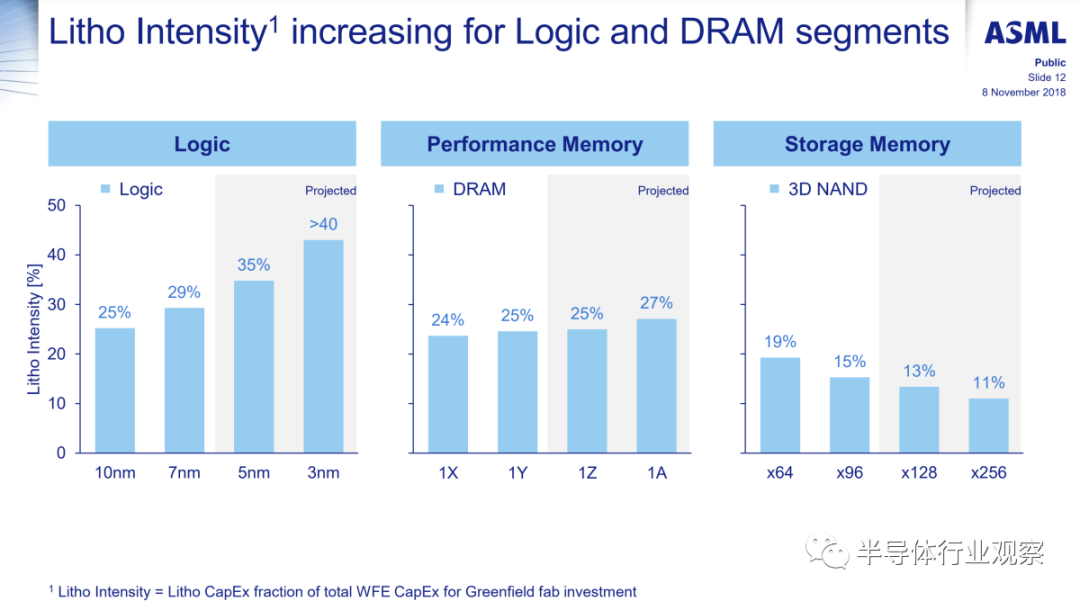

据semianalysis报道,他们正在密切跟踪的一个项目是光刻支出如何随着各种节点缩小而演变。这项研究最初是从28nm开始,然后从第一代 FinFET 节点发展到第一个 EUV 节点,再到第一个 Gate All Around Nanosheet 节点(3nm 和 2nm)。根据检查的节点,光刻花费的百分比有很大不同。下图是关于该主题的旧 ASML 幻灯片。它似乎排除了许多不同的晶圆厂资本支出,但看起来很有趣。

光刻支出与沉积与蚀刻的演变对 ASML、Lam Research、Applied Materials、Tokyo Electron 等公司的相对表现有很大影响。在我们解决这个问题时,最重要的一个方面是每个 DUV 或 EUV 层的曝光量的单位成本,以及它们的数量。顺便说一句,一些卖方分析师试图将每个节点的 EUV 曝光数量计算到他们的 ASML 模型中,这完全是错误的。

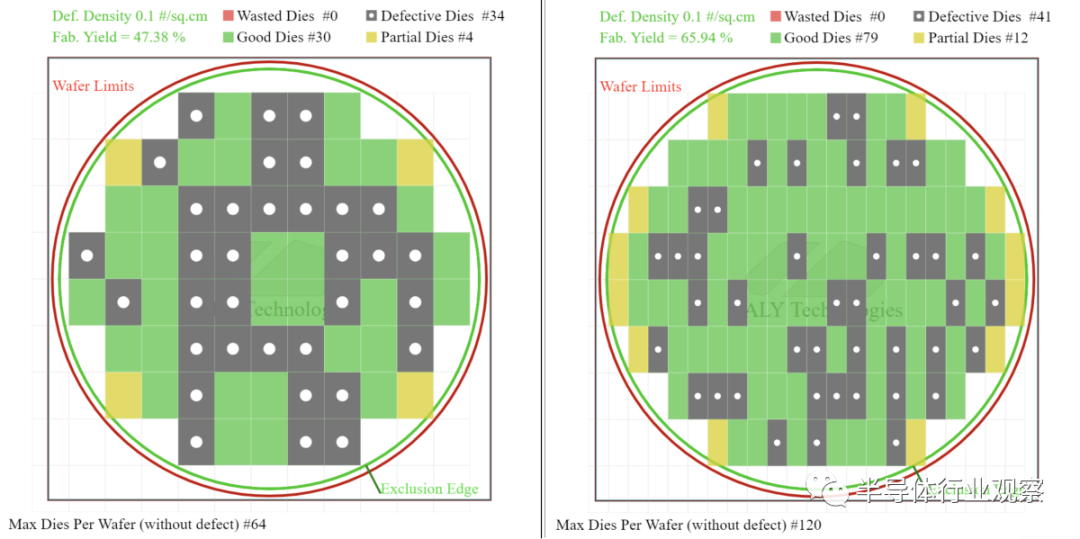

传统观点认为,更大的dies成本会成倍增加。我们认为我们所有的读者都知道这一点。较大的die尺寸会增加成本,因为缺陷更有可能影响较大的die。这是小芯片革命背后的主要驱动之一。

这种传统的思维过程可能是完全错误的。让我们使用一个带有图片的假设示例来解释为何有时候较小的die制造成本更高。假设一个无晶圆厂芯片设计团队正在决定是制作单个大型单片芯片还是 2 个小芯片 MCM 设计。左边是一个25 毫米 x 32 毫米、800 平方毫米的晶圆。右边是一个 13.5 毫米 x 32 毫米、432 平方毫米的裸片晶圆。2 个小芯片设计中每个小芯片的硅片数量只会增加 8%,这与 AMD 使用其当前小芯片 CPU 所经历的开销相似。尽管两个节点已被模拟为具有相同的每 cm 2 (0.1)缺陷数,但两种设计之间的无缺陷裸片数量差异很大。

单片设计每个晶圆有 30 个好的die,而小芯片 MCM 设计每个晶圆有 79 个好的die。假设所有有缺陷的die都必须扔进垃圾桶。如果没有芯片良率收获,单片设计的设计公司每片晶圆只能卖30个产品,而chiplet MCM设计可以卖39.5个。

通过使用小芯片和 MCM,每个晶圆的产品数量增加了约 30%。如果假设每个晶圆的成本为 17,000 美元,那么单片无缺陷硅片的成本为 567 美元,而小芯片 MCM 每个无缺陷硅片的成本为 215 美元,两个则为 430 美元。显然,如果我们设计团队应该选择小芯片 MCM 选项忽略任何功耗、芯片收获和包装成本差异,因为它们可以为每件产品节省 136 美元!

如果我们告诉你这个小芯片 MCM 设计更贵怎么办?

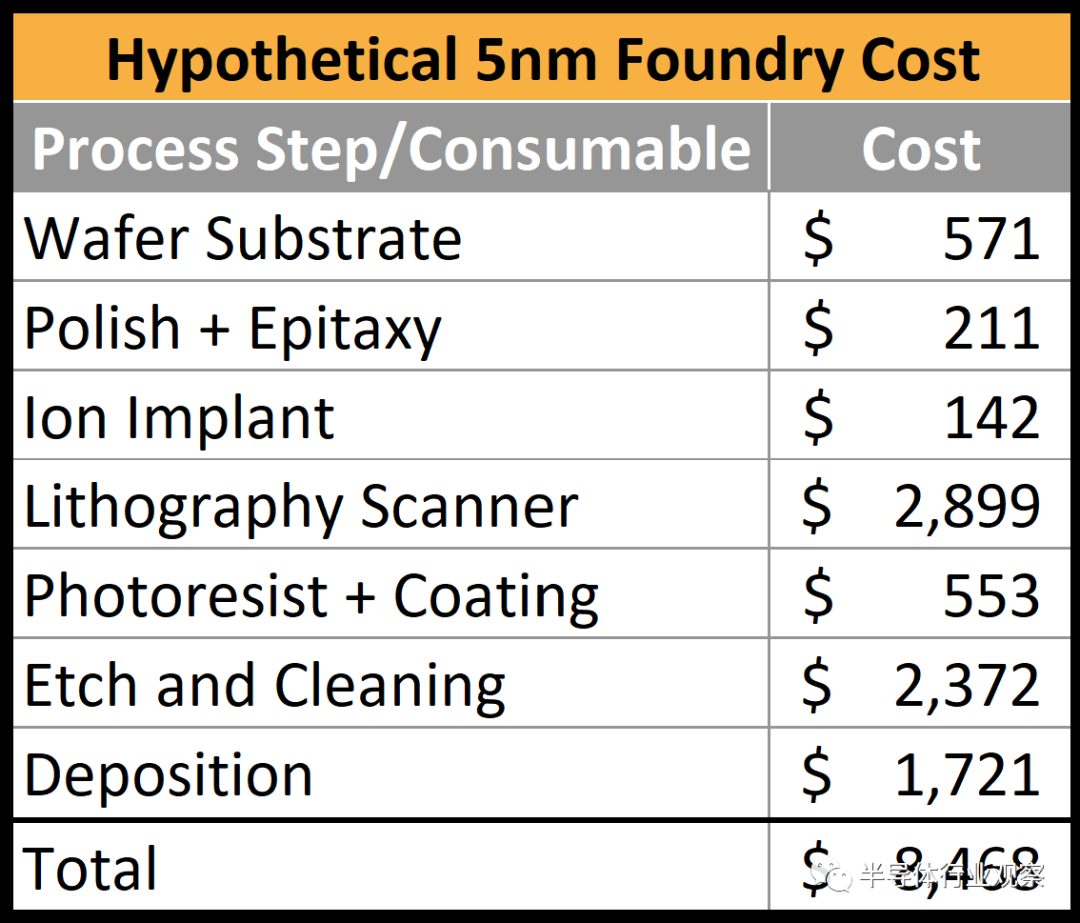

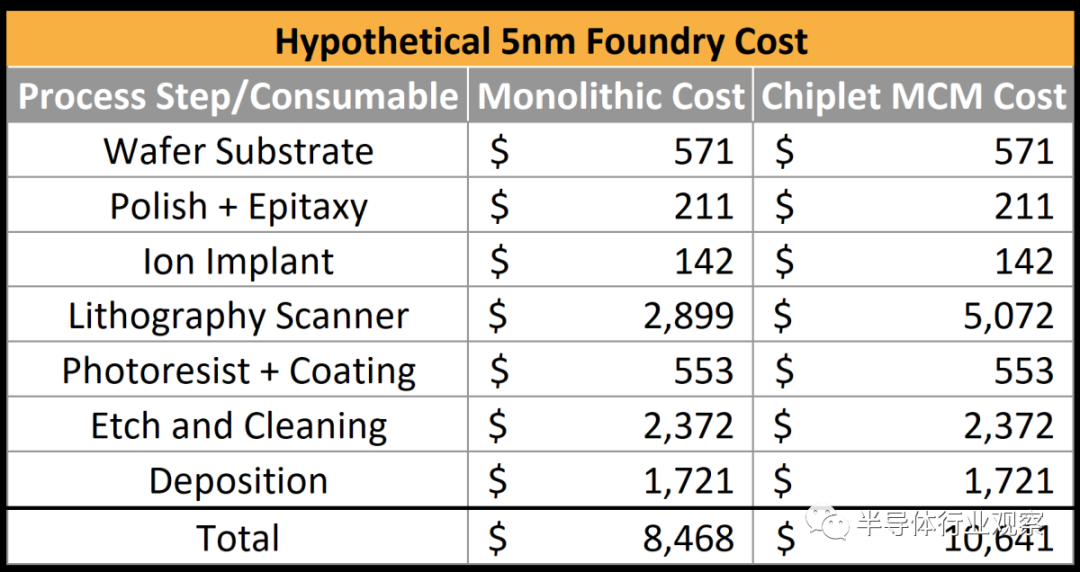

你可能不会相信我们,但让我们来看看如何。在这个假设场景中,假设产品使用代工 5nm 级节点。假设这家代工厂以约 17,000 美元的价格出售这些晶圆,毛利率约为 50%。以下是按消耗品或工艺步骤划分的成本细分,包括工具折旧、维护成本、电力使用、员工成本分配等。

这些数字与我们的实际估计相差甚远,但一致的是最大的成本中心是光刻——接近加工晶圆成本的近1/3。光刻成本只是一个平均假设。根据您选择的裸片尺寸,它可能会有很大差异。

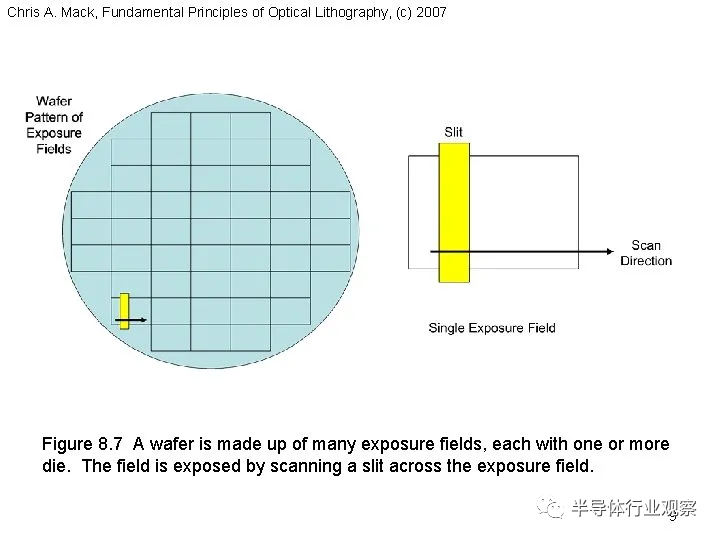

光刻工具不加选择地暴露硅片。它需要知道在哪里用光刻曝光,在哪里不曝光。光掩模是包含芯片设计并阻挡光线或允许光线通过以暴露硅片的东西。领先的 5nm 代工设计将有十几个 EUV 光掩模和另外几十个 DUV 光掩模。这些光掩模中的每一个都对应于晶圆上的一个特征或特征的一部分,并且对于每个芯片设计都是唯一的。通过光刻和所有其他工艺步骤的循环,这家代工厂可以在大约 10 周的时间内在晶圆上制造出特定的 5nm 芯片。下面是一张 DUV 光掩模的图片。

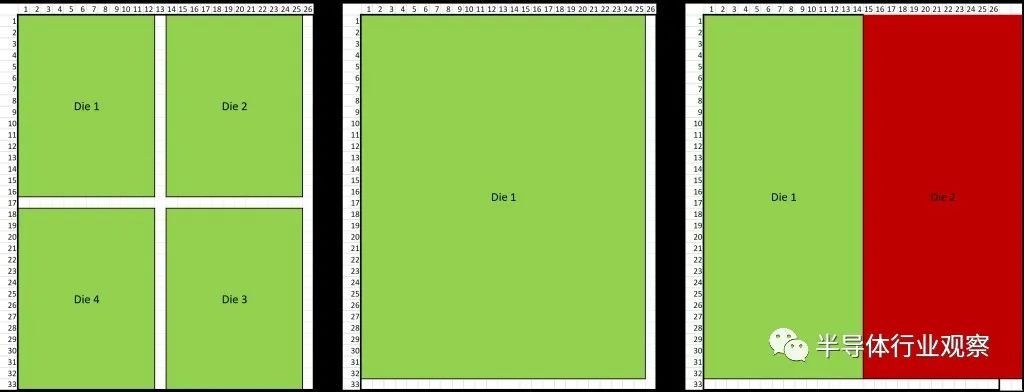

标准光掩模为 104 毫米 x 132 毫米。然后,光刻工具通过光掩模曝光,以 4 倍放大率在晶圆上打印特征。该区域为 26 毫米 x 33 毫米。大多数设计不能与 26 毫米 x 33 毫米完美对齐。

为了更好地计算,我们引入了标线(reticle)利用率的概念。

通常,芯片设计较小,因此光掩模可以包含多个与上图相同的设计。即使这样,大多数设计也不能完美地适应 26mm x 33m 的场,因此通常该光掩模的一部分也没有曝光。

如果一个die是 12 毫米 x 16 毫米,我们可以在每个标线片上安装 4 个die。这里的标线利用率非常高,因为只有一小部分标线没有暴露。对于 25mm x 32mm 的单片芯片,我们在狭缝和扫描方向上不使用 1mm。那个标线的利用率同样很高。对于我们的小芯片,它是 13.5 毫米 x 32 毫米。该die太大,无法在标线板上并排放置 2 个die,因此每个标线板只能有 1 个die。下图显示了上述示例的一些可视化。

你可能会问,标线利用率低有什么问题?

这成为一个巨大的成本问题,因为当我们缩小到晶圆级的处理过程时会发生什么。放置在光刻工具和工具中的硅片一次暴露硅片标线区域的一部分。如果使用完整的 26mm x 33mm 掩模版,则光刻工具以最少的步数跨过 300mm 硅片,12 个掩模版区域宽和 10 个掩模版区域高。如果分划板利用率较低,则工具必须在每个方向上越过和越过晶片更多次。

将每个晶圆上的 25mm x 32mm 单片芯片与 13.5mm x 32mm 小芯片 MCM 设计进行比较时,我们需要将晶圆跨过 1.875 倍!

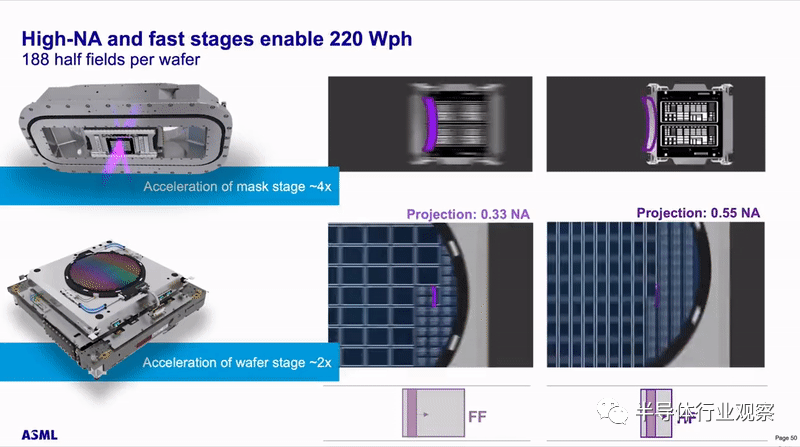

现代 DUV 和 EUV 工具具有狭缝(slit)和扫描(scan)功能。狭缝(26 毫米)是暴露出来的,它扫描(33 毫米)穿过十字线区域。下面这张Andreas Schilling分享的来自 ASML 的关于 High-NA EUV 的 gif 展示了这个概念。使用 High-NA EUV,狭缝最大仍为 26mm,扫描减半。生产力的主要损失是晶圆台必须移动的速度。

想象一下,如果相反,狭缝减半。吞吐量影响会大得多。 在比较我们的单片设计与小芯片 MCM 设计时,我们的光刻工具时间显着增加,因为晶圆必须扫描 1.875 倍。这是因为狭缝的很大一部分没有得到充分利用。虽然在晶圆加载时间方面仍有一些效率,但光刻工具的大部分成本是扫描时间。因此,每片晶圆的内部成本显着上升。

在这种假设情况下,代工厂现在每片晶圆的光刻成本要多花 2,174 美元。这是一个巨大的成本增加,代工厂不会为已经有非常紧张的利润交易的大批量客户忍受。假设代工厂按利润率定价,因此无论设计如何,都能保持 50% 的毛利率。

未充分利用分划板上的狭缝导致的成本增加意味着代工厂不会以 17,000 美元的价格出售这些晶圆来维持 50.2% 的毛利率。相反,他们将以 21,364 美元的价格出售这些晶圆。单片产品的无缺陷硅成本仍为 567 美元。每个裸片的无缺陷硅成本不是 215 美元,而是 270 美元。每件产品不再是 430 美元,而是 541 美元。

小芯片与单片的决定现在变得更加困难。一旦考虑到封装成本,单片芯片的制造成本很可能会更便宜。此外,小芯片设计存在一些电力成本。在这种情况下,构建一个大型单片芯片绝对比使用chiplet/MCM 更好。

此示例是选择用于演示标线利用率点的最坏情况。这种简单化和假设性的分析还有很多警告。此外,与其他工艺步骤相比,5nm 之前以及我们进入栅极之后的大多数其他工艺节点都具有较低的光刻成本。大多数小芯片架构可能会提高而不是降低标线利用率。

编辑:黄飞

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3359

-

【「芯片通识课:一本书读懂芯片技术」阅读体验】芯片怎样制造2025-04-02 4030

-

光刻胶在集成电路制造中的应用2018-08-23 7421

-

光刻机工艺的原理及设备2020-07-07 17525

-

魂迁光刻,梦绕芯片,中芯国际终获ASML大型光刻机 精选资料分享2021-07-29 70632

-

指纹识别传感器技术的演变历程2019-05-11 3873

-

未来极紫外光刻技术将如何发展?产业格局如何演变?2021-02-01 3821

-

未来科技量子芯片无需用使用光刻机?制造芯片难还是问题吗?2021-08-27 38819

-

芯片制造公司光刻机的情况2021-12-30 5327

-

光刻支出对芯片行业的影响2022-06-21 2461

-

宇微光学成功研发计算光刻EDA软件2022-11-28 1878

-

芯片制造光刻步骤详解2023-06-08 7543

-

各种光刻技术你都了解吗?2023-10-13 3596

-

光刻机的工作原理和分类2024-11-24 8747

-

芯片制造:光刻工艺原理与流程2025-01-28 4743

全部0条评论

快来发表一下你的评论吧 !