终端区域对开关损耗的物理分析

电子说

描述

尽管硅是电子产品中使用最广泛的半导体,但最近的研究表明它有一些局限性,特别是在高功率应用中。带隙是基于半导体的电路的一个相关因素,因为高带隙在高温、电压和频率下的操作方面具有优势。虽然硅的带隙为 1.12 eV,但碳化硅的带隙值是 3.2 eV 的 3 倍,从而在更高的开关频率以及更小的整体占位面积下实现更好的性能和效率。

SiC MOSFET具有显着的特性和单极传导机制,可减小尺寸并提高开关性能。此外,当具有相同的电流和电压额定值时,SIC MOSFET 的尺寸可以比 Si 对应物更小,正如 Huang 的品质因数1中所推测的那样。由于尺寸更小,整体寄生电容更小,这使得 SiC MOSFET 能够实现高开关速度和低导通电阻。因此,基于 SiC 的转换器在混合动力/电动汽车、太阳能逆变器和不间断电源中具有巨大的应用潜力。

先前的研究表明,SiC 芯片尺寸的显着减小仅考虑有源区域。由于位于有源区边界的边缘电场,封闭有源区并有助于成功实现近乎理想的雪崩击穿的终止区不能按比例缩放。一组研究人员开展了分析从端接区域引入的寄生电容以及它如何影响 SiC MOSFET 的开关损耗的工作。2该研究得到了国家自然科学基金的部分支持,部分得到了宽带隙半导体电力电子器件国家重点实验室的支持。

分析终端区域中的 SiC MOSFET

在题为“端接区域对 SiC MOSFET 的开关损耗的影响”的论文中,研究人员分析了端接区域对寄生电容的影响。简单来说,寄生电容是电子元件或电路的各部分之间由于彼此接近而存在的一种不可避免但不受欢迎的电容。

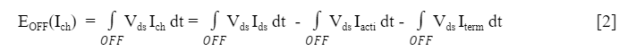

图 1:半电池节距和端接区域的横截面图

输入电容、输出电容和反向传输电容都取决于 SiC MOSFET 的所有三个端子之间的电容。由于栅极总线和源极之间存在物理重叠,因此栅极下方的氧化层比栅极氧化层厚。由于栅极和漏极以及栅极和源极端之间没有重叠,它们对总电容的贡献很小。因此,漏源端电容由有源区和终端区的等效电容组成。

该团队使用 TCAD Sentaurus 演示了 SiC MOSFET 开启和关闭事件期间寄生电容的工作原理。TCAD Sentaurus 是一种先进的多维模拟器,能够模拟硅基器件的电学、热学和光学特性,用于开发和优化半导体工艺技术。器件两端的电压 (V ds ) 和流经器件的电流 (I ds ) 重叠会导致开关损耗。为了说明 SiC MOSFET 内部的开关过程,通道电流 (I ch ) 通过栅极通道引入。

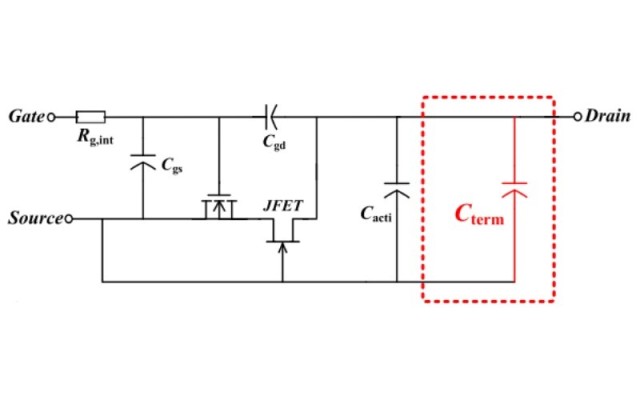

图 2:考虑端接区域的寄生电容电路图

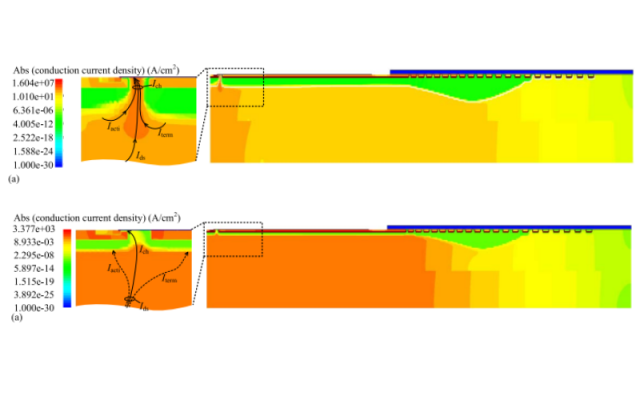

在导通过程的米勒间隔期间,栅漏电容 (C gd ) 和有源区电容 (C acti ) 由于来自终端引入的电容的放电电流 (I term ) 的电阻流动而放电区(C term)通过位于有源区的栅极沟道。在此区间内流过栅极沟道的耗散电流或沟道电流 (I ch ) 是流过终端区的电流 (I term ) 与有源区电容 (I acti ) 和漏极的放电电流的组合源电流 (I ds )。

而对于关断过程的米勒间隔,一部分漏源电流 (I ds ) 开始对引入到有源区和终端区的电容 (C acti和 C term ) 充电,而不是流过栅极沟道),如下图所示。这里,耗散沟道电流 (I ch ) 不包括 C term和 C acti的电流(即I ch = I ds – I acti – I term)。

图 3:开启(上)和关断(下)工艺的米勒平台选择期间 SiC MOSFET 端接区域的示意图和等效电路

SiC MOSFET 的开关损耗建模

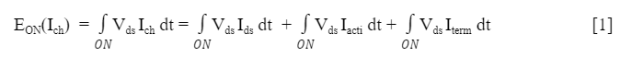

在终端区域的物理分析过程中,流过 SiC MOSFET 栅极沟道的沟道电流 (I ch ) 是展示开关损耗但不可测量的漏源电流 (I ds ) 的基本电流。因此,考虑终端区域的开启和关闭损耗表达式为:

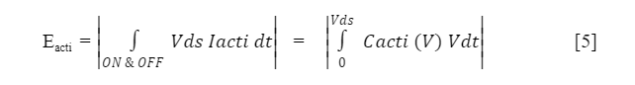

将上述关断和开通损耗公式组合后,定义如下公式:

等式 3 和 4 表示在开启和关闭米勒过程期间可测量 I ds的开关损耗贡献。等式 5 和 6 描述了 C acti和 C term的充电和放电。对于给定的器件,存储在有源区和终端区的寄生电容中的能量固定在相同的阻断电压下,但与 I ds无关。

结果

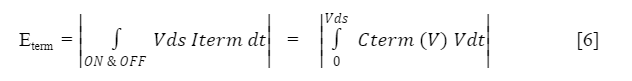

图 4:SiC MOSFET 分离的开关电路图

如图 4 所示,建立了一个双脉冲测试,其中 SiC MOSFET 在有源区和终端区分开,以检查开关损耗的组成。SiC MOSFET 的额定电流为 1、3 和 6 A,定义为V ds = 3 V 和V gs = 20 V。使用 TCAD Sentaurus 仿真,计算的开关损耗击穿为 1-、3-、下图显示了 800、1,000 和 1,200 V 以下的 6-A SiC MOSFET。

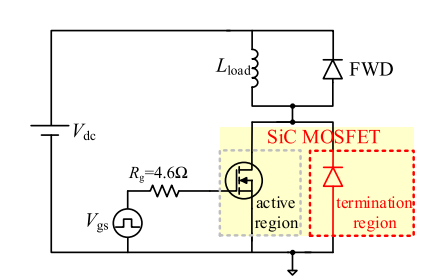

图 5:不同 MOSFET 的开关损耗细分

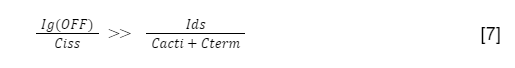

开关损耗分为 E ON (I ds )、E acti、E term和 E OFF (I ch )。E ON (I ds )、E acti和 E term的值是可比较的,而 E OFF (I ch ) 在各种阻断电压和电流额定值下变得非常低。随着用于更高额定电流的有源区面积的增加,E acti增加了总开关损耗的比例。如果使用相对较弱的栅极驱动器,则 E ON (I ds ) 和 E OFF (Ich ) 会更大。另一方面,对于特定的 MOSFET ,E acti和 E term是固定的。对于 SiC MOSFET 的 E OFF,很少有电流流过栅极沟道,产生很少的焦耳热,但几乎所有电流都将 C acti和 C项充电为位移电流。这导致较低的 E OFF (I ch ) 值。可以表示如下:

其中 I g(OFF)是关断过程中栅极回路的放电电流,表明关断持续时间比 C acti和 C term快得多。

结论

使用 TCAD Sentaurus 和考虑了端接区域影响的开关损耗模型模拟了对 SiC MOSFET 端接区域的物理洞察。经证实,终端区域对开关损耗的影响不容忽视,尤其是对于低电流额定值的 SiC MOSFET。开通损耗的重要部分之一是 E term和 E acti,这是一种固有损耗,甚至高于常用的电测量估计。

审核编辑:汤梓红

-

使用Cauer网络仿真热行为与对开关损耗影响的评估2023-12-29 3168

-

集成高侧MOSFET中的开关损耗分析2022-11-16 781

-

PFC MOSFET的开关损耗测试方案2022-10-19 2937

-

开关损耗包括哪几种2021-10-29 2456

-

开关损耗原理分析2021-10-22 1584

-

基于航迹数据的机场终端区进场效率分析2021-07-05 827

-

功率MOSFET的开关损耗分析2021-04-16 1586

-

如何更加深入理解MOSFET开关损耗?2021-04-07 3483

-

【干货】MOSFET开关损耗分析与计算2021-01-30 5493

-

如何准确的测量开关损耗2019-06-27 3291

-

全SiC功率模块的开关损耗2018-11-27 4776

-

基于CMM下开关损耗和反激开关损耗分析以及公式计算2018-01-13 11032

-

功率MOSFET的开关损耗:关断损耗2017-03-06 7345

-

MOSFET开关损耗分析2016-01-04 994

全部0条评论

快来发表一下你的评论吧 !