基于p型V-WSe2和n型MoS2的可编程FET的异质集成

描述

研究背景

CMOS技术是无数现代电子产品、仪器和计算工具的大脑。60多年来,CMOS技术在性能、能效和单位功能成本方面持续增长,这得益于遵循摩尔定律的硅基MOSFET的不断扩展。虽然仍在全力以赴,但硅基CMOS已开始显示出未来技术节点出现问题的早期迹象。前面有两个主要的技术障碍:1)对于亚10 nm节点,必须积极减小沟道厚度以保持栅极静电,从而保持理想的器件性能。硅和其他块材半导体由于有害的量子限制效应和沟道-电介质界面处电荷载流子的散射增加而容易受到厚度缩放的影响,从而导致迁移率严重下降。2)算术核心或逻辑单元与数据存储或内存单元的物理分离,这是冯诺依曼架构所要求的,限制了CMOS处理器在计算和数据密集型应用中的能效。第一个问题的解决方案是超薄通道材料的创新。第二个问题的解决方案是非冯诺依曼架构,其中消除了逻辑和内存之间的物理分离。

成果介绍

有鉴于此,近日,美国宾夕法尼亚州立大学Saptarshi Das教授团队首次报道了大面积生长的n型MoS2和p型钒掺杂WSe2 FET的异质集成,具有非易失性和模拟存储器存储能力,可以实现非冯诺依曼2D CMOS平台。这种制造工艺流程允许精确定位n型和p型FET,这对于任何IC开发都至关重要。本文还演示了使用这种非冯诺依曼2D CMOS平台的反相器和简化的2输入1输出多路复用器和神经形态计算原语,例如高斯、sigmoid和tanh激活函数。该演示展示了晶圆级2D材料异质集成的可行性。文章以“Heterogeneous Integration of Atomically Thin Semiconductors for Non-von Neumann CMOS”为题发表在著名期刊Small上。

图文导读

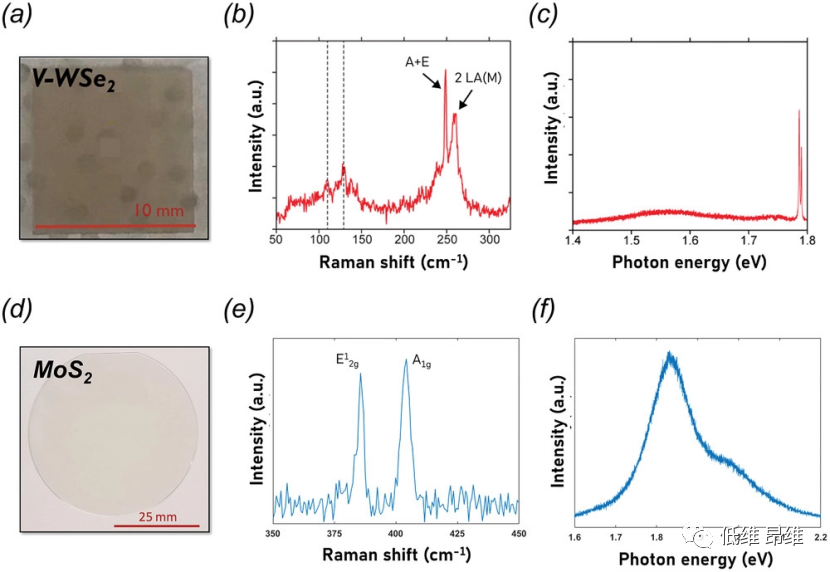

图1. 大面积p型V-WSe2和n型MoS2。(a)在c面蓝宝石衬底上MOCVD生长和完全聚结的单层V-WSe2的光学图像。(b&c)V-WSe2的拉曼光谱和光致发光光谱。(d)在c面蓝宝石衬底上MOCVD生长和完全聚结的单层MoS2的光学图像。(e&f)MoS2的拉曼光谱和光致发光光谱。

V-WSe2薄膜在定制的冷壁MOCVD反应器中沉积在10 mm×10 mm的c面蓝宝石衬底上。W(CO)6、H2Se和V(C5H5)2分别用作金属、硫族元素和掺杂剂前驱体,H2作为载气。MOCVD合成使用三步生长方法进行,其中掺杂剂与金属前驱体在生长的所有阶段同时引入反应室。图1a显示了生长衬底上完全聚结的单层V-WSe2的光学图像。图1b所示的拉曼光谱显示缺陷激活的ZA(M)和LA(M)模式的强度分别在129.2和109.9 cm-1处增加,同时WSe2的A+E模式在248.7 cm-1处增加,这是故意引入杂质引起V-WSe2晶格扰动的直接证据。此外,如图1c所示,PL信号由于正三重子的非辐射复合而完全猝灭,其中由于薄膜中的空穴数量增加,预计其密度会增加。类似地,通过MOCVD将单层MoS2沉积在外延2英寸c面蓝宝石衬底上。图1d显示了生长衬底上完全聚结的单层MoS2的光学图像。图1e给出了单层MoS2的拉曼光谱,在383和404 cm-1处有两个特征峰,分别对应于面内E2g1和面外A1g模式,预期的单层峰分离约为19 cm-1。图1f显示了峰值为1.83 eV的PL光谱,证实了单层MoS2。

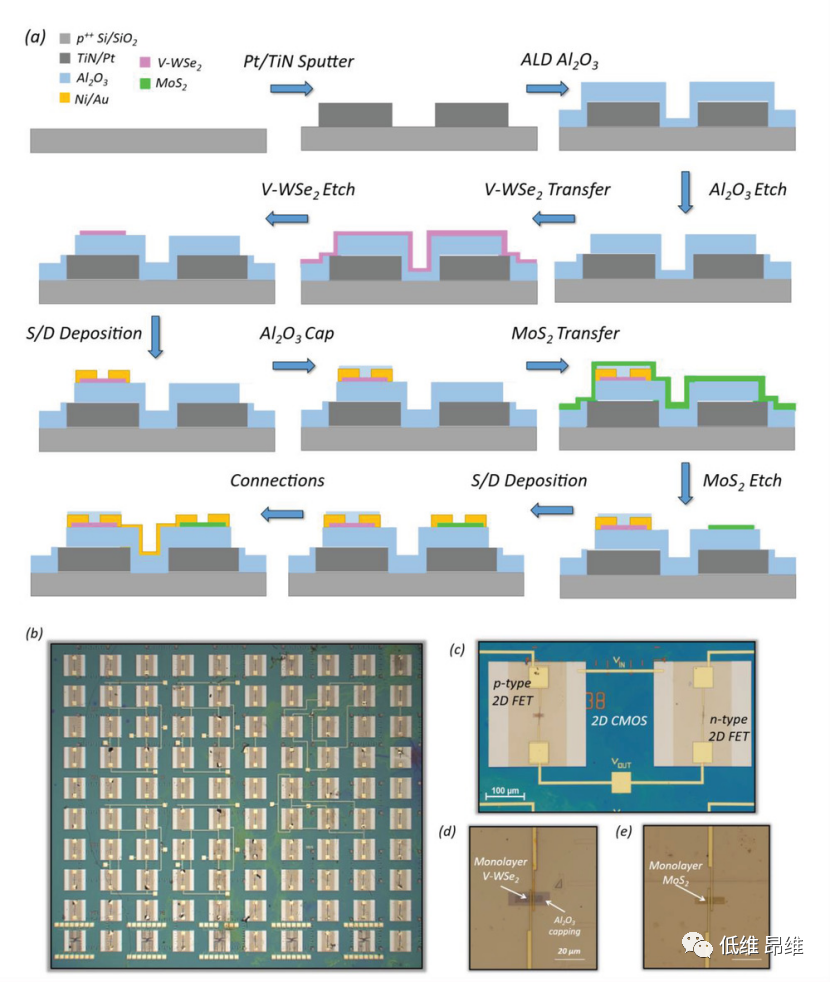

图2. p型V-WSe2和n型MoS2的集成。(a)使用n型MoS2和p型V-WSe2实现2D CMOS基集成电路的制造工艺流程。(b)显示芯片布局的代表性光学图像。(c)2D CMOS反相器。(d)具有Al2O3覆盖层的单层V-WSe2 FET的光学图像,可保护底层材料免受后续制造步骤的影响。(e)单层MoS2 FET的光学图像。

图2a总结了整个制造工艺流程,允许在SiO2/p++-Si衬底上精确定位单独栅控的p型和n型2D FET。第一步是制造局部背栅岛。为此,采用电子束光刻技术定义250 µm×250 µm正方形,然后溅射20 nm TiN和50 nm Pt。选择Pt作为背栅接触是因为它的功函数大。沉积TiN层来促进Pt和SiO2之间的粘附。在背栅接触放置之后,使用ALD沉积50 nm Al2O3作为背栅氧化物。然后使用光学光刻来定义可以访问Pt栅电极的区域,然后使用BCl3气体进行反应离子刻蚀(RIE)步骤以刻蚀暴露的氧化铝。刻蚀在20 s四个循环中完成,以避免衬底加热效应。在制造Al2O3/Pt/TiN背栅岛堆叠后,使用PMMA辅助的湿法转移技术将V-WSe2从生长衬底转移到岛衬底。然后RIE使用SF6气体在5 ℃下30 s,用于分离5 µm×20 µm的V-WSe2条带。这些分离的V-WSe2薄膜位于岛的顶部,需要用作p型FET。通过这种方式,p型FET可以在衬底的任何位置制造,从而允许设计任何复杂的CMOS电路。最后,通过电子束蒸发40 nm Ni/30 nm Au接触完成p型FET制造。所有p型V-WSe2 FET的沟道长度和宽度分别设计为1和5 µm。接下来,进行另一个电子束光刻步骤,然后进行30 nm Al2O3蒸发以封装所有p型FET,保护它们免受后续制造步骤的影响。然后使用相同的湿法转移技术将MOCVD MoS2薄膜转移到衬底上。然后重复用于制造p型FET的相同制造步骤,在所需的岛上制造MoS2基n型FET。所有n型MoS2 FET的沟道长度和宽度也分别设计为1和5 µm。最后,p型FET和n型FET之间的必要电路连接是通过使用电子束光刻定义7 µm宽的线,然后使用电子束沉积蒸发60 nm Ni/30 nm Au来实现的。图2b-d分别显示了完全制造的2D CMOS芯片、代表性电路以及单独n型MoS2和p型V-WSe2 FET的光学图像。

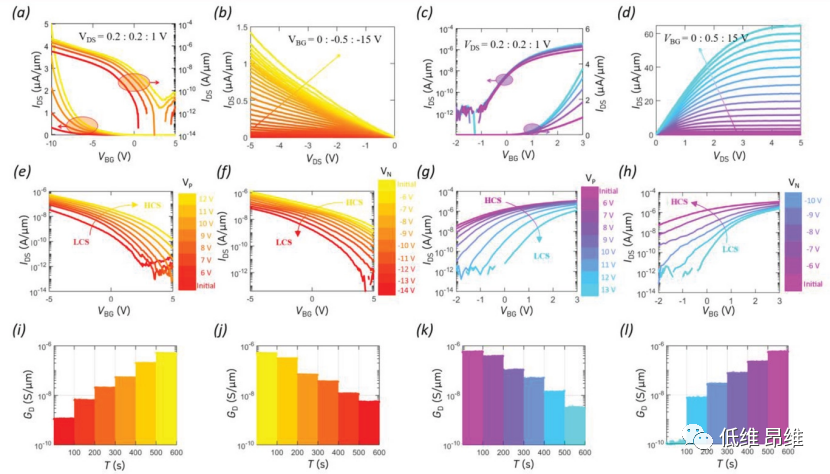

图3. 非冯诺依曼2D CMOS的电学表征。(a&b)基于单层V-WSe2的代表性p型FET的转移和输出特性。(c&d)基于单层MoS2的代表性n型FET的转移和输出特性。(e&f)使用不同幅度的大正(VP)和大负(VN)电压脉冲对V-WSe2 FET进行编程。(g&h)使用不同幅度的大正(VP)和大负(VN)电压脉冲对MoS2 FET进行编程。(i&j)V-WSe2 FET的编程后和擦除后电导状态的非易失性保留。(k&l)MoS2 FET的编程后和擦除后电导状态的非易失性保留。

在沉积电路演示所需的连接线之前,对p型和n型FET进行了电学表征。图3a和b显示了基于V-WSe2的代表性p型FET的转移和输出特性。MoS2基n型FET的相同两个图如图3c和d所示。p型V-WSe2 FET表现出电流开/关比(rON/OFF)≈105和亚阈值斜率(SS)≈470 mV dec-1。在10 nA µm-1等电流下提取的阈值电压(VTH-p)为≈-3 V,从峰值跨导中提取的空穴场效应迁移率(μp)为≈2 cm2 V-1 s-1。在VDS=5 V时,对于≈1.5×1013 cm-2的反转载流子密度,导通电流(Ip)达到≈1.5 µA µm-1。n型MoS2 FET的rON/OFF≈107,SS≈450 mV dec-1,阈值电压(VTH-n)≈2.8 V,电子场效应迁移率(μn)≈17 cm2 V-1 s-1。在VDS=5 V时,对于≈1.5×1013 cm-2的反转载流子密度,导通电流(IOn)高达≈65 µA µm-1。与V-WSe2 FET相比,对于相似的反转电荷载流子密度,n型MoS2 FET达到更高的导通电流。这可以归因于迁移率值的差异以及Ni/MoS2界面处的低肖特基势垒(SB)高度导致接触电阻的显著差异,这从它们各自的输出特性可以看出。

上述特征的2D FET还表现出模拟编程和电导状态的非易失性保留,如图3e-h所示。这种能力可归因于电介质/2D界面处/附近的电荷俘获/去俘获现象。将高正编程电压脉冲(VP)施加到这些器件的局部背栅,将两个器件的阈值电压转移到正侧。对于大的正VP值,在给定VBG处测量的电导对于p型FET将增加,对于n型FET将减少,分别如图3e和g所示。同样,施加高负电压脉冲(VN)将导致阈值电压向负侧偏移,从而导致p型FET从高电导状态变为低电导状态,对于n型FET反之亦然,如图3f和h所示。无论编程电压脉冲的幅度和持续时间如何,发现在这些编程电导状态中的每一个的存储器保留对于两种类型的器件都是稳定的。图3i-l分别显示了p型V-WSe2和n型MoS2 FET在VBG=VR=0 V的读取电压下提取的100 s内不同编程后和擦除后电导状态(GDS)的演变。虽然传统的存储器需要多年的非易失性保留,但包括神经形态和边缘计算在内的许多内存计算应用程序放宽了对长期保留的要求,并且可以很好地满足几小时到几天的短期存储保留。尽管如此,这里的关键成就是能够在p型和n型FET中编程和存储模拟电导状态,从而首次实现非冯诺依曼CMOS。

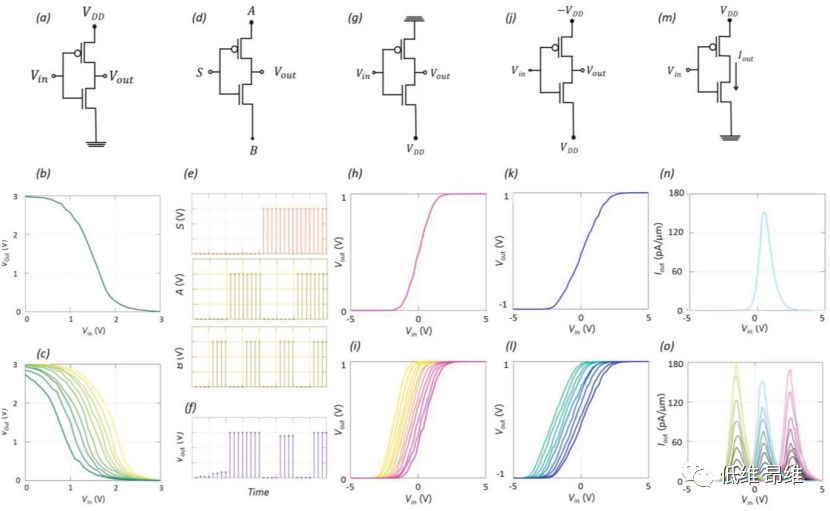

图4. 2D CMOS基内存计算原语。(a-c)2D CMOS基可编程反相器的电路原理图、输出(Vout)与输入(Vin)特性以及可重构的开关阈值(VSW)。(d-f)2×1 MUX的电路原理图,施加到选择器S和输入A和B的电压波形,以及输出电压(Vout)波形。(g-i)电路原理图、输出(Vout)与输入(Vin)特性,以及使用可编程2D CMOS实现的可重构sigmoid激活函数。(j-l)电路原理图、输出(Vout)与输入(Vin)特性,以及使用可编程2D CMOS实现的可重构双曲正切激活函数。(m-o)电路原理图、输出(Vout)与输入(Vin)特性,以及使用可编程2D CMOS实现的可重构高斯激活函数。

使用上述2D FET的非易失性编程能力,在此展示了可重构的数字和神经形态计算原语。图4a显示了2D CMOS反相器的电路原理图。反相器是IC技术中的核心逻辑元件,需要p型和n型晶体管来实现高增益。尽管已经展示了仅基于具有电阻负载的n型MoS2 FET的反相器,但这种设计存在更高的功耗和更低的噪声容限。图4b显示了反相器特性,增益≈4。虽然反相器是有用的逻辑元件,但可编程反相器对于数字和模拟电路设计都具有很高的意义。具有可编程开关阈值的反相器可以根据应用和环境要求设置电压参考电平,从而减少电路占用空间和能量消耗。图4c显示了2D CMOS反相器的开关阈值(VSW)。

图4d显示了2×1 MUX的电路原理图。MUX是一种常见的电子器件,用于选择性地在各种输入之间切换。在2×1 MUX的情况下,选择器线S可用于在两个输入A和B之间切换。通过将p型V-WSe2 FET与n型MoS2 FET串联来使用简化的MUX设计。两个器件的局部背栅短路并连接到选择器线,而输入A和B分别施加到p型FET的漏极端和n型FET的源极端。理想情况下,当S=0时,输入A应反映在输出(Vout)上,而当S=1时,Vout应为输入B。图4e显示了选择器S和输入A和B的波形,图4f显示了Vout。显然,2晶体管电路可以用作2×1 MUX,从而降低能耗和面积开销。

接下来,实现可重构的神经形态原语,例如sigmoid、双曲正切(tanh)和高斯激活函数。图4g显示了由p型V-WSe2 FET和n型MoS2 FET串联组成的电路原理图,以实现sigmoid激活功能。输入(Vin)施加于两个器件的公共背栅端,而VDD和GND分别施加到n型和p型FET的源极和漏极。图4h显示了在n型和p型FET的公共节点端处测量的输出电压(Vout)与Vin的关系,类似于sigmoid激活函数。与反相器的情况类似,sigmoid激活曲线也可以通过对p型和n型FET进行相应编程来编程为不同的阈值。测量了具有不同开关阈值的各种sigmoid曲线,如图4i所示。对于相同的sigmoid电路设计,通过在p型FET的漏极端施加-VDD,如图4j所示,得到如图4k所示的双曲正切(tanh)曲线。这里,函数从-1切换到+1。与上述情况类似,该函数也可以编程为不同的状态,如图4l所示。最后,使用图4m所示的电路设计实现高斯激活函数。当Vin值为大的正或大的负时,串联连接的两个FET中的一个关闭,防止任何电流在电路中流动。然而,随着n型MoS2 FET从关闭状态切换到开启状态,电流传导开始并随着Vin遵循亚阈值特性呈指数增加,并达到由VDD确定的峰值幅度。超过这个峰值,电流开始随着p型V-WSe2 FET的亚阈值特性呈指数下降。因此,p型V-WSe2和n型MoS2 FET的串联表现出具有指数尾的非单调传输特性,可模拟高斯分布。然而,高斯的幅度可以通过VDD来改变,而平均值可以通过对底层p型和n型FET进行编程来相应地调整。具有不同幅度和平均值的高斯曲线如图4o所示。

总结与展望

本文展示了基于p型V-WSe2和n型MoS2的可编程FET的异质集成,用于实现各种数字和神经形态计算原语。本文的研究结果是实现2D CMOS基集成电路的第一步,尽管仍有一些挑战有待缓解。例如,改进p型V-WSe2的合成可以带来更好的器件和电路性能、寿命和良率。此外,金属功函数工程可用于进一步提高n型和p型2D FET的性能。未来的工作还将通过提出材料、器件和电路级别的解决方案,专注于开发更复杂的2D CMOS电路。材料合成的优化、浮栅的开发和集成以及接触工程都是将探索实现2D TMDs超大规模集成电路(VLSI)的途径。

审核编辑:汤梓红

-

mos管怎么判断是n型还是p型2024-01-10 5504

-

HAT1089C 数据表(-20V -2A Silicon P Channel MOS FET / Power Switching)2023-07-12 484

-

HAT1095C 数据表(-12V -2A Silicon P Channel MOS FET / Power Switching)2023-03-30 590

-

N型场效应管FET是如何进行工作的?2023-03-08 1336

-

基于MoS2高密度和高性能的大规模柔性集成电路的制造挑战2022-10-12 3046

-

什么是MOS管?如何判断MOS管是N型还是P型2021-12-31 3800

-

网络型可编程控制实训装置相关资料分享2021-06-29 1158

-

USB限流开关IC,具有可编程的电流限制2021-01-26 1094

-

USB过流保护IC,可编程的限流开关2021-01-25 994

-

可编程7.8V UVLO的ADP2302降压型稳压器典型应用2019-05-07 1943

-

ADI推出可编程的抖动衰减型时钟转换器芯片2011-10-29 1215

-

FX2N可编程序控制器2010-10-02 1586

-

HG2F/3F/4F型可编程显示器2010-08-11 490

全部0条评论

快来发表一下你的评论吧 !