正确使用并联氮化镓晶体管

今日头条

描述

电源转换器的设计人员正在寻找提高效率同时增加系统功率密度的方法。宽带隙 (WBG) 技术提供了答案。由氮化镓 (GaN) 制成的晶体管作为一种解决方案正变得越来越流行,但与其硅对应物一样,单个器件在处理功率方面仍然存在限制。然而,当结合使用这些器件(GaN 晶体管)时,工程师不能简单地从硅 MOSFET 切换到 GaN 器件。

并联开关装置和最佳驱动

理想情况下,当使用并联开关时,所用器件的 R DS(on)需要紧密匹配,以确保静态电流在晶体管上均匀分布。还必须考虑动态切换期间由于不同的栅极阈值、PCB 走线阻抗等而导致的器件之间缺乏对称性。如果不这样做,可能会导致不良的高频振荡、满足 EMC 要求的挑战,甚至会损坏开关。

虽然硅 MOSFET 的并行操作是众所周知的,但对许多工程师来说,驱动单个 GaN HEMT 将是一种全新的体验。由于其出色的开关速度,在处理并行操作之前必须充分了解这一挑战。

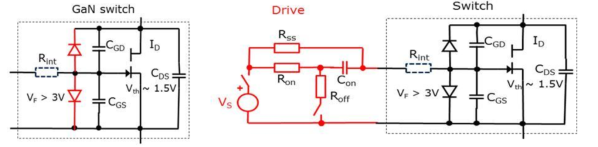

Infineon CoolGaN™ 600 V HEMT 在栅极下方使用 p 掺杂 GaN,从而产生一个正向电压约为 3.5 V 的 pn 二极管,与栅极电容 C G并联。这需要一个不同于硅 MOSFET 使用的驱动电路。二极管将栅极钳位到接近 V F的值,这意味着需要负电压才能正确关闭晶体管。稳定导通状态和关断/导通瞬态期间所需的驱动器也存在差异。

图 1 中的电路解决了这个问题。通过 R on的低阻抗快速交流通路打开器件,而 R SS决定稳态二极管电流。当关闭晶体管时,需要负栅极电压 V G。这是通过确保 C on大于 C GS 来实现的。

单栅极驱动器,例如隔离式 EiceDRIVER™ 1EDI20N12AF,是 CoolGaN HEMT 的理想伴侣。源极 (OUT+) 和漏极 (OUT-) 输出分别使用正确的电压实现晶体管的开启/关闭。这可确保不超过栅极阈值,即使在 RC 网络可能趋向于 0 V 的低占空比下,也能很好地定义V G。

交流电路径的影响

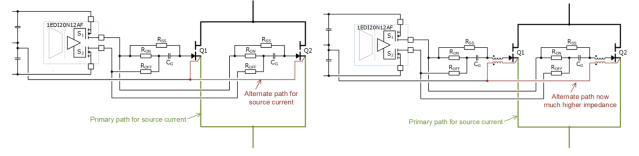

即使每个晶体管都有单独的驱动电路,栅极驱动器回路中仍然有一个共享的电流路径(图 2),因为不可避免地会有一些电流流过开尔文源。即使是微小的毫伏差异也会导致两个晶体管之间的严重振荡。

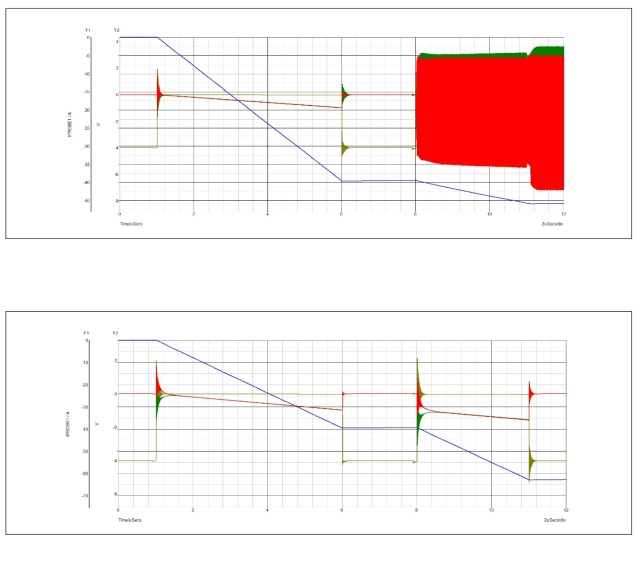

开尔文源路径中的高阻抗共模 (CM) 电感器和 1 Ω 电阻器可解决此问题。图 3 的仿真结果显示了精心设计尺寸的 CM 电感器以避免损害驱动器能力的影响。

PCB 设计的良好实践

在高频和电流下使用 GaN HEMT 时,杂散电感和电容引起问题的可能性很高,在并行操作时更是如此。然而,使用 SIMetrix 晶体管模型的模拟表明,对于小型且对称的栅极驱动回路以及使用 CM 电感器,均流中的任何静态不平衡仅与所选晶体管之间的R DS(on)差异有关。

积累实践经验

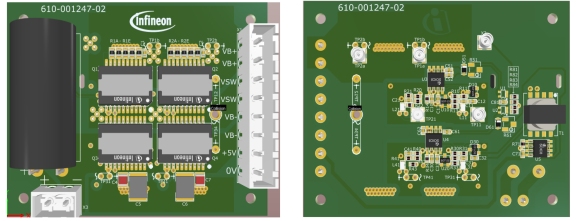

为了让工程师能够快速评估并联运行的 GaN HEMT,英飞凌开发了一款并联半桥评估板,其中包含四个 70 mΩ IGOT60R070D1。使用此处讨论的设计指南,它为深入分析提供了广泛的测试点。借助外部电感器,该板可用于降压和升压模式测试以及双脉冲测试。脉冲宽度调制 (PWM) 操作也可以用于频率高达 1 MHz 和功率级别为几千瓦的硬开关和软开关。可以测试 28 A 的连续电流和 70 A 的峰值电流,以及适当的散热片。

概括

充分了解所需的栅极驱动电路后,可以相对轻松地并行使用 GaN 功率晶体管。最大的挑战与许多工程师使用当前的硅技术永远无法体验的高功率和开关频率有关。通过遵循良好 PCB 布局的基本规则、在栅极和开尔文源路径中使用 CM 电感器以及平衡晶体管之间的电流,破坏性振荡的可能性被最小化。

审核编辑:汤梓红

-

氮化镓晶体管的并联设计技术手册免费下载2025-02-27 1603

-

氮化镓: 历史与未来2023-06-15 2165

-

迄今为止最坚固耐用的晶体管—氮化镓器件2023-02-27 1662

-

氮化镓晶体管历史2023-02-12 1163

-

氮化镓晶体管的优点2023-02-08 1494

-

氮化镓晶体管应用范围2023-02-07 1109

-

氮化镓场效应晶体管与硅功率器件比拼之包络跟踪,不看肯定后悔2021-04-13 1975

-

SGN2729-250H-R氮化镓晶体管2021-03-30 1328

-

CMPA801B025F氮化镓(GaN)高电子迁移率 基于晶体管2020-12-03 1048

-

QPD1004氮化镓晶体管2018-07-30 1543

-

QPD1018氮化镓晶体管2018-07-27 1200

-

TGF2977-SM氮化镓晶体管2018-07-25 1925

-

放大器尺寸再减50%!TriQuint卓越增益新氮化镓晶体管2012-12-19 1647

全部0条评论

快来发表一下你的评论吧 !