英飞凌简化了 PCB 安装封装,以提高硬辐射功率电子设备的效率

今日头条

描述

设计人员在不影响熟练程度的情况下安装印刷电路板 (PCB) 的噩梦推出了英飞凌科技公司 International Rectifier HiRel Products (IR HiRel) 的一款新产品。解决方案是将十四个新的 QPL 认证、抗辐射(rad-hard) SupIR-SMD MOSFET,安装在直接到 PCB 的 PCB 安装封装中。SupIR-SMD 是用于从卫星到航天器等各种任务的高性能空间电源系统的解决方案。

将表面贴装元件 (SMD) 固定到印刷电路板 (PCB) 对许多设计人员来说是一个挑战,尤其是那些处理空间问题的设计人员。很多时候,不同的热系数会导致所用材料的膨胀错位,从而导致效率损失。“太空应用需要高可靠性的电力电子设备,能够在最恶劣的环境中达到规范要求。它们必须能够承受严酷的热、机械和辐射条件,预期寿命为 15 年或更长。SupIR-SMD 是一种出色的热膨胀和热传递封装解决方案,”IR HiRel 营销总监 Andrew Popp 说。

空间环境用PCB

空间环境中的 PCB 必须满足预期的功能并提供持续的性能,同时还要确保在通信卫星、遥感卫星、导航卫星和其他行星卫星等大气中的高可靠性。航天应用中使用的电子元件主要受到空间辐射的影响,称为单事件效应或 SEE,由地球磁场中的电子和质子引起。

航天级PCB在航天发射过程中会受到冲击和压力,必须确保在空间辐射和真空条件下运行的能力。真空条件使 PCB 难以散热;如果处理不当,它们可能会出现裂纹和焊点问题。

太空硬件最重要的因素是可靠性,因为除非在某些极端情况下,否则不可能修复它。PCB 设计可以对航天器的可靠性产生直接影响。

卫星和航天器航空电子设备越来越多地 将高功率与射频传输结合起来。所有这些功能都定义了对 PCB 的设计、布局和构造的独特要求,还定义了为此目的选择合适的介电材料、堆叠中的层数、布线、轨道几何形状和接地。如今,电子系统需要高水平的性能。从高速数字电路到射频功率放大器和大功率 LED 模块,在所有这些领域中,材料的选择是设计人员减少与散热和电磁干扰相关的可能问题的重要目标。

优质材料的选择通常是成本和性能之间的折衷。

需要考虑的一些参数是信号完整性、抗噪性和散热。

介电常数是许多 PCB 材料选择过程的起点,也是热膨胀系数 (CTE) 和耗散因数的起点。

良好的信号完整性还可以评估一些因素,例如电磁兼容性要求和 EMI、电磁干扰要求。材料的选择确保了一个完美的解决方案,可以限制串扰噪声,同时限制可能影响系统功能的损失。

CTE 显示了 PCB 材料在加热后膨胀的速度。CTE 是一种表示材料在温度变化期间体积变化量的方法,以每摄氏度百万分之几表示。大多数基板具有比铜更高的 CTE。当 PCB 温度升高时,会导致互连问题。

新包

PCB 和密封表面贴装之间的热膨胀系数 (CTE) 未对准带来了两个基本挑战。在接口处保持可靠的焊点并保持密封功率 MOSFET 的密封完整性至关重要。即使是很小的 CTE 失配也会导致热应力引起的界面断裂。

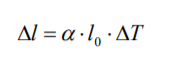

材料随温度膨胀的特性是众所周知的。它出现在所有三 (3) 个维度中。这种膨胀会产生同样的张力,会导致装配问题。由于温度变化而引起的材料长度变化由下式定义:

在哪里:

l 是材料长度,

α 是线性膨胀系数,单位为 10-6 /K(或 ppm/K),并且

ΔT 是以开氏度为单位的温度变化。

因此,对于 100 ppm/K 的 α,材料长度将发生 0.01% 的变化。即使很小的偏差也会引起应力和变形(表 1)。

表 1:分析中使用的材料特性(来源:英飞凌)

IR HiRel 设备存储在密封包装中,主要由金属和陶瓷组合制成。陶瓷的 CTE 约为六 (6) ppm/K,大多数 PCB 的 CTE 范围为 13-14 ppm/K(FR-4 板)或 17-18 ppm/K(聚酰亚胺板)。这种大错位带来了重大的设计挑战,例如焊接疲劳和封装应力。金属具有延展性,而陶瓷则易碎。如果承受高强度的应力,金属会承受很大的应变而不会破裂,而陶瓷则会破裂。这种“成败”,陶瓷的一种特性,给密封封装的设计增加了另一个挑战。

多年来,当表面贴装功率器件直接安装在 PCB 上时,陶瓷开裂一直是一个问题。

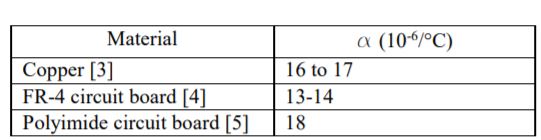

设计人员目前正在使用各种配置,将电源封装倒置并使用电缆连接到 PCB。这种配置不仅可以最佳地散热,而且还降低了 MOSFET 的容量。

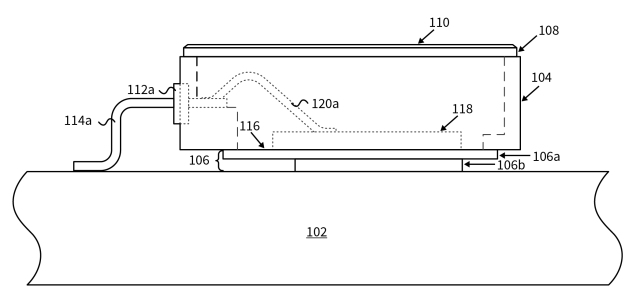

相比之下,SupIR-SMD 可以直接连接到 PCB,提供更直接的传热路径。“与空间应用中使用的典型封装解决方案相比,SupIR-SMD 的占地面积减少了 37%,质量减轻了 34%,电流容量增加了 33%,”安德鲁说。

他继续说道,“一些好处可能如下:逐渐从陶瓷到 PCB 的 CTE 变化,减少巨大的 CTE 失配带来的压力;通过安装模具的零件底部的更直接的热路径。

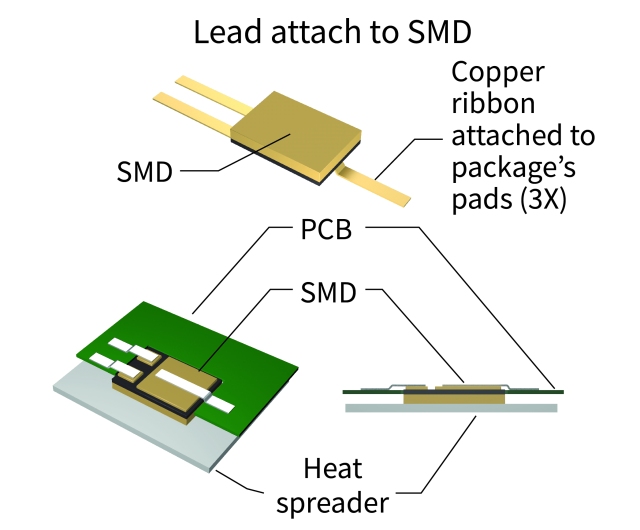

为解决电源封装与印刷电路板之间大量 CTE 错位导致的开裂问题,最大限度地降低热阻和电阻,IR HiRel 采用了如图 2 所示的多级设计。或更大的 SMD 的载体是一个不雅和次优的解决方案,现在 SupIR-SMD 解决了这个问题,”安德鲁说。

图 1:用于解决组装热膨胀问题的 SMD 引线连接选项(来源:IR HiRel)

图 2:SupIR-SMD,一种新的设计概念(剖视图显示内部芯片和引线键合)(来源:IR HiRel)

在该设计中,基体有两层,连接陶瓷体的层具有与陶瓷CTE匹配的CTE,连接印刷电路板的涂层在第一层和印刷电路板之间具有CTE值。通过这种方式,CTE 逐渐从陶瓷变为 PCB,从而减少了巨大的 CTE 错位带来的应力。

SupIR-SMD 封装符合 MIL-PRF-19500 的 JANS 标准。JANS 是最严格的筛选和验收要求,可确保用于太空飞行的分立半导体的性能、质量和可靠性。根据适用于空间应用的合格产品清单 (QPL),新的抗辐射 MOSFET 也通过了 QPL 认证。抗辐射 MOSFET 的共享应用包括卫星总线配电系统、航天级 DC-DC 转换器和其他高速开关设计。

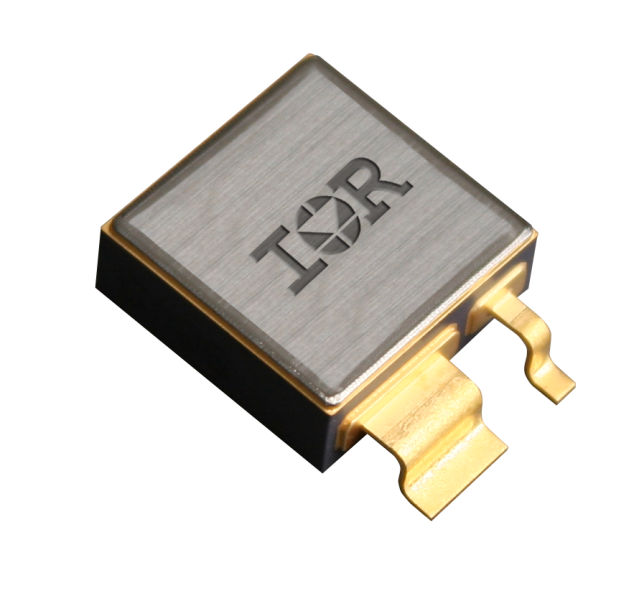

图 3:SupIR-SMD 封装

审核编辑 黄昊宇

-

PCB是所有电子设备的核心油泼辣子 2023-11-18

-

手机辐射功率2011-04-11 2340

-

车载电子设备空间辐射超标的频谱分析法2015-08-05 7830

-

电力电子设备的现状与展望2018-08-05 9202

-

航空电子设备PCB组件的实验模态分析2018-09-13 3583

-

需要距离辐射源多远才能使辐射信号不干扰系统呢?2019-01-18 2757

-

浪涌抑制器IC简化了针对危险环境的电子设备的本质安全屏障设计2019-04-09 3140

-

请问M24SR64 NFC辐射功率是什么?2019-08-09 2053

-

如何解决电子设备对外辐射干扰2020-10-23 1824

-

什么是卫星通信的有效全向辐射功率(EIRP)2010-04-03 6727

-

芯片辐射功率等级、灯珠支架材料和芯片尺寸等区别对封装质量的影响2017-09-22 1734

-

直流接触器的使用简化了电路板设计过程2022-03-01 921

-

如何最大限度地提高电子设备中能量收集的效率2022-12-30 2136

-

英飞凌SiC芯片嵌入PCB提高效率2023-05-05 1625

-

无线通信系统中等效辐射功率和链路预算的计算2023-09-07 3632

全部0条评论

快来发表一下你的评论吧 !