简单科普一下静电放电的基本概念、模型与测试方法

EMC/EMI设计

描述

在芯片的生产,制造,测试,存储,运输,装配及使用等过程中,都会产生大量的静电荷,静电放电(ESD, Electrostatic Discharge)现象无处不在。随着器件特征尺寸的降低和电路复杂化的提升,静电放电问题也逐渐成为集成电路中非常重要的可靠性问题之一。

下面小编就给大家简单科普一下静电放电的基本概念、模型、测试方法以及常用于I/O接口的静电防护器件和电路。

静电放电的基本概念

静电放电现象指的是芯片在制造,运输,使用的过程中都会积累的电荷,这些电荷可以通过芯片引脚进入电路内部,瞬间产生高达数安的电流,从而将芯片烧毁。

静电放电产生的失效机制主要有两种,一种是热击穿,一种是电击穿。产生热击穿的根本原因是ESD脉冲产生了瞬间大电流,这时因为半导体组件的热传导特性都不是很好,由ESD电流所产生的大量热量使得温度上升,而由于ESD现象所发生的时间非常短暂,所以此过程中产生的热量很难被泄放。产生电击穿的根本原因是大电场所引起的介质击穿,这种情况经常发生在MOSFET的栅氧处。知道了产生ESD损害的原因,我们在ESD防护设计中就需要处理大电流和高电压的问题。因此,片上ESD防护的原则有以下两条:一是通过低阻通道安全泄放ESD电流,二是将电压钳在一个较低的水平。

静电放电模型

ESD事件依据静电放电产生原因及其对集成电路放电方式的不同可分成以下四类模型:

(1)人体放电模型(HBM, Human-Body Model)

(2)机器放电模型(MM, Machine Model)

(3)器件充电模型(CDM, Charged-Device Model)

(4)电场感应模型(FIM, Field-Induced Model)

以最为人熟知也最常用的人体放电模型(HBM)为例来介绍下ESD模型的概念。如图1所示,HBM模型是指通过接触芯片,人体上由于摩擦或其他因素所积累的静电从芯片内流过泄放至地,放电时间只有几百纳秒,而瞬间的放电电流可达到数安培,从而足以将芯片内部的组件烧毁。对于一般商用芯片标准2KV 静电防护电压而言,其对应的瞬间放电电流最大值可达到1.33A。

静电防护器件的常用测试方法

传输线脉冲测试(TLP, Transmission Line Pulse)是测量ESD防护元件的I-V特性曲线的一种方法,通过恒定阻抗传输线所生成的短脉冲用来模拟ESD脉冲,作用在防护器件上。

通过传输线可以产生ESD电流脉冲从而对ESD器件进行测试。在传输线脉冲测试中,传输线由电压源充电,然后向器件输入矩形脉冲电流。TLP测试的脉冲宽度与传输速度和传输线长度有关。在TLP测试方法中,脉冲宽度的选择基于HBM模型,这种表征方法对于器件的导通特性提供了一个较为精确的估计,在二次击穿点前的TLP测试曲线可以很好地表征器件在ESD压力下的状态。

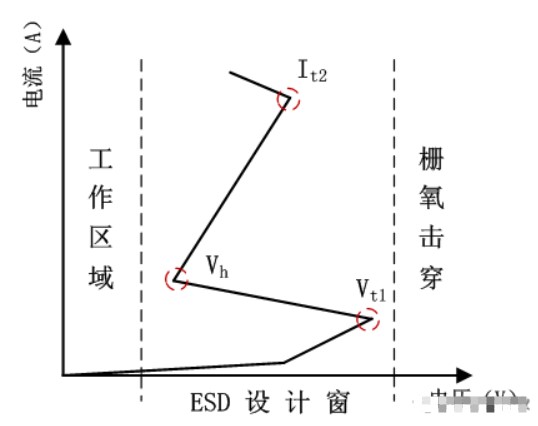

图2描绘的是在TLP脉冲下,待测器件的I-V特性曲线。该曲线中包含三个较为关键的技术指标,分别是触发电压Vt1,维持电压Vh,以及二次击穿电流It2。而这三点也限制了ESD设计窗口。触发电压需要小于内部电路的栅氧击穿电压以保证电路不受ESD影响,维持电压需要大于内部电路的工作电压以避免闩锁问题,而二次击穿电流则决定了静电防护器件的最高耐压值,表征了器件的防护等级。

图2 ESD器件的I-V特性曲线

常见I/O接口的ESD防护器件及电路

对于IC设计来说,有效地设置片上ESD防护结构是最有效的方法。早期,齐纳二极管被广泛应用到ESD保护上,而后,随着对ESD防护要求的提高,其他的ESD防护结构应运而生,比如BJT结构,MOS结构,可控硅(SCR, Silicon Controlled Rectifier)结构,以及其他双向防护器件。

在芯片的I/O接口需要设置ESD防护器件和电路以确保当ESD事件到来时能够进行有效的电流泄放,并且将电压钳制在一定的水平。下面简要介绍I/O接口中常用的ESD防护器件及电路。

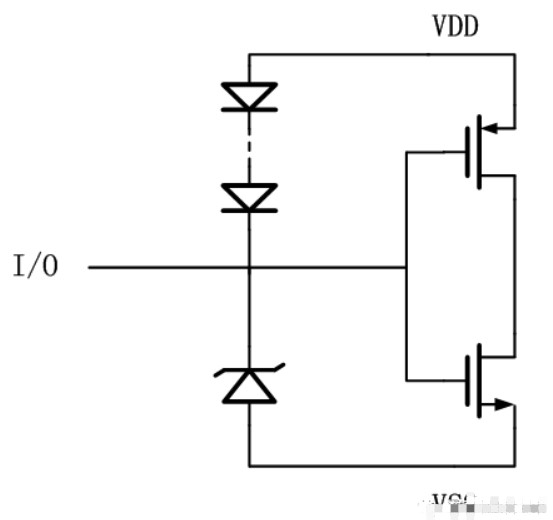

(1)结型二极管是最原始的ESD防护结构,由于其简单高效,目前仍被广泛使用。以齐纳二极管为例,其正向偏置和反向偏置均可以用作ESD防护,典型电路如图3。因为二极管的正向开启电压较低,单一的正向二极管一般不能够单独使用,取而代之的是二极管链,但是这样又会引起达林顿效应。相比较来说,反向的二极管则更为简单和实用。将二极管应用到ESD防护中的优势是其可以加入到电路仿真当中。

图3 应用到I/O口的二极管ESD防护器件

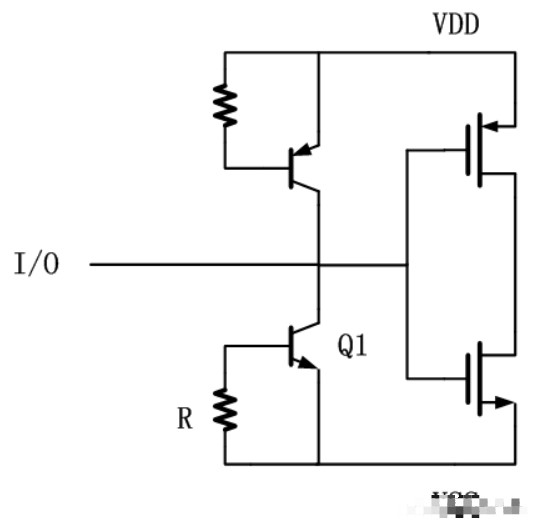

(2)双极结型晶体管(BJT)利用其回滞模型进行ESD防护,典型的防护电路如图4。当正向的ESD脉冲加在I/O接口时,BJT Q1的集电结反偏直至击穿,当电阻R上的压降达到足够大时,发射结开启,Q1导通。此时集电极处的电压VC下降,Q1进入到回滞区域,低阻泄放通道产生,安全泄放ESD电流。同时I/O接口处电压被钳制在较低的维持电压。

图4 应用到I/O口的BJT ESD防护器件

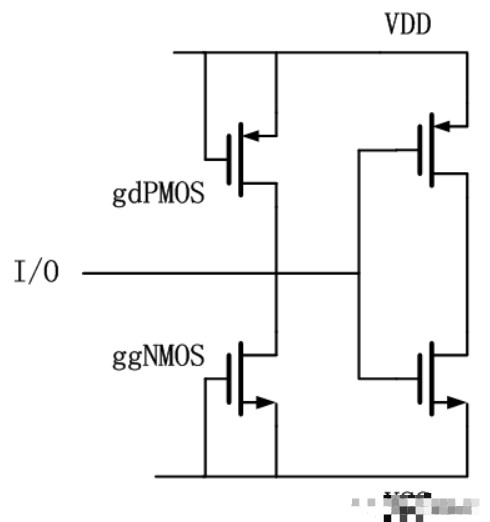

(3)最简单的MOS类ESD防护器件是栅接地NMOS结构(ggNMOS, Gate Grounded NMOS),其中漏极接I/O接口,源极、栅极和衬底都接地。其ESD防护性能由其寄生的NPN三极管决定,其栅接地的主要原因就是确保ESD防护结构在正常的工作情况下没有泄漏电流。图5是典型的MOS类ESD防护器件应用到芯片的I/O接口图,其中I/O口到VDD之间使用了gdPMOS器件。gdPMOS器件和ggNMOS器件的原理相似,只是它利用其内部的寄生PNP三极管进行电流泄放。

图5 应用到I/O口的MOS类ESD防护器件

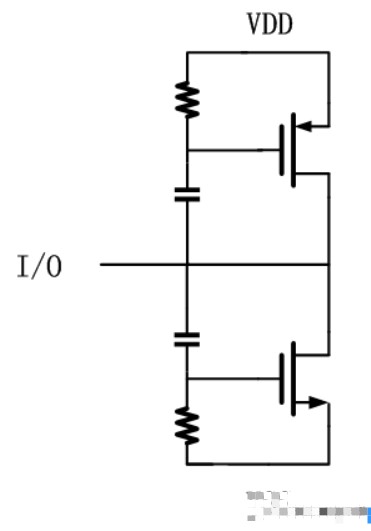

(4)常用的ESD防护结构还包括RC触发的NMOS结构(GCNMOS, Gate Coupled NMOS)。该结构利用电容耦合的方法降低了器件的触发电压,并且有利于器件的均匀导通。根据不同的情况可以在RC触发电路和NMOS的栅极之间加入反向器构成GDNMOS(Gate Driven NMOS)结构,但是该结构触发电路占用过多的版图面积这一缺点也不容忽视。

图6 应用到I/O口的RC触发的MOS结构

审核编辑:刘清

-

汽车整车静电放电测试2016-02-23 4434

-

手机的静电测试方法2017-09-29 5590

-

电路静电防护小科普:了解放电器件与ESD防护方法2019-05-28 3028

-

系统层级静电放电与芯片层级静电放电有什么差异2019-07-25 2265

-

USB基本概念及从机编程方法介绍2021-11-08 1863

-

讲解一下A/D和 D/A的基本概念2021-11-25 2118

-

探讨一下PWM基本概念与简单基础的应用2022-02-24 1210

-

人体静电放电(ESD)及保护电路的设计2009-08-05 1070

-

介绍一下ARCore的基本概念并剖析其工作机理2018-01-24 6805

-

静电放电ESD的介绍和原理及解决方法概述2019-01-07 5354

-

简单科普一下GPS和GNSS和区别2023-03-05 6970

-

给大家科普一下什么是APN及配置方法2023-03-13 10161

-

静电放电的测试方法 静电放电问题整改案例2023-09-05 1751

-

静电放电模型中的阻容参数2023-11-24 1625

-

浅谈静电放电(ESD)测试2025-03-17 2714

全部0条评论

快来发表一下你的评论吧 !