富昌电子SiC设计分享(五):SiC MOSFET 相关应用中的EMI改善方案

EMC/EMI设计

1295人已加入

描述

富昌电子(Future Electronics)一直致力于以专业的技术服务,为客户打造个性化的解决方案,进而缩短产品的设计周期、加快行业发展的步伐。在第三代半导体的实际应用领域,富昌电子结合自身的技术、项目经验积累,着笔SiC相关设计的系列文章,希望能给到大家一定的参考,并期待与您进一步的交流。

本文作为系列文章的第五篇,主要针对SiC MOSFET相关应用中的EMI改善方案做一些探讨。

对设计人员而言,成功应用 SiC MOSFET 的关键在于深入了解 SiC MOSFET 独有的工作特征及其对设计的影响。SiC MOSFET的快速开关速度,高额定电压和低RDS(on)使其对于不断寻求在提高效率和功率密度的同时,保持系统简单性的电源设计人员具有很高的吸引力。但是,由于高压及超快的开关速度带来的超高di/dt,dv/dt,会通过系统的杂散电感,电容形成干扰,比如SiC MOSFET过高的开关速度会引起Vds振铃尖峰,因而产生EMI。

寄生电感是SiC MOSFET Vds尖峰和振铃的主要原因。SiC MOSFET的快速开关速度会导致较高Vds尖峰和较长的振铃时间。这种尖峰会降低设备的设计裕量,并且较长的振铃时间会引入EMI。在大电流情况下,该现象更加明显。

判断EMI是否来源于di/dt与dv/dt,以及采用合适的、有针对性的方案就显得尤为重要,常见的EMI解决方案技术如下:

1, 通过使用高栅极电阻(Rgon, Rgoff)来实现降低通过器件的电流变化率(dI/dt). 高的Rg会显着增加开关损耗, 需要在效率和EMI平衡。

2,通过使用门极漏极电容Cgd来降低器件Vds的电压变化率(dv/dt), 高的Cgd同样会增加开关损耗, 需要在效率和EMI平衡。

3, 降低功率环路的杂散电感,最大限度缩短导线长度,降低 PCB布局的电感(如将栅极驱动器放在尽可能靠近 MOSFET 的位置,并使用叠接式导线几何形状而不是并排(共平面)几何形状),也是改善EMI的有效方法,需要在最小间距和间隙安全规定平衡。

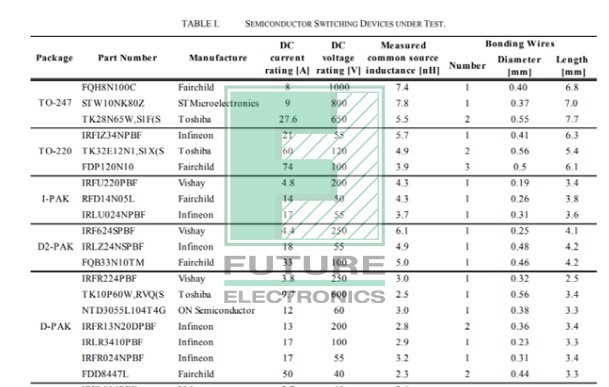

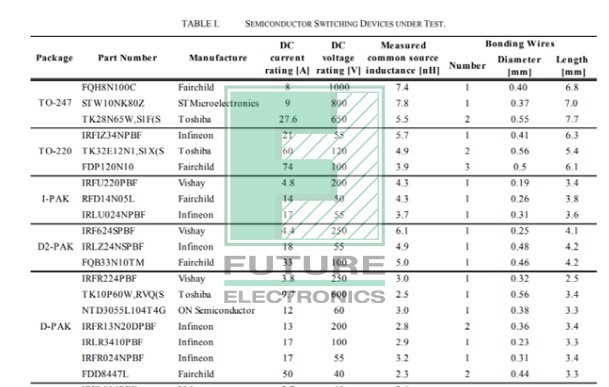

4,使用新的封装如贴片低引线电感(如图一),封装电感是决定切换时间的关键参数,而切换时间与开关速度和EMI等密切相关,需要在的封装和热性能平衡。

5,新的数控技术(如频率抖动, 软开关技术等) 对低和高频段的EMI有好处 。

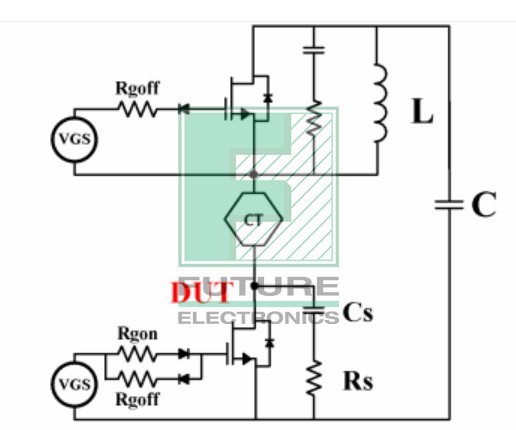

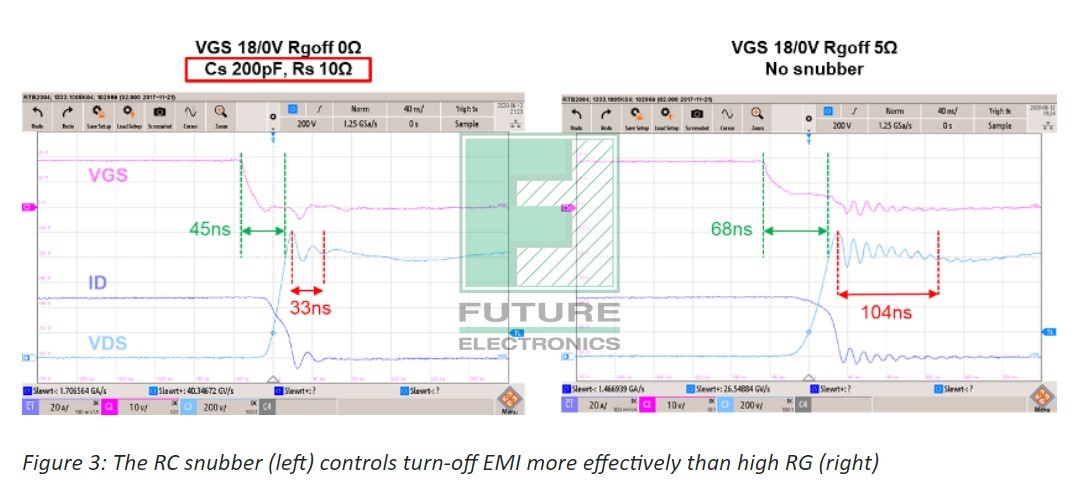

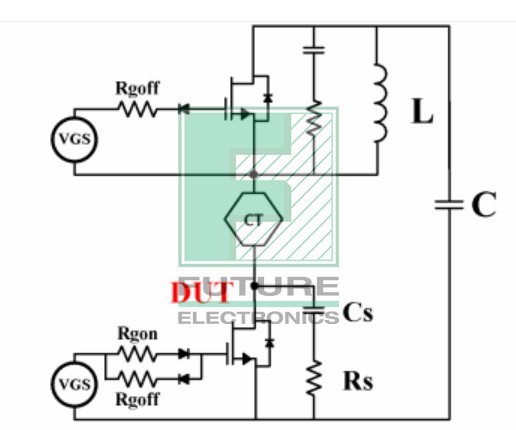

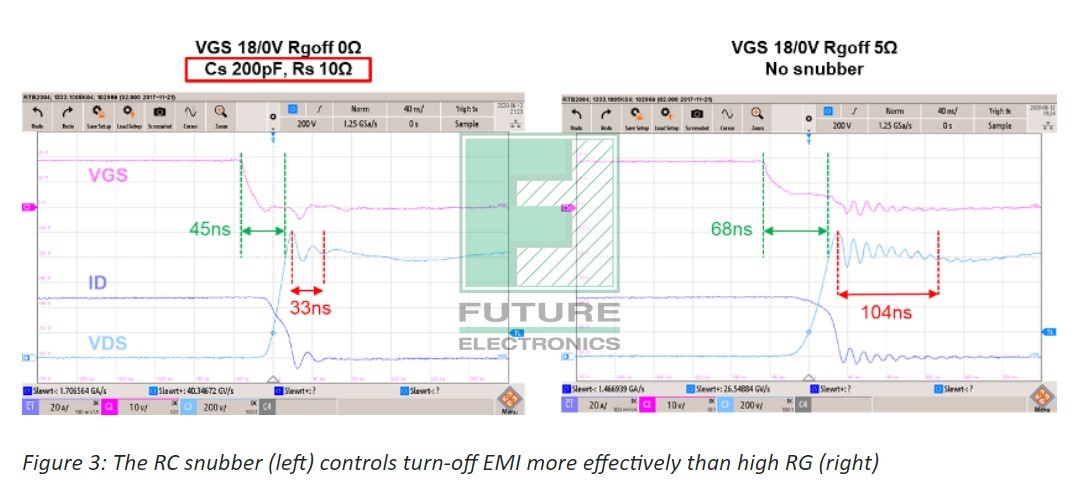

6,使用缓冲器(如RCD) 对Vds振荡尖峰做吸收(如图二),也能明显改善Vds抖动和EMI(如图三所示测试结果),但是需要在效率和EMI平衡。相比于调节Rg,该方案相对高效。

结论: 以上是富昌电子与客户工程师交流总结的EMI方案,供参考。 由于EMI的产生原因和机理不同,方案也不一样,有时需要多种方案综合评估。如需进一步探讨,请联系富昌电子技术方案中心。

关键字: 碳化硅,SiC,SiC MOSFET,EMI改善,新能源汽车,储能,富昌电子

参考文献:

打开APP阅读更多精彩内容

本文作为系列文章的第五篇,主要针对SiC MOSFET相关应用中的EMI改善方案做一些探讨。

对设计人员而言,成功应用 SiC MOSFET 的关键在于深入了解 SiC MOSFET 独有的工作特征及其对设计的影响。SiC MOSFET的快速开关速度,高额定电压和低RDS(on)使其对于不断寻求在提高效率和功率密度的同时,保持系统简单性的电源设计人员具有很高的吸引力。但是,由于高压及超快的开关速度带来的超高di/dt,dv/dt,会通过系统的杂散电感,电容形成干扰,比如SiC MOSFET过高的开关速度会引起Vds振铃尖峰,因而产生EMI。

寄生电感是SiC MOSFET Vds尖峰和振铃的主要原因。SiC MOSFET的快速开关速度会导致较高Vds尖峰和较长的振铃时间。这种尖峰会降低设备的设计裕量,并且较长的振铃时间会引入EMI。在大电流情况下,该现象更加明显。

判断EMI是否来源于di/dt与dv/dt,以及采用合适的、有针对性的方案就显得尤为重要,常见的EMI解决方案技术如下:

1, 通过使用高栅极电阻(Rgon, Rgoff)来实现降低通过器件的电流变化率(dI/dt). 高的Rg会显着增加开关损耗, 需要在效率和EMI平衡。

2,通过使用门极漏极电容Cgd来降低器件Vds的电压变化率(dv/dt), 高的Cgd同样会增加开关损耗, 需要在效率和EMI平衡。

3, 降低功率环路的杂散电感,最大限度缩短导线长度,降低 PCB布局的电感(如将栅极驱动器放在尽可能靠近 MOSFET 的位置,并使用叠接式导线几何形状而不是并排(共平面)几何形状),也是改善EMI的有效方法,需要在最小间距和间隙安全规定平衡。

4,使用新的封装如贴片低引线电感(如图一),封装电感是决定切换时间的关键参数,而切换时间与开关速度和EMI等密切相关,需要在的封装和热性能平衡。

5,新的数控技术(如频率抖动, 软开关技术等) 对低和高频段的EMI有好处 。

6,使用缓冲器(如RCD) 对Vds振荡尖峰做吸收(如图二),也能明显改善Vds抖动和EMI(如图三所示测试结果),但是需要在效率和EMI平衡。相比于调节Rg,该方案相对高效。

图一

图二

图三

结论: 以上是富昌电子与客户工程师交流总结的EMI方案,供参考。 由于EMI的产生原因和机理不同,方案也不一样,有时需要多种方案综合评估。如需进一步探讨,请联系富昌电子技术方案中心。

关键字: 碳化硅,SiC,SiC MOSFET,EMI改善,新能源汽车,储能,富昌电子

参考文献:

- EMI Prediction Method for SiC Inverter by Developing an Accurate Model of Power Device.

- How to Minimize EMI and Switching Loss When Using SiC MOSFETs

- Switching Fast SiC FETs with a Snubber.

- Challenges in Switching SiC MOSFET without Ringing.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

富昌电子SiC设计分享(二):碳化硅器件驱动设计之寄生导通问题探讨2022-06-16 110116

-

富昌电子SiC设计分享(三):SiC MOSFET 和Si MOSFET寄生电容在高频电源中的损耗对比2022-07-07 3231

-

富昌电子SiC设计分享(一):SiC MOSFET驱动电压的分析及探讨2022-05-30 8917

-

富昌电子SiC设计分享(四):SiC MOSFET Desat设计注意事项2022-08-01 4011

-

富昌电子SiC设计分享(六):ESS 储能系统中SiC器件的应用2022-09-28 1867

-

为何使用 SiC MOSFET2017-12-18 6043

-

SiC-MOSFET的应用实例2018-11-27 6069

-

SiC-MOSFET与Si-MOSFET的区别2018-11-30 11060

-

沟槽结构SiC-MOSFET与实际产品2018-12-05 4850

-

搭载SiC-MOSFET和SiC-SBD的功率模块2019-03-12 3436

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5703

-

SiC MOSFET SCT3030KL解决方案2019-07-09 2472

-

SiC MOSFET:经济高效且可靠的高功率解决方案2019-07-30 4257

-

SiC MOSFET的器件演变与技术优势2023-02-27 1554

-

SiC MOSFET应用中的EMI改善方案分析2022-08-29 2177

全部0条评论

快来发表一下你的评论吧 !