功率MOSFET的常见封装与布局配置

功率器件

描述

栅极驱动器和功率 MOSFET 的放置对于前置驱动器电机驱动解决方案的正确运行和性能优化至关重要。对于具有集成 MOSFET 的电机驱动器,例如 DRV8870、DRV8313、DRV10987、DRV10983-Q1和DRV8873-Q1,在内部已完成了正确布线。对于DRV8701,DRV8304、DRV8306、DRV8323、DRV8343-Q1 和 DRV8353 等栅极驱动器,仔细规划 PCB 的布局和功率 MOSFET 的放置方式非常重要。以下部分将介绍一些常见的 MOSFET 拓扑,并展示一些使用常见电机驱动架构的基本布局示例。

功率 MOSFET 的常见封装

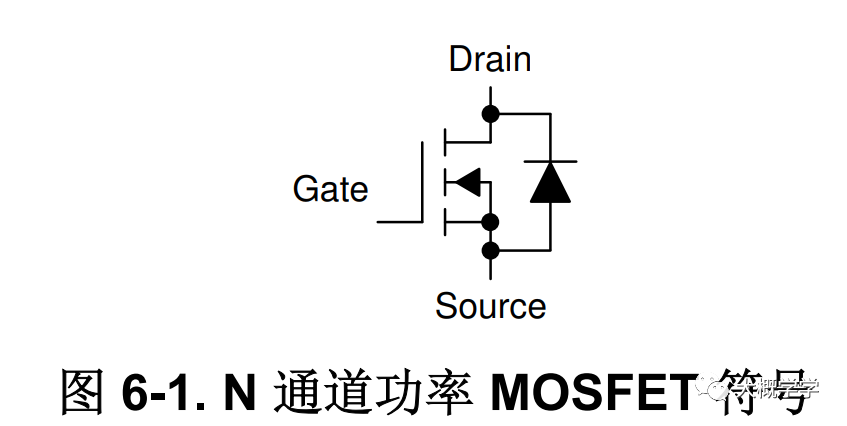

本部分将介绍N通道功率 MOSFET 的一些常见封装类型。大多数功率 MOSFET具有这四种选项之一。通过了解封装类型、尺寸和引脚排列,能够更好地设计 PCB 以构建出色的解决方案。图 6-1中的符号代表了一个 N 通道功率MOSFET。虽然MOSFET 是具有源极、栅极、漏极和衬底的四端子器件,但衬底端子通常是源极端子。

MOSFET 封装与功率级和热耗散之间有着直接关系。不同的封装有不同的布线规则。

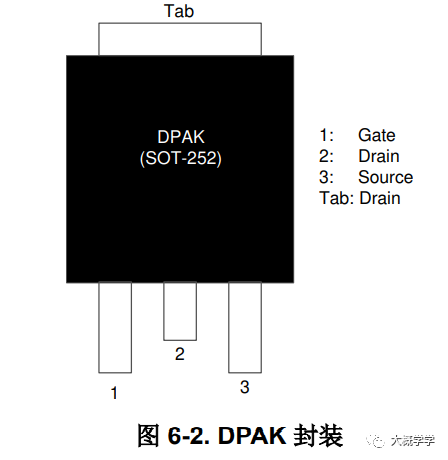

DPAK

图 6-2所示的 DPAK (SOT-252) 封装是业内常用的封装之一。该封装在尺寸和性能之间进行了折衷。DPAK 封装通常用于高功率MOSFET和稳压器。

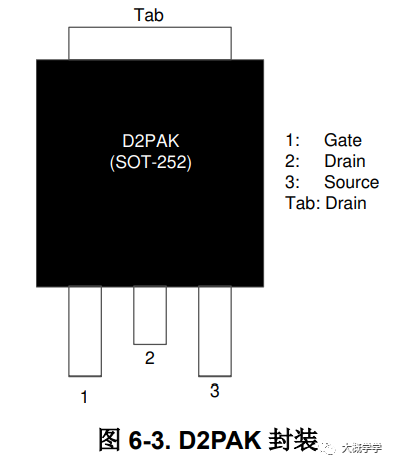

D2PAK

D2PAK (SOT-252) 封装(请参阅图 6-3)是 DPAK 封装的更大版本,具备更好的散热效能。

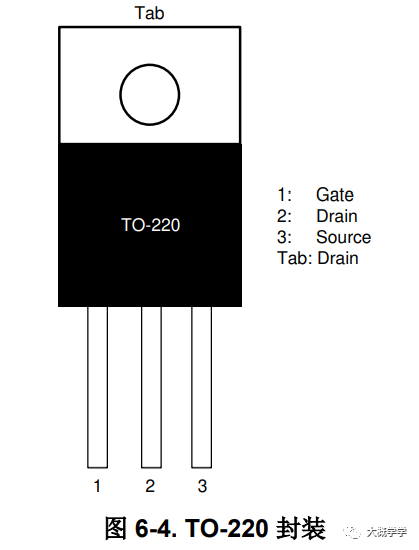

TO-220

TO-220 封装(请参阅图 6-4)是一种穿孔的 MOSFET 封装。可使用直立锁片来安装散热器。使用这种封装的缺点是它需要更多的空间,通常比表面贴装封装(例如 DPAK 和 D2PAK 封装)更高。

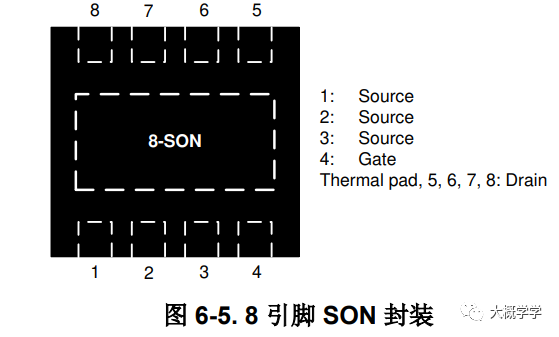

8 引脚 SON

8 引脚 SON 封装(请参阅图 6-5)是常见的无引线封装,可实现布板空间超小且性能出色的解决方案。大多数引线式封装具有类似的引脚排列。与引线式封装(TO-252 和 TO-220)相比,8 引脚 SON 封装别具一格,因为其栅极引脚位于相反的一侧。

MOSFET 布局配置

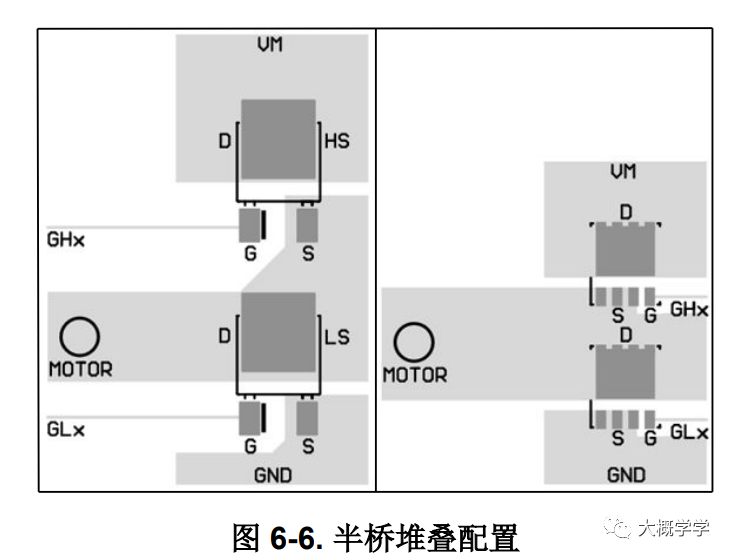

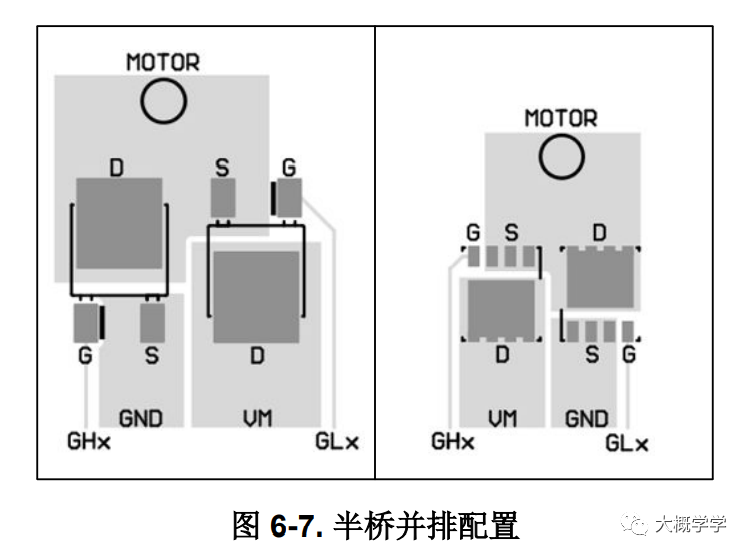

图 6-6 和图 6-7 展示了以下两种典型配置的常见 MOSFET 的放置和布局方式:分别为半桥堆叠和半桥并排,适用于引线式封装和无引线封装。

这些半桥布局可重复用于多种半桥拓扑,包括 H 桥(两个半桥)、逆变器(三个半桥)和双 H 桥(四个半桥)。

功率级布局设计

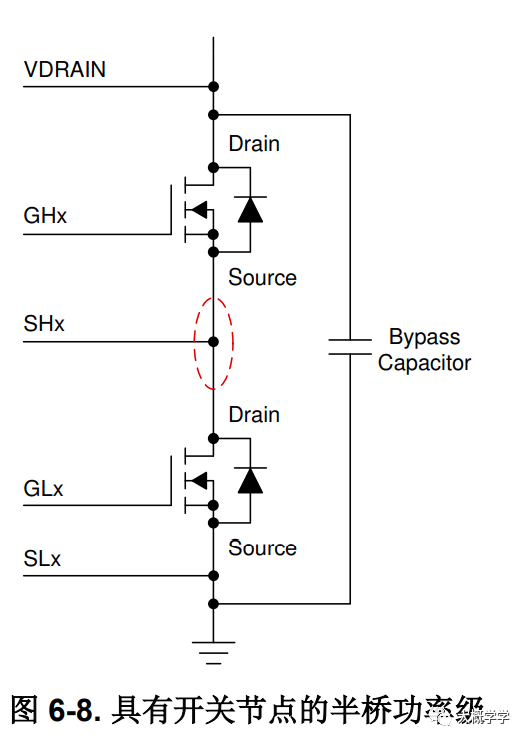

为功率 MOSFET 选择正确的放置方式后,下一步是确保布线正确。MOSFET 用于电机驱动器的大功率开关应用,因此该设计对非理想布局引起的寄生效应很敏感。本部分将介绍一些需要布线的重要信号以及管理它们的最佳实践。图 6-8 展示了功率级。

开关节点

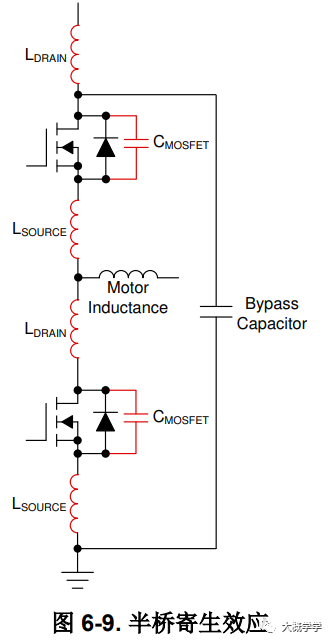

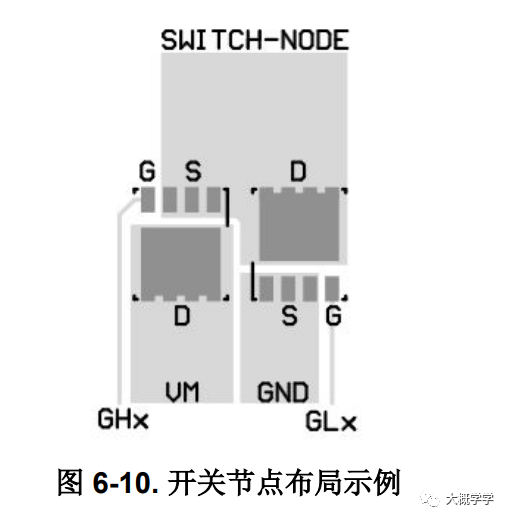

如图 6-10 所示,开关节点是高侧 MOSFET 的源极引脚和低侧 MOSFET 的漏极引脚之间的连接。该节点是最终连接到负载(在此应用中是一个电机)的网络。因为该网络上的信号具有高频、大电流特性,开关节点是半桥配置中需要布线的关键信号。图 6-8 中所示电路具有许多由 PCB 和功率 MOSFET 引起的非理想寄生效应。图 6-9 展示了这些主要寄生效应中的一部分,它们是引发“开关节点振铃”现象的主要原因。

开关节点振铃是开关节点上由于 PCB 和功率 MOSFET 的寄生效应而产生的 LC 振荡。开关节点振铃会导致 EMI 并产生过冲和下冲电压,这些值会超出 MOSFET 漏源电压和栅极驱动器引脚的绝对最大额定值。此外,还会降低功率级的效率。可通过外部措施和系统调整(降低压摆率、使用外部缓冲器等)来解决开关节点振铃问题,但基本合理的布局可以解决许多这样的主要问题。图 6-10 的布局示例中显示的设计可最大限度地降低高侧 MOSFET 的源极与低侧 MOSFET 的漏极之间的电感。较好的做法是尽可能缩短覆铜平面连接的长度并增加其宽度,并且采用具有极小寄生电感的 MOSFET 封装。

大电流环路路径

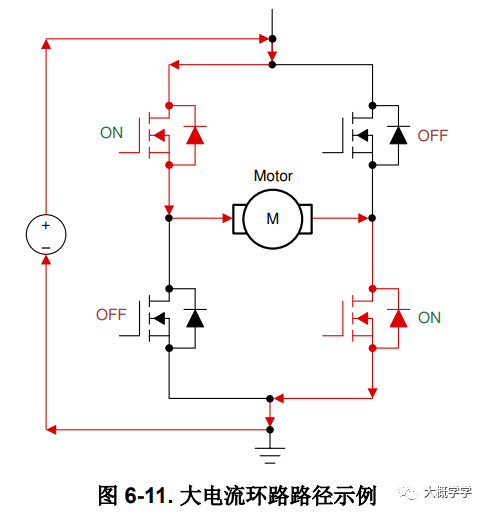

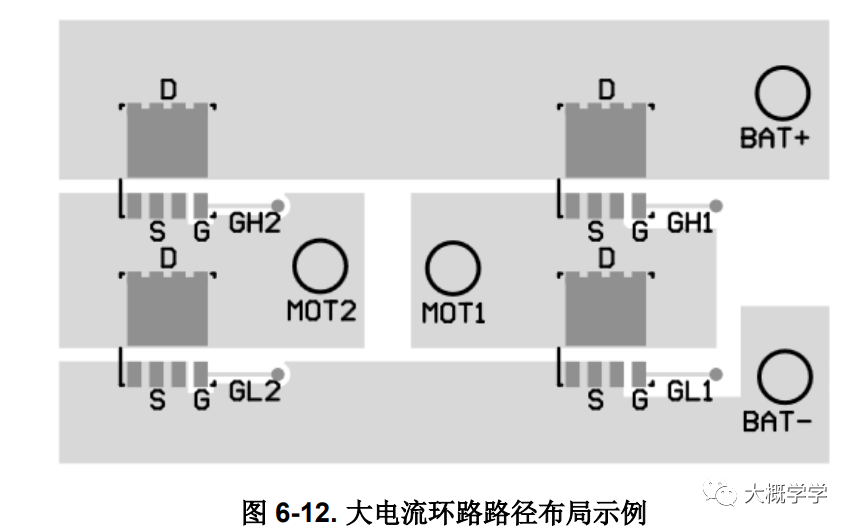

电机应用依赖于大开关电流,因此最大限度地降低大电流路径的整体环路电感至关重要。最大限度地降低该电感可将电压纹波和噪声尽可能降低,并可减少对额外旁路电容的需求。在电机系统中,大电流环路从电源的正极开始,经过高侧功率 MOSFET、电机绕组、低侧 MOSFET,再回到电源的负极。图 6-11在H桥示例中展示了这种流向。

应通过执行以下操作来最大限度地缩短大电流环路路径:

• 对完整的大电流环路使用正确的布线宽度。增加布线宽度会降低寄生电感。

• 通过正确放置来尽量减小元件之间的距离。减小布线长度会降低寄生电感。

• 最大限度地减少大电流路径中的跳层次数,并在通过大电流布线进行跳层时使用正确的过孔尺寸和数量。

图 6-12 所示为经优化的大电流环路示例布局。

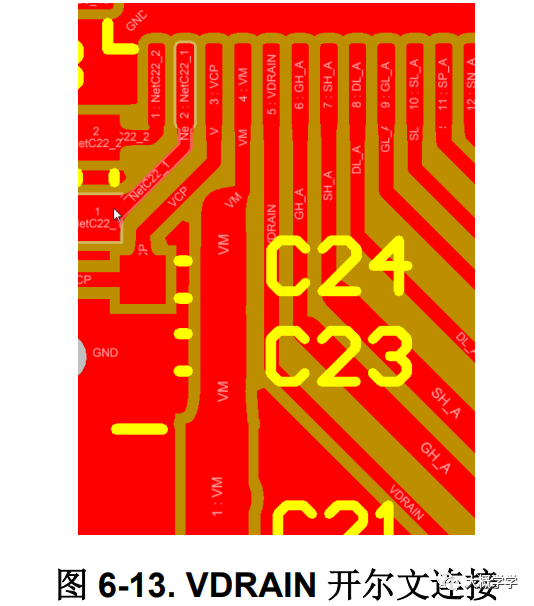

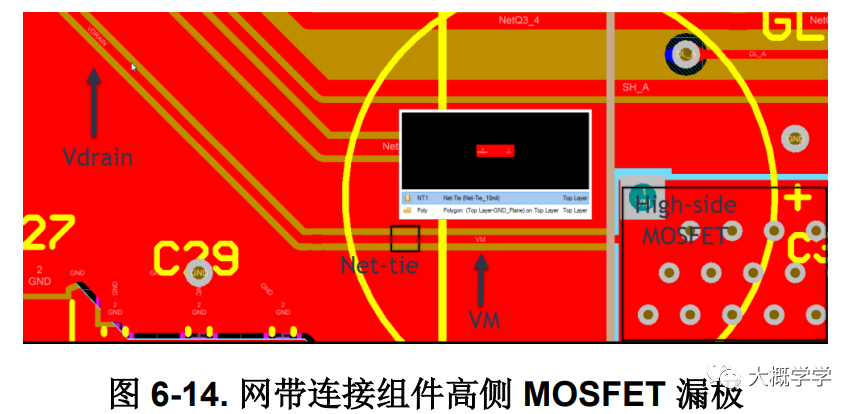

VDRAIN 感测引脚

VDRAIN 引脚用于感测高侧 MOSFET 漏极电压。具有VDRAIN引脚的电机驱动器件必须在布线时考虑尽可能改善性能。供电电压首先进入高侧 MOSFET 的漏极,因此 VDRAIN 引脚的布线对布局至关重要。VDRAIN 引脚为电源 (VM) 提供开尔文连接,因此可在发生过流事件时监测高侧 MOSFET的VDS 电压(请参阅图 6-13)。功率级中的VM连接通常包含大型覆铜平面和宽布线以支持所需的电流,因此平面的额外电感和电压降会影响 VDS 测量精度。所以,应将 VDRAIN 引脚以单一布线的形式直接连接到外部功率 MOSFET 的漏极。TI 建议使用靠近漏极的网带连接组件来最大限度地减小会导致误报 OCP 故障的额外电感(请参阅图 6-14)。

审核编辑:汤梓红

-

电源 PCB 布局中的常见错误及避免方式2025-01-08 1878

-

功率MOSFET故障分析2024-10-08 2023

-

为电机驱动提供动力的功率MOSFET2022-09-27 2310

-

MOSFET和封装技术的进步使得TI能够成功应对挑战2019-07-31 1414

-

SiC MOSFET:经济高效且可靠的高功率解决方案2019-07-30 4139

-

功率MOSFET技术提升系统效率和功率密度2019-07-04 2517

-

采用ATPAK封装功率MOSFET在开关器件设计中的应用2019-03-06 4527

-

功率MOSFET数据表解析2018-10-18 2231

-

封装寄生电感对MOSFET性能的影响2018-10-08 4316

-

理解功率MOSFET管的电流2016-08-15 12266

-

创新型MOSFET封装:大大简化您电源的设计2013-12-23 2992

-

满足供电需求的新型封装技术和MOSFET2012-12-06 3566

-

用于高压功率MOSFET的全新无管脚SMD封装ThinPAK2010-05-12 1192

-

创新封装将功率MOSFET散热效率提升80%2010-03-01 1105

全部0条评论

快来发表一下你的评论吧 !