分享使用MOSFET的双向逻辑电平转换器

描述

回到 ENIAC 时代,计算机本质上更多是模拟的,并且使用的数字 IC 很少。今天,Joe的计算机一般可以在多个电压等级下工作,看过 CPU SMPS 的人会注意到您的计算机需要 ±12V、+5V 和 +3.3V 才能运行。这些电压水平对于计算机来说非常重要。特定的电压决定了信号的状态(高或低)。计算机将这种高状态作为二进制 1 接受,将低状态作为二进制 0 接受。根据 0 和 1 条件,计算机产生数据、代码和指令以提供所需的输出。

现代逻辑电压电平在 1.8V 到 5V 之间变化很大。标准逻辑电压为 5V、3.3V、1.8V 等。但是,使用 5V 逻辑电平(例如Arduino )的系统或控制器如何与使用 3.3V(例如ESP8266)或任何其他不同电压的另一个系统通信等级?这种情况经常出现在许多设计中,其中使用了多个微控制器或传感器,这里的解决方案是使用逻辑电平转换器或逻辑电平转换器。在本文中,IC先生网将了解有关逻辑电平转换器的更多信息,我们还将使用 MOSFET 构建一个简单的双向逻辑电平转换器电路这将对您的电路设计派上用场。

高电平和低电平输入电压

但是,从微处理器或单片机方面来看,逻辑电压电平值并不是固定的;它有一些容忍度。例如,对于 5V 逻辑电平微控制器,可接受的逻辑高电平(逻辑 1)是最小 2.0V(最小高电平输入电压)至最大 5.1V(最大高电平输入电压)。同样,对于逻辑低(逻辑 0),可接受的电压值是从 0V(最小低电平输入电压)到 8V(最大低电平输入电压)的最大值。

以上示例适用于 5V 逻辑电平微控制器,但也可提供 3.3V 和 1.8V 逻辑电平微控制器。在这种类型的微控制器中,逻辑电平电压范围会有所不同。您可以从该特定控制器 IC 的数据表中获取相关信息。使用电压电平转换器时,应注意高压值和低压值在这些参数的限制范围内。

双向逻辑电平转换器

根据应用和技术结构,可提供两种类型的电平转换器,单向逻辑电平转换器和双向逻辑电平转换器。在单向电平转换器中,输入引脚专用于一个电压域,输出引脚专用于另一个电压域,但双向电平转换器并非如此,它可以双向转换逻辑信号。对于双向电平转换器,每个电压域不仅有输入引脚,还有输出引脚。例如,如果您向输入侧提供 5.5V,它将在输出侧将其转换为 3.3V,同样,如果您向输出侧提供 3.3V,它将在输入侧将其转换为 5V。

在本教程中,我们将构建一个简单的双向电平转换器,并将测试它的高到低转换和低到高转换。

简单的双向逻辑电平转换器

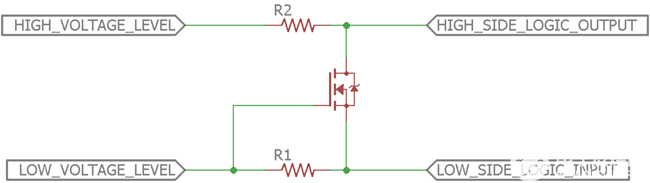

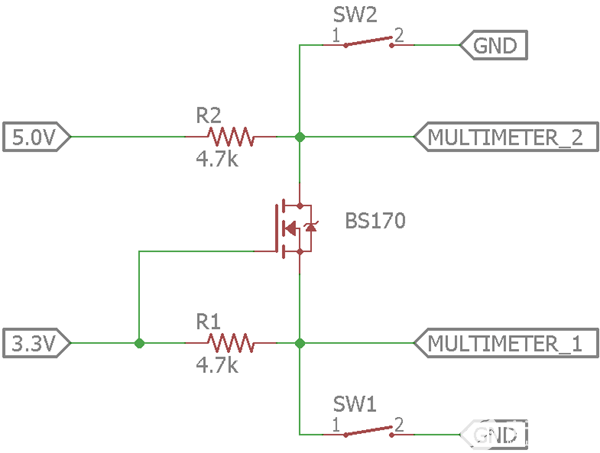

下图显示了一个简单的双向逻辑转换器电路。

该电路使用n 沟道 MOSFET将低压逻辑电平转换为高压逻辑电平。也可以使用电阻分压器构建一个简单的逻辑电平转换器,但它会引入电压损耗。基于 MOSFET 或晶体管的逻辑电平转换器专业、可靠且集成更安全。

该电路还使用了两个附加组件,R1 和 R2。那些是上拉电阻。由于零件数量最少,它也是一种具有成本效益的解决方案。根据上述电路,将构建一个简单的 3.3V 至 5V 双向逻辑转换器。

使用 MOSFET 的 5V 至 3.3V 电平转换器

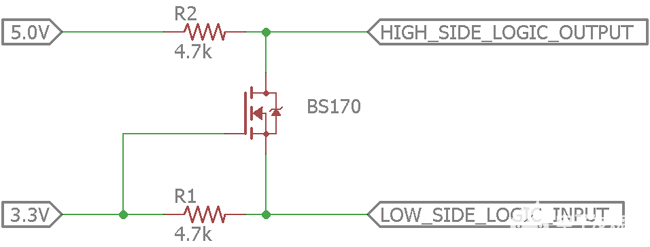

5V 到 3.3V的双向逻辑电平转换器电路如下图所示 -

如您所见,我们必须为电阻器 R1 和 R2 提供 5V 和 3.3V 的恒定电压。Low_side_Logic_Input和High_Side_Logic_Input引脚可互换用作输入和输出引脚。

上述电路中使用的元件是

R1 - 4.7k

R2 - 4.7k

Q1 - BS170(N 沟道 MOSFET)。

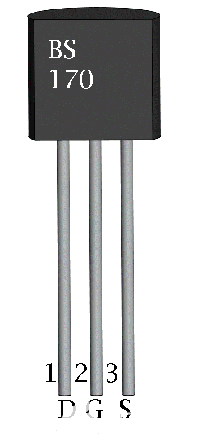

两个电阻都有 1% 的容差。容差为 5% 的电阻器也可以工作。BS170 MOSFET的引脚排列如下图所示,顺序为漏极、栅极和源极。

电路结构由两个每个 4.7k 的上拉电阻组成。MOSFET 的漏极和源极引脚被上拉到所需的电压电平(在本例中为 5V 和 3.3V),以进行低到高或高到低的逻辑转换。您也可以为 R1 和 R2 使用 1k 到 10k 之间的任何值,因为它们仅用作上拉电阻。

为了达到完美的工作状态,在构建电路时需要满足两个条件。第一个条件是,低电平逻辑电压(本例中为 3.3V)需要连接到 MOSFET 的源极,而高电平逻辑电压(本例中为 5V)必须连接到 MOSFET 的漏极引脚。第二个条件是,MOSFET 的栅极需要连接到低压电源(本例中为 3.3V)。

双向逻辑电平转换器的仿真

使用仿真结果可以理解逻辑电平转换器电路的完整工作原理。正如您在下面的 GIF 图像中看到的,在高电平到低电平的逻辑转换期间,逻辑输入引脚在 5V 和 0V(地)之间转换,逻辑输出为 3.3V 和 0V。

同样,在低电平到高电平转换期间,3.3V 和 0V 之间的逻辑输入被转换为 5V 和 0V 的逻辑输出,如下图 GIF 图像所示。

逻辑电平转换器电路工作

满足这两个条件后,电路工作在三种状态。状态如下所述。

当低端处于逻辑 1 或高状态 (3.3V) 时。

当低端处于逻辑 0 或低状态 (0V) 时。

当高端状态从 1 变为 0 或从高变为低(5V 到 0V)

当低端为高时,即 MOSFET 的源极电压为 3.3V,由于未达到 MOSFET 的 Vgs 阈值点,MOSFET 不导通。此时 MOSFET 的栅极为 3.3V,MOSFET 的源极也为 3.3V。因此,Vgs 为 0V。MOSFET 关闭。逻辑 1 或低端输入的高状态通过上拉电阻 R2 在 MOSFET 的漏极侧反射为 5V 输出。

在这种情况下,如果 MOSFET 的低端将其状态从高电平变为低电平,则 MOSFET 开始导通。源为逻辑 0,因此高端也变为 0。

以上两个条件成功地将低压逻辑状态转换为高压逻辑状态。

另一种工作状态是 MOSFET 的高端将其状态从高变为低。这是漏极衬底二极管开始导通的时间。MOSFET 低端被下拉至低电压电平,直到 Vgs 越过阈值点。低压部分和高压部分的总线在同一电压电平下都变低了。

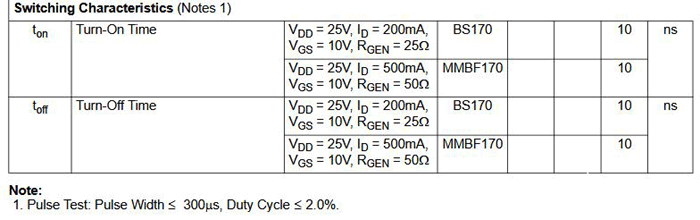

转换器的开关速度

设计逻辑电平转换器时要考虑的另一个重要参数是转换速度。由于大多数逻辑转换器将用于 USART、I2C 等通信总线之间,因此逻辑转换器的切换速度必须足够快(转换速度)以匹配通信线路的波特率。

转换速度与 MOSFET 的开关速度相同。因此,在我们的案例中,根据 BS170 数据表,MOSFET 的开启时间和 MOSFET 的关闭时间如下所述。因此,为您的逻辑电平转换器设计选择正确的 MOSFET非常重要。

所以我们这里的 MOSFET 需要 10nS 开启和 10nS 关闭,这意味着它可以在一秒钟内开启和关闭 10,00,000 次。假设我们的通信线路以每秒 115200 位(波特率)的速度运行,那么这意味着它在一秒钟内仅打开和关闭 1,15,200 位。所以我们也可以很好地使用我们的设备进行高波特率通信。

测试您的逻辑转换器

测试电路需要以下组件和工具 -

具有两种不同电压输出的电源。

两个万用表。

两个触觉开关。

用于连接的电线很少。

修改原理图以测试电路。

在上面的示意图中,引入了两个额外的触觉开关。此外,还连接了一个万用表来检查逻辑转换。通过按下 SW1,MOSFET 的低端将其状态从高电平变为低电平,逻辑电平转换器作为低压到高压逻辑电平转换器工作。

另一方面,通过按下SW2,MOSFET的高端将其状态从高变为低,并且逻辑电平转换器作为高压到低压逻辑电平转换器工作。

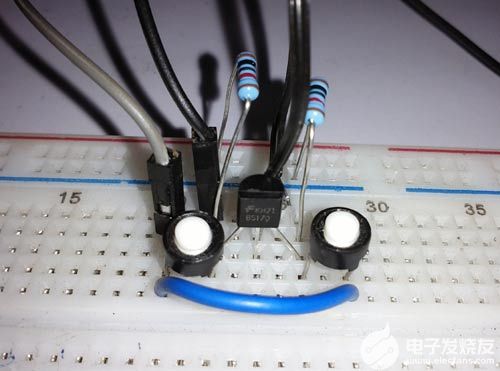

该电路在面包板上构建并经过测试。

上图显示了 MOSFET 两侧的逻辑状态。两者都处于逻辑 1 状态。

逻辑电平转换器的局限性

该电路当然有一些限制。这些限制高度依赖于MOSFET 的选择。该电路可使用的最大电压和漏极电流取决于 MOSFET 的规格。此外,最小逻辑电压为 1.8V。由于 MOSFET 的 Vgs 限制,低于 1.8V 的逻辑电压将无法正常工作。对于低于 1.8V 的电压,可以使用专用的逻辑电平转换器。

重要性和应用

正如介绍部分所讨论的,数字电子设备中不兼容的电压电平是接口和数据传输的问题。因此,需要电平转换器或电平转换器来克服电路中与电压电平相关的误差。

由于电子市场中广泛的逻辑电平电路以及不同电压电平的微控制器的可用性,逻辑电平转换器具有令人难以置信的用例。一些基于I2C、UART 或音频编解码器工作的外围设备和传统设备需要电平转换器来与微控制器进行通信。

流行的逻辑电平转换器 IC

有很多厂商提供逻辑电平转换的集成解决方案。流行的 IC 之一是MAX232。它是最常见的逻辑电平转换器 IC 之一,可将微控制器逻辑电压 5V 转换为 12V。RS232 端口用于在带有微控制器的计算机之间进行通信,需要 +/-12V。我们之前已经使用MAX232 与 PIC和其他一些微控制器来连接微控制器与计算机。

根据极低电压电平转换、转换速度、空间、成本等,也存在不同的要求。

SN74AX也是德州仪器 ( Texas Instruments) 流行的双向电压电平转换器系列。该细分市场中有许多 IC 提供单比特到 4 位电源总线的转换以及附加功能。

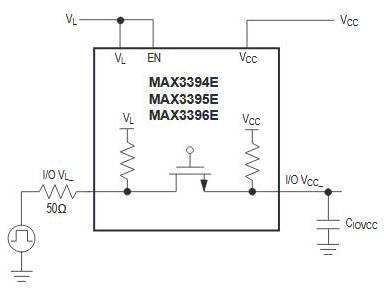

另一种流行的双向逻辑电平转换器 IC 是MaximIntegrated的MAX3394E。它使用与 MOSFET 相同的转换拓扑。引脚图可以在下图中看到。该转换器支持单独的使能引脚,可以使用微控制器进行控制,这是一项附加功能。

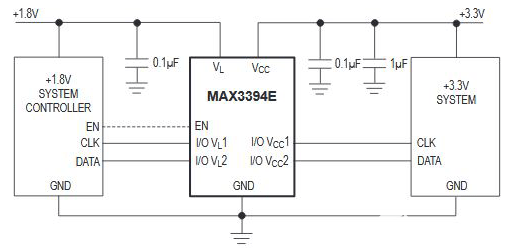

上述内部结构显示了相同的MOSFET 拓扑结构,但具有 P 沟道配置。它具有许多额外的附加功能,例如I/O 和 VCC 线路上的 15kVESD 保护。典型示意图如下图所示。

上面的示意图显示了将 1.8V 逻辑电平转换为 3.3V 逻辑电平的电路,反之亦然。可以是任何微控制器单元的系统控制器也控制着 EN 引脚。

审核编辑:汤梓红

-

ADG3300 1.15 V至5.5 V低压、8通道双向逻辑电平转换器技术手册2025-05-16 1279

-

MAX14611 4通道双向逻辑电平转换器技术手册2025-05-15 1194

-

双向逻辑电平转换器电路图分享2024-02-19 6554

-

ADG3308/ADG3308-1:低压,1.15 V至5.5 V,8通道双向逻辑电平转换器产品手册2021-04-27 751

-

ADG3301:低压1.15 V至5.5 V,单通道双向逻辑电平转换器产品手册2021-04-22 895

-

digilent逻辑电平转换器介绍2019-11-29 2934

-

怎样用双向逻辑电平转换器连接具有不同最大电压的MCU和模块2019-08-03 8565

-

智能手机的逻辑电平转换方案2018-10-10 3198

-

EasyEDA硬件开源项目——逻辑水平转换器(双向)2016-01-07 4255

-

美信MAX14611四通道双向逻辑电平转换器2012-04-23 5122

-

MAX14569 双对单向逻辑电平转换器2010-10-08 1096

全部0条评论

快来发表一下你的评论吧 !