verilog基础之规范化参数定义parameter

FPGA/ASIC技术

描述

采用parameter可以让程序变得可维护性,所以在verlog中,尽量在有数据可能发生变动的地方,设置为parameter,以免以后又从头开始更改。

parameter经常用于定义数据位宽,定义时间延迟,在模块和实例引用时,可以通过参数传递,改变被引用的模块。因此我们尽量把所有的可能变动的参数设置在顶层,一眼明了,方便日后维护。

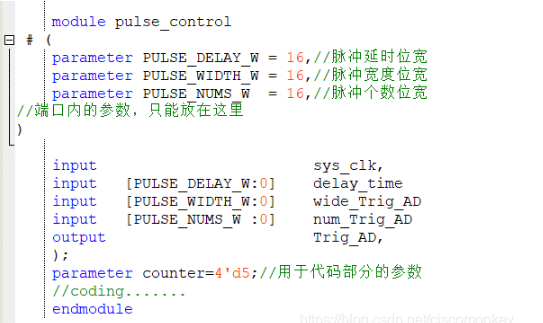

端口参数与模块内部参数

本module内有效的定义,可用于参数传递;

如果在模块内部定义时无法进行参数传递,

参数传递

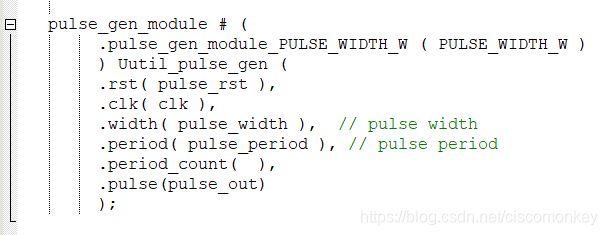

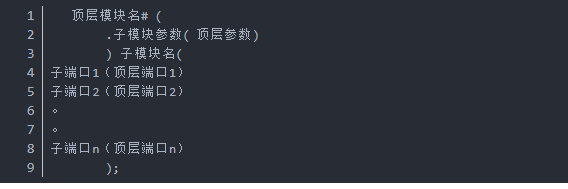

参数传递经常用于顶层的参数传递给子模块,这样我们只需要关注顶层实体的内容,把子模块的内容当做一个黑箱子即可,这也是非常实用的。

可以看到参数传递和例化是非常继续相似的,

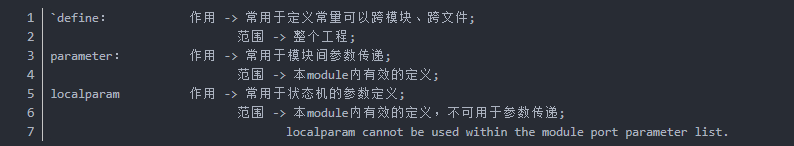

众说parameter、define、localparam的区别

defparam

defparam这个单独拿出来说一下,其实这个参数,个人觉得意义不大,因为你用parameter参数实例化就可以很好的解决问题,defparam用于重定义参数的数,可以通过

defparam 顶层.子模块名1.子模块名2=XXX

这样的语法格式更改,从而实现专门针对某一个子模块更改,这样有助于例化了多个相同的子模块,但我只更改一个子模块的问题。!

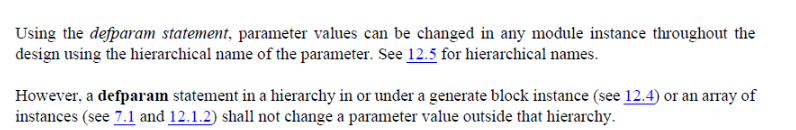

我们来一起看看官方文档IEEE verilog 2005

defparam的语法我们就去亲自查阅官方语法!这样才能有收货。

这段说了,defparam适用于改变指定层次模块下的参数,不影响其他模块的参数。

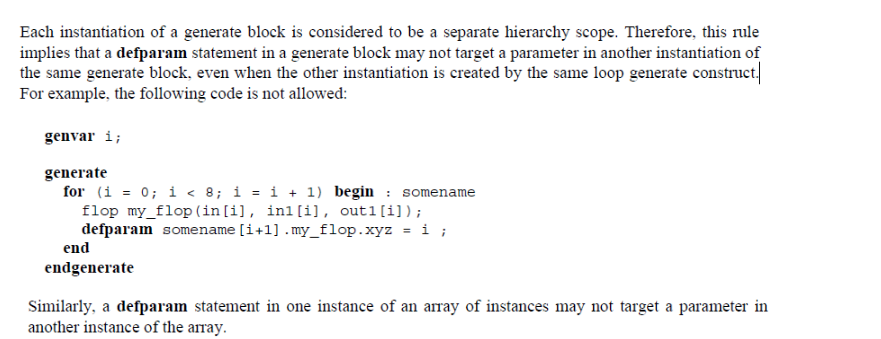

这段话也再次说明了,即使是使用相同的子模块实例化生成的模块,也不会受影响,defparam只针对指定路径下的参数更改。

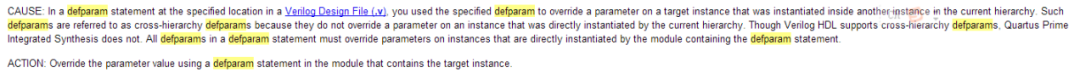

defparam目前所有综合工具都不支持综合,所以仅仅用于仿真。

审核编辑 :李倩

-

工器具规范化使用2010-11-18 1968

-

Verilog中parameter和define的区别2013-04-25 8814

-

关于发帖标题规范化管理公告2014-11-04 5235

-

Verilog语法基础讲解之参数化设计2017-10-21 2400

-

Verilog HDL代码书写规范2017-12-08 9996

-

如何用参数化加法器树编写Verilog2019-04-25 3422

-

代码规范化如何学习,单片机也要求规范化吗?2023-10-12 456

-

一种创新的无监督文本规范化系统2017-12-15 939

-

数据库-关系规范化的详细资料介绍,为什么要对进行关系的规范化?2018-09-05 3128

-

浅析FPGA规范化的重要性2018-10-09 3754

-

FPGA设计关于Verilog编码的12规范2020-11-24 5222

-

怎么样才能让Java代码编写更规范化2021-08-27 4295

-

使用NVIDIA NeMo进行文本规范化和反向文本规范化2022-10-11 3260

-

verilog语言编写规范2022-11-23 2154

-

IC设计之Verilog代码规范2023-08-17 2748

全部0条评论

快来发表一下你的评论吧 !