Verilog中clk为什么要用posedge,而不用negedge

描述

取某个信号的上升沿或下降沿信号

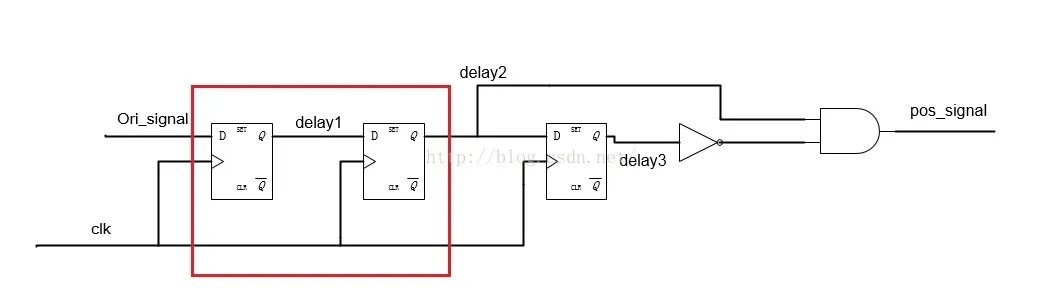

取一个信号的上升沿或下降沿信号,可以通过将信号delay后,然后将原信号和delay信号,通过不同的与非操作,获取上升沿信号或下降沿信号: 阶段一: reg delay; // delay信号 always @ ( posedge clk or negedge rstn ) if( !rstn ) delay <= 0; else delay <= orig; // orig是原信号 wire pos_signal = orig && ( ~delay ); // 原信号上升沿位置处产生的pulse信号 wire neg_signal = ( ~orig ) && delay; // 原信号下降沿位置处产生的pulse信号 阶段二: 上述操作会存在亚稳态问题,并且得到的上升沿信号pos_signal和下降沿信号neg_signal无法被原采样时钟clk采样。正确做法是,先将原信号用采样时钟delay 2次(打两拍),得到和采样时钟同时钟域的信号delay2,然后再按上述方法获取上升沿和下降沿信号,这时得到的上升沿或下降沿就可以被原采样时钟采样。 例句如下: reg ori_signal;// 需取上升沿或下降沿的原信号 reg delay1; reg delay2; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay1 <= 0; else delay1 <= ori_signal; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay2 <= 0; else delay2 <= delay1; // delay2 已与clk同域 reg delay3; always @ ( posedge clk or negedge rstn ) if( !rstn ) delay3 <= 0; else delay3 <= delay2; wire pos_signal = delay2 && ( ~delay3 ); // 原信号上升沿位置处产生的pulse信号 wire neg_signal = ( ~delay2 ) && delay3; // 原信号下降沿位置处产生的pulse信号 上升沿电路如下: 注意:前两个触发器的运用就是起同步作用,将某个信号同步到采样时钟域,以后要重点注意使用。

阶段三:

用阶段二的语句会比较繁琐,可以用下述语句简化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信号

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信号下降沿位置处产生的pulse信号

注意:前两个触发器的运用就是起同步作用,将某个信号同步到采样时钟域,以后要重点注意使用。

阶段三:

用阶段二的语句会比较繁琐,可以用下述语句简化:

reg[2:0] delay;

always @ ( posedge clk or negedge rstn )

if( !rstn )

delay <= 0;

else

delay <= { delay[1:0], ori_signal} ; // ori_signal是原信号

wire pos_signal = delay[1] && ( ~delay[2] ); // 原信号上升沿位置处产生的pulse信号

wire neg_signal = ( ~delay[1] ) && delay[2]; // 原信号下降沿位置处产生的pulse信号

Verilog中clk为什么要用posedge,而不用negedge

posedge是上升沿,电平从低到高跳变

negedge是下降沿,电平从高到低跳变

对于典型的counter逻辑

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 24'd0;//十进制0

else if(counter < led_time) begin

flag_counter = 1'b0;

counter <= counter + 1'b1;

end

else begin

counter <= 24'd0;

flag_counter = 1'b1;

end

end

clk为什么要用posedge,而不用negedge呢?

一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。

在ModelSim仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用posedge,则整个系统的节拍都按照clock上升沿对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升沿到上升沿肯定是一个时钟周期,但是上升沿到下降沿却很可能不是半个周期。这都会出现问题。

FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫Global CLK

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ISE12.1 那个verilog text fixture 怎么写?2014-03-30 2876

-

verilog描述异步置0,异步置1功能的D触发器2014-04-04 15786

-

verilog快速掌握之程序设计及程序下载2015-05-22 5408

-

verilog中的阻塞和非阻塞2015-09-13 5053

-

FPGA verilog 中调用的task 的问题2016-01-10 11931

-

如何测试写过的verilog功能?2016-02-24 3599

-

新手请教一个verilog代码的问题,就一个命令。2016-07-31 3076

-

关于Verilog中always块敏感信号的疑问与讨论。2017-09-18 10260

-

可以在相同的总块中使用时钟的posedge和negedge2018-10-30 3671

-

初学者求助 Verilog 的 if 语句2019-04-01 2690

-

Verilog hdl教程实例2010-02-09 705

-

Verilog中四个基础的时序分析2021-08-25 5510

-

FPGA设计之Verilog中clk为什么要用posedge而不用negedge?2023-10-10 7818

全部0条评论

快来发表一下你的评论吧 !