利用同步fifo实现对输入序列的检测

电子说

描述

今天继续为大家解析联发科技数字IC设计岗的笔试题。

16、【简答题】请用Verilog写出以下逻辑

Interface signals如下:

input clk_ck;

input rst_b(async reset);

input req_in;

output req_in_ack;

input [31:0] data_in;

output data_out_vld;

output [31:0] data_out;

模块功能需求如下:

1)模块名为:filter_data_store

2)当req_in和req_in_ack都为高时,说明本模块有能力接收data_in的数据;

3)在data_in的数据中找到特殊字符32’hA1B9_0000,特殊字符前的数据全部丢弃,特殊字符后的资料全部收下来;

4)当sync_fifo为非空的时候,将数据读出放到data_out上,并用data_out_vld指示数据的有效性。(15分)

解析:本题目主要考察了利用同步fifo实现对输入序列的检测

本题是一道关于同步fifo应用的题目,遇到这种类型的题目首先要根据题目中的要求逐条分析,然后依次在草稿纸上画出大致的模块框图、波形图,再编写RTL代码。

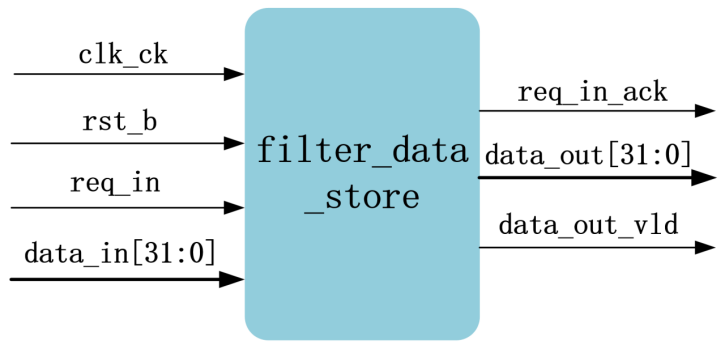

首先根据Interface signals需求1携带的信息,绘制出的模块框图如下所示:

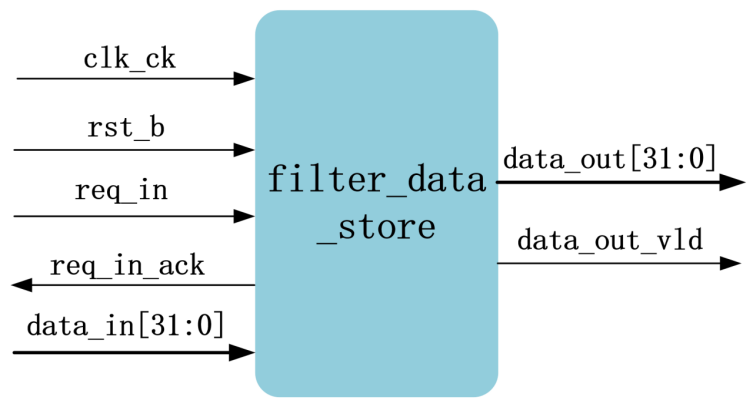

然后根据需求2改进模块框图如下:

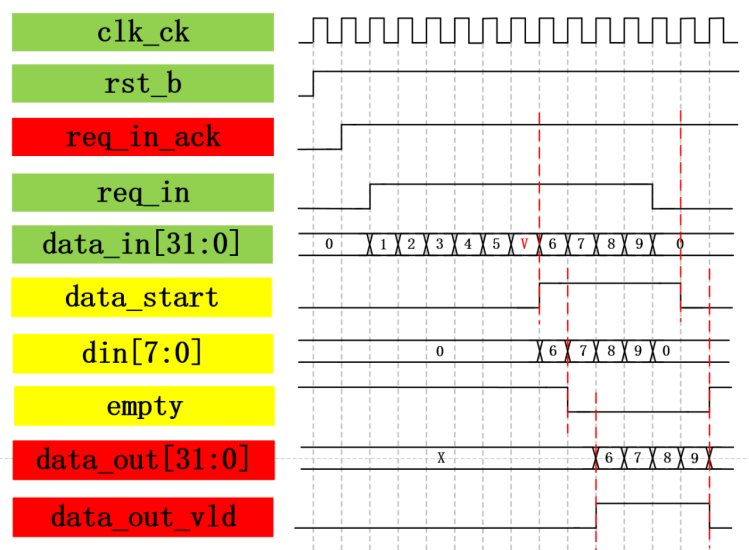

然后绘制波形图如下所示:

filter_data_store模块的HDL代码如下所示:

//------------------

01 module filter_data_store(

02 inputwire clk_ck,

03 inputwire rst_b,

04 inputwire req_in,

05 inputwire[31:0]data_in,

06

07 outputreg req_in_ack,

08 outputwire[31:0]data_out,

09 outputreg data_out_vld

10 );

11

12 reg data_start;

13 reg data_start_reg;

14 wire [31:0] dout;

15 wire full;

16 wire empty;

17

18 always@(posedge clk_ck or negedge rst_b)

19 if(!rst_b)

20 req_in_ack <= 1'b0;

21 else if(full == 1'b0)

22 req_in_ack <= 1'b1;

23 else if(empty == 1'b1)

24 req_in_ack <= 1'b0;

25

26 always@(posedge clk_ck or negedge rst_b)

27 if(!rst_b)

28 data_start <= 1'b0;

29 else if(req_in ==1'b1 && req_in_ack == 1'b1 && data_in == 32'hA1B9_0000)

30 data_start <= 1'b1;

31 else if(req_in == 1'b0)

32 data_start <= 1'b0;

33

34 always@(posedge clk_ck or negedge rst_b)

35 if(!rst_b)

36 data_start_reg <= 1'b0;

37 else

38 data_start_reg <= data_start;

39

40 //-------sync_fifo_inst-------

41 sync_fifo sync_fifo_inst(

42 .clk_ck(clk_ck), //input clk_ck

43 .rst_b (rst_b), //inputrst_b

44 .wr_en (data_start), //input wr_en

45 .din (data_in), //input [31:0] din

46 .rd_en (~empty), //input rd_en

47

48 .dout (dout), //output [31:0] dout

49 .full (full), //output full

50 .empty (empty) //output empty

51 );

52

53 assign data_out = dout;

54

55 always@(posedge clk_ck or negedge rst_b)

56 if(!rst_b)

57 data_out_vld <= 1'b0;

58 else if(data_start == 1'b0 && data_start_reg == 1'b1)

59 data_out_vld <= 1'b0;

60 else if(data_start_reg == 1'b1)

61 data_out_vld <= 1'b1;

62

63 endmodule

//----------------还需要一个同步fifo模块,如果有时间建议自己用逻辑手写一个同步fifo。同步fifo模块的HDL代码如下所示://----------------01 module sync_fifo(02 input wire clk_ck,03 input wire rst_b,04 input wire wr_en,05 input wire[31:0]din,06 input wire rd_en,07 08 output wire[31:0] dout,09 output wire full,10 output wire empty11 );12 13 reg[4:0] wr_cnt;14 reg[4:0] rd_cnt;15 reg[31:0] mem [15:0];16 reg[31:0] dout_r;17 18 wire[3:0] wr_p;19 wire[3:0] rd_p;20 21 assign wr_p = wr_cnt[3:0];22 assign rd_p = rd_cnt[3:0];23 assign dout = dout_r;24 assign full=(wr_cnt[4]!=rd_cnt[4]&&wr_p == rd_p) ? 1'b1 : 1'b0;25 assign empty = (wr_cnt == rd_cnt) ? 1'b1 : 1'b0;26 27 always@(posedge clk_ck or negedge rst_b)28 if(!rst_b)29 begin30 wr_cnt <= 5'd0;31 rd_cnt <= 5'd0;32 end33 else34 begin35 if(!full && wr_en) 36 begin37 mem[wr_p] <= din;38 wr_cnt <= wr_cnt + 1'b1;39 end40 if(!empty && rd_en)41 begin42 dout_r <= mem[rd_p];43 rd_cnt <= rd_cnt + 1'b1;44 end45 end46 47 endmodule//------------------Testbench如下所示://------------------

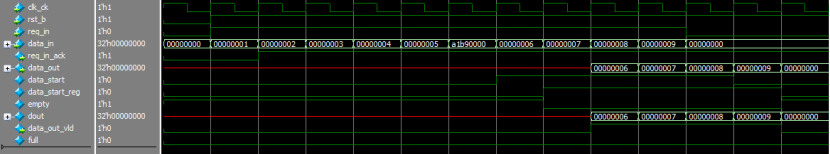

01 moduletb_filter_data_store();02 03 reg clk_ck;04 reg rst_b;05 reg req_in;06 reg [31:0]data_in;07 08 wire req_in_ack;09 wire [31:0]data_out;10 wire data_out_vld;11 12 //初始化系统时钟、全局复位13 initialbegin14 clk_ck = 1'b1;15 rst_b <= 1'b0;16 req_in <= 1'b0;17 data_in <= 32'h0000_0000;18 #2019 rst_b <= 1'b1;20 @(posedge clk_ck)21 req_in <= 1'b1;22 data_in <= 32'h0000_0001;23 @(posedge clk_ck)24 data_in <= 32'h0000_0002;25 @(posedge clk_ck)26 data_in <= 32'h0000_0003;27 @(posedge clk_ck)28 data_in <= 32'h0000_0004;29 @(posedge clk_ck)30 data_in <= 32'h0000_0005;31 @(posedge clk_ck)32 data_in <= 32'hA1B9_0000;33 @(posedge clk_ck)34 data_in <= 32'h0000_0006;35 @(posedge clk_ck)36 data_in <= 32'h0000_0007;37 @(posedge clk_ck)38 data_in <= 32'h0000_0008;39 @(posedge clk_ck)40 data_in <= 32'h0000_0009;41 @(posedge clk_ck)42 req_in <= 1'b0;43 data_in <= 32'h0000_0000;44 req_in <= 1'b0;45 #100046 $finish;47 end48 49 always #10 clk_ck = ~clk_ck;50 51//------filter_data_store_inst-------52 filter_data_store filter_data_store_isnt(53 .clk_ck(clk_ck ), //input clk_ck 54 .rst_b (rst_b ), //input rst_b 55 .req_in(req_in ), //input req_in 56 .data_in (data_in ), //input [31:0] data_in 57 58 .req_in_ack(req_in_ack ), //output req_in_ack 59 .data_out (data_out ), //output [31:0] data_out 60 .data_out_vld(data_out_vld) //output data_out_vld 61 );62 63 endmodule //----------------用QuestaSim仿真出的波形如下所示:

审核编辑:汤梓红

-

握手型接口的同步FIFO实现2023-12-04 1680

-

利用AD7616灵活的可编程序列器和突发模式实现准同步采样2023-11-24 1446

-

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用2023-10-18 2916

-

同步FIFO设计分析2023-09-11 1392

-

基于Verilog的同步FIFO的设计方法2023-08-31 1654

-

FPGA学习-序列检测器2023-08-29 2786

-

同步FIFO设计详解及代码分享2023-06-27 3284

-

基于寄存器的同步FIFO2023-06-14 1666

-

同步FIFO之Verilog实现2022-11-01 3126

-

利用ISE的SDRAM设计的FIFO实验2021-08-04 958

-

如何利用FPGA实现准单输入调变序列生成器的设计?2021-04-29 1442

-

基于CAZAC序列的OFDM时频同步方案解析2020-12-17 4122

-

利用VHDL语言和格雷码对地址进行编码的异步FIFO的设计2019-08-02 3074

-

基于VHDL和FPGA的非对称同步FIFO设计实现2011-01-13 2305

全部0条评论

快来发表一下你的评论吧 !