X态产生的原因主要分为哪几种情况

电子说

描述

在Verilog中,IC设计工程师使用RTL构造和描述硬件行为。但是RTL代码中的一些语义,并不能够准确地为硬件行为建模。Verilog中定义了4种不同的逻辑值:1、0、X和Z,1和0是真实存在的逻辑电平,Z表示高阻态,X表示未知态。

X态的存在使得仿真结果要么太过于乐观,要么太过于悲观。因此X态如何通过RTL级和门级仿真模型中的逻辑进行传播的,是需要特别关注的。为此,还产生了两种观念,X-optimism和X-pessimism。前者将X值转换为0或1,后者将X值一直传播出去。

X态产生的原因主要分为以下几种情况:

四值变量、寄存器和锁存器未初始化

模块输入端口未连接

总线争用

超出范围的位选择和数组索引

setup/holdtiming violation

testbench中注入X态

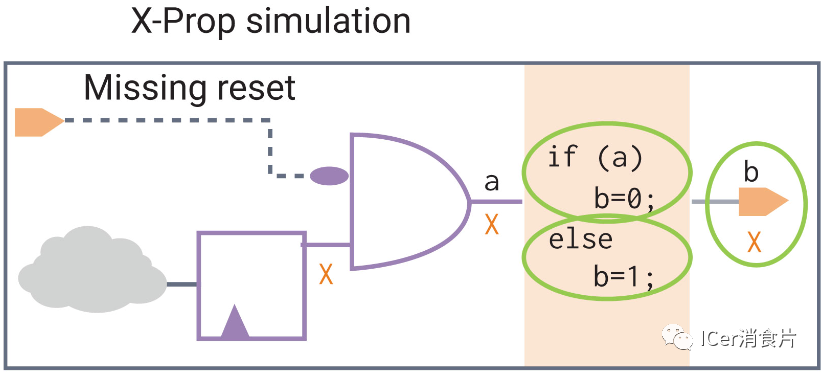

VCS对于RTL仿真提供了支持X-Propagation的选项,因为RTL仿真偏向于乐观,导致一些X态传播的bug,无法在正常的RTL仿真阶段发现。但是在Gate-level仿真时会暴露出来,因为Gate-level仿真也更接近实际硬件行为。

我们知道越早的发现bug,所消耗的成本也越低的,故VCS的X-Propagation功能可以更接近Gate-level的X态传播行为,是一种在后仿之前debug的低成本仿真策略。

通常使用带xprop的仿真选项为:

vcs -xprop[=tmerge|xmerge|xprop_config_file]

[-xprop=flowctrl]

[-xprop=nestLimit=

other_vcs_options

这里就不深入介绍各个选项了,而是介绍三种merge mode:

vmerge mode: 就是Verilog协议规定的X态处理行为;

tmerge mode: 更接近Gate-level仿真,也就是实际硬件行为;

xmerge mode: 相比tmerge mode,对于X态的处理更悲观;

下面举几个实例来看看这三种mode的具体区别

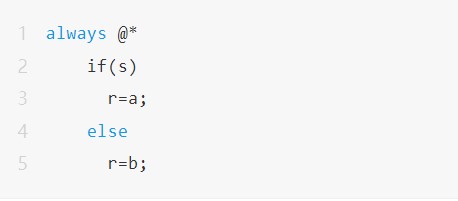

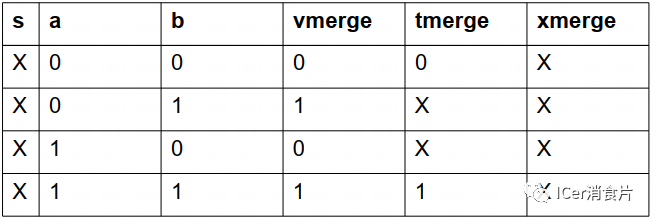

if语句

在vmerge模式下,使用标准的HDL模拟语义。当控制信号s未知时,输出信号r总是被赋给else语句的值。此时r的值与信号b相同。

在tmerge模式下,当控制信号s未知时,如果输入信号a和b 同,则r的值与a(或b) 相同。如果a和b不相同,则r的值为X。

在xmerge模式下,当控制信号s未知时,输出信号r的值始终为X。

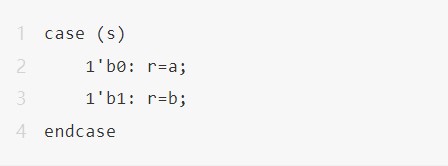

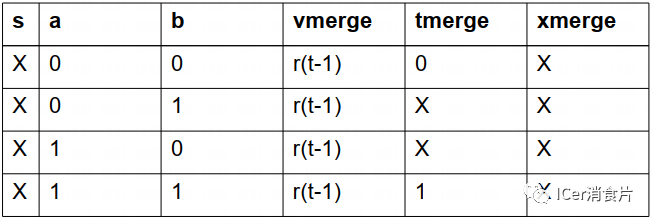

case语句

在vmerge模式中,使用标准的HDL模拟语义。当控制信号s未知时,输出信号r的值与执行case语句之前保持一致。

在tmerge模式中,当控制信号s未知时,如果a和b相同,r的合并和最终值与a和b 相同。如果a和b不相同,r的合并和最终值为X。

在xmerge模式下,当控制信号s未知时,输出信号r的值始终为X。

边沿敏感表达式

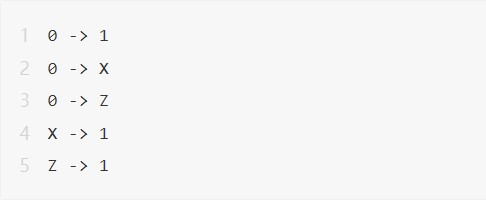

在标准的 Verilog 中,对于时钟信号中以下值的变化会触发上升沿转换:

如果X被认为是0或1值,那么在 0 -> X 转换中,X可能表示0值,这表示没有转换。X可以表示1值,此时表示上升沿。Xprop仿真考虑了这两种行为并合并了结果。

以下为一个低有效复位的D触发器示例:

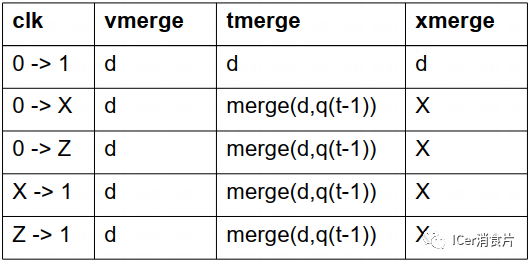

在三种模式中,如果时钟信号clk从0变成1,即一个上升沿触发,D触发器的输出信号q被赋值为输入信号d。

对于其余四种时钟信号的变化,vmerge模式中,输出信号q被赋值为输入信号d;xmerge模式中,输出信号q被赋值为X;tmerge模式中,q端的结果是当前拍d端和上一拍q端值得merge的结果,如果两者不同,则当前拍锁存X。

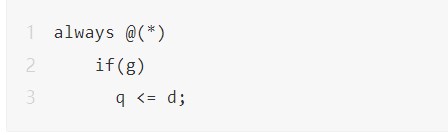

latch

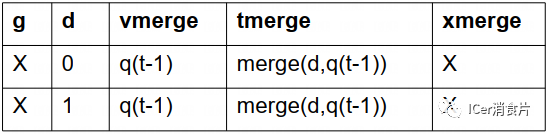

在vmerge模式下,当控制信号g未知时,输出信号q的值不变。

在tmerge模式下,当控制信号g未知时,分配给q的合并值取决于q和d的值。

在xmerge模式下,当控制信号g未知时,输出信号q的值始终为X。

当xprop仿真过程中出现X态报错时,需要看波形以具体分析是寄存器没有初始化值,存在X态导致的,还是代码逻辑中存在问题导致的。

审核编辑:刘清

-

逻辑分析仪的主要特点有哪些?可分为哪几种类型?2021-04-14 2510

-

显示器接口分为哪几种?如何去保护?2021-06-01 1551

-

什么是功放?功放分为哪几种?2021-06-02 5867

-

电路基础部分知识包括哪些?滤波电路主要分为哪几种?2021-06-22 3101

-

请问什么是波导天线?波导天线分为哪几种?2021-06-30 3129

-

ARM产品可分为哪几类?ARM处理器主要分为哪几种?2021-07-01 3408

-

计时器主要分为哪几种?其工作原理是什么?2021-07-02 4420

-

无刷电机的位置检测器主要分为哪几种?求解2021-07-26 1587

-

UPS的电池寿命主要受到哪几种因素的影响?2009-11-06 2314

-

电容的用途主要有哪几种?2009-11-27 1579

-

SMT元器件有哪几种类型2020-11-27 3295

-

在哪几种情况下会造成伺服电机抖动2022-02-22 2795

-

消防应急灯具按用途分为哪几种?2023-08-18 7305

-

以太网接口分为哪几种接口?车载以太网接口分为哪几种接口?2023-08-31 6830

-

降噪是什么原理 降噪方法分为哪几种2024-03-14 14276

全部0条评论

快来发表一下你的评论吧 !