NC-FET技术解决方案

描述

众所周知,互补金属氧化物半导体 (CMOS) 晶体管存在缩放问题。随着 CMOS 场效应晶体管 (FET) 变得更小,它们的功率效率会降低,进而更容易受到自热的影响。当由于功率耗散导致的发热变得如此之大以致 CMOS-FET 器件无法有效运行时,这将成为一个问题。这个概念被称为玻尔兹曼暴政,它由 MOSFET 在 300k 时 60 mV/dec 的亚阈值斜率 (SS) 的热离子极限定义。这种现象导致工作电压下限,最终限制了标准 FET 的功耗。

由于已知 CMOS FET 技术的这种局限性,因此一直在努力开发解决该问题的方法。这些潜在解决方案的一些示例包括隧道 FET、自旋 FET、纳米机电 FET、相位 FET,以及最近的负电容 FET (NC-FET)。正如题为“使用负电容为低功率纳米级器件提供电压放大”的技术论文中提出的那样,NC-FET 的设计是用指定厚度的铁电绝缘体代替标准绝缘体。

该解决方案可以创建一个升压变压器,增加栅极电压,并导致 SS 值低于 60 mV/dec。这样的解决方案允许更低电压的 FET 操作,这与更低的功耗和更高的器件效率相吻合。这个提议的解决方案,正如最初提供的那样,不涉及 FET 物理操作的任何内在变化,并且仅能够在较低的电源电压下达到导通电流阈值。

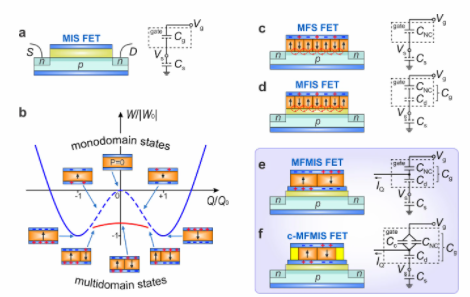

图 1上图展示了基于铁电的 NC-FET 的稳定性和可行性。资料来源:施普林格自然

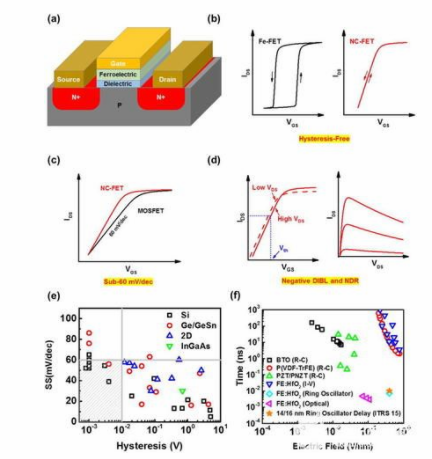

无论 NC-FET 的理论多么简单,自 2008 年最初提出 NC-FET 以来,开发和建模这些设备的实际情况远没有那么简单。看来,造成这种情况的主要原因之一是最初提出的 NC-FET 要求铁电绝缘体的负电容状态稳定在单畴状态,准静态 NC 模型。与具有迟滞 IV 特性的铁电 FET (Fe-FET) 不同,NC-FET 没有这种特性(图 2)。

图 2 NC-FET 在 MOSFET 的现有栅极氧化物中添加了一层薄薄的铁电 (FE) 材料。资料来源:AIP 出版社

此外,对于 NC-FET,总栅极电容仍然为正,而在 Fe-FET 中,总栅极电容为负。本质上,NC-FET 要求 IV 特性与扫描频率和扫描电压无关且无滞后。

NC-FET 设计中的一个挑战是太厚的铁电 (FE) 层会导致负差分电阻 (NDR),这可能会降低 NC-FET 器件的性能。这是由于更大厚度的 FE 材料允许更高的界面电场强度和更大的界面/体积陷阱。这些 NDR 效应也会导致器件的滞后,并且必须在 NC-FET 的未来发展中加以解决。幸运的是,真正的 NC-FET 还表现出漏极感应势垒上升 (DIBR),这实际上会导致关断电流减小,这有利于 NC-FET 的低电源电压操作。

剩下的就是开发用于制造 NC-FET 的 CMOS 兼容工艺、稳定和可逆的 NC-FET 技术,以及可以扩展到 2.5 nm 至 5 nm 工艺节点的 NC-FET。

Jean-Jaques (JJ) DeLisle是罗切斯特理工学院的电气工程专业毕业生 (MS),在模拟和射频研发以及设计工程出版物的技术写作/编辑方面拥有丰富的背景。他为 Planet Analog 撰写有关模拟和射频的文章。

-

深控技术NC程序管理系统:机加工行业智能化升级的工业物联网中枢2025-11-24 486

-

使用SiC FET替代机械断路器的固态解决方案2023-06-12 1509

-

基于Arm®技术的嵌入式控制解决方案分享2022-12-08 508

-

电子系统的浪涌管理和系统保护的解决方案2022-11-23 769

-

采用离散FET设计的EMI抑制技术2022-11-09 684

-

#硬声创作季 #FPGA Xilinx入门-16 亚稳态现象原理与解决方案-1水管工 2022-10-09

-

立体智慧仓储解决方案.#云计算学习电子知识 2022-10-06

-

Beacon的定位技术解决方案2018-12-06 3730

-

转基于FET1052-C核心板---移动支付解决方案2018-10-23 1379

-

基于Zigbee技术的智能家居解决方案2014-03-26 9603

-

ADAS技术解决方案与应用对比2013-01-07 4398

-

微型能源采集技术的关键应用问题及解决方案2011-09-29 3140

-

采用Sun StorEdge技术创建存储解决方案2009-11-13 3566

全部0条评论

快来发表一下你的评论吧 !