systemverilog bins是如何去定义的

电子说

1.4w人已加入

描述

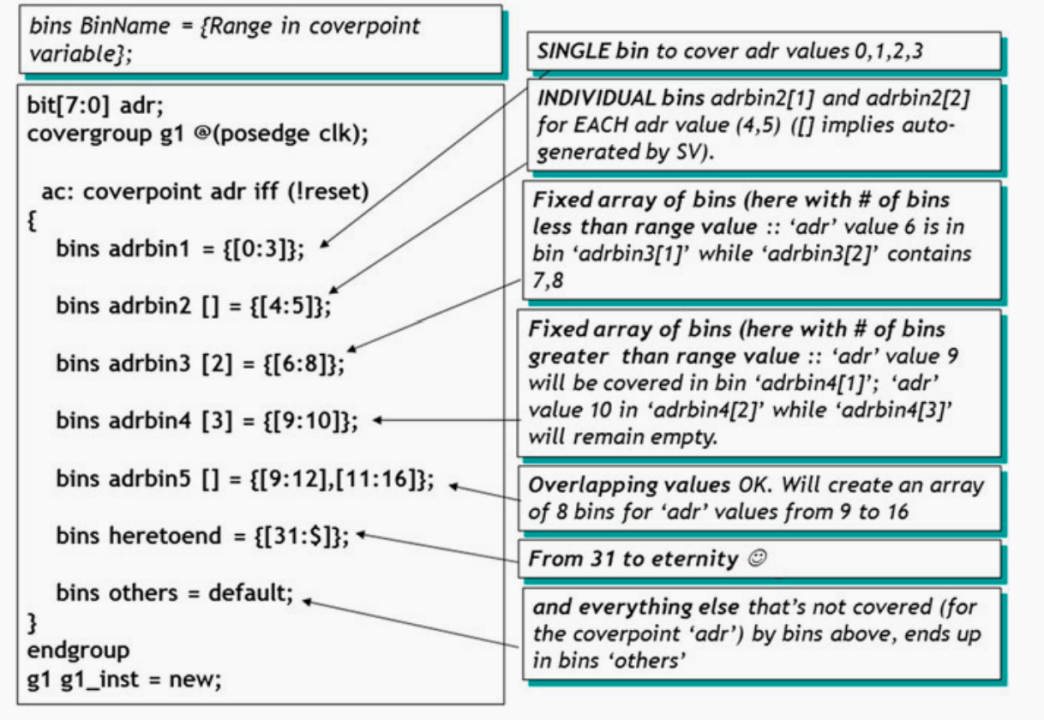

“bins”是在功能覆盖率coverpoint中收集设计特性用的。

功能覆盖率覆盖的就是一个个的coverpoint bins(不同的变量),对于一个8bit addr,那么默认的bins就是8‘h00~8’hFF,当然也可以显式地指定不同值之间的切换为一个bins。

从这个角度来理解,coverpoint bins非常容易理解,但是涉及到具体的应用还是会有很多问题需要考虑的。

例如,在下面的声明中,将创建多少个bins?

bins adrbin1 = {[0:3]};

16个、4个还是1个。

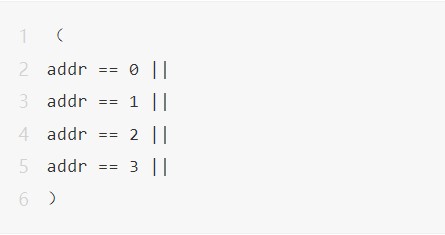

答案是1个bin,相当于覆盖了

注意上面的写法' bins adrbin1 '没有[]括号。换句话说,' bins adrbin1 '不会为' addr '值{[0:3]}自动创建4个bins,而是只创建1个bins来覆盖值' 0 ',' 1 ',' 2 ',' 3 '。

也就是说,只要覆盖了0~3其中的一个,这个coverpoint覆盖率就是100%

但是,如果你希望分别收集变量“adr”的每个值,该怎么办呢。应该按照下面的这种写法,加上“[]”

bins adrbin2[] ={[4:5]};

这时候会为4、5分别创建一个bins,只有4和5全部覆盖,这个coverpoint的覆盖率才是100%

在开发SV功能覆盖率模型时可能没有办法把所有的值都写满,这个时候可以利用符号“$”,很多语义下它都代表着无限大的意思。对于一个8bit addr变量

bins adr[] = {[31:$]}

就意味着显式地收集{[31:255]}

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ignore_bins和default两者之间有些什么细微差别呢?2023-07-14 3857

-

SystemVerilog里的regions以及events的调度2023-07-12 3118

-

从Verilog PLI到SystemVerilog DPI的演变过程2023-05-16 1770

-

SystemVerilog中的Shallow Copy2022-11-21 1589

-

怎样去使用SystemVerilog中的Static方法呢2022-11-18 1918

-

SystemVerilog中的struct2022-11-07 3480

-

SystemVerilog对硬件功能如何进行建模2022-03-30 2801

-

SystemVerilog有哪些标准?2021-06-21 1968

-

SystemVerilog的正式验证和混合验证2021-03-29 940

-

做FPGA工程师需要掌握SystemVerilog吗?2017-08-02 7105

-

round robin 的 systemverilog 代码2017-03-14 3747

-

systemverilog学习教程2015-04-01 8671

-

[启芯公开课] SystemVerilog for Verification2013-06-10 8964

-

SystemVerilog Assertion Handbo2009-07-22 1067

全部0条评论

快来发表一下你的评论吧 !