电力场效应管电路分析

电子说

描述

电力场效应管适用于1000KV以下的中小功率场合,主要指电力MOSFET,其采用多元集成的垂直导电结构,有V形槽导电的VVMOSFET和双扩散MOS结构的VDMOSFET,目前比较流行的是VDMOSFET,比较常用的是其中的N沟道增强型。增强型的含义是,当栅源电压Ugs超过开启电压Uth后,Ugs越大,漏源之间导通电阻Rds越小,导电能力越强;栅源之间隔着很薄的二氧化硅绝缘层,形成类似平板电容的寄生电容C,其中电场强度E=Ugs/d,间距d很小,对Ugs有格的要求,一般为10~15V,极限值为±20V,否则电场太强会击穿二氧化硅。电力MOS管多数用作开关管,工作在开关状态,即在截止区和非饱和区之间切换;通常说的输入阻抗极高,输入电流可忽略,是指直流静态特性。在栅极施加高频驱动脉冲时,充放电电流i=C*dUgs/dt ,频率越高,电流越大 ;对栅极输入电容充电为开通过程,放电为关断过程;栅极输入电容为皮法级的小容,充放电很快,MOS 管开关速度很快,工作频率是主流电力电子器件中最高的,可达100KHz以上。开关频率越高,充放电电流越大,所需驱动功率也越大。提高工作频率,有利于设备小型化。半导体变流技术离不开电感、电容和开关变压器,而电感、电容起作用的实质体现在感抗和容抗上,感抗XL=2兀fL,容抗 Xc=1/2兀fC,由此可见,提高频率等同于增加电感量和电容量,这样就可成倍地减小体积;由于能量转换速度加快,开关变压器容量和体积也大大减小。

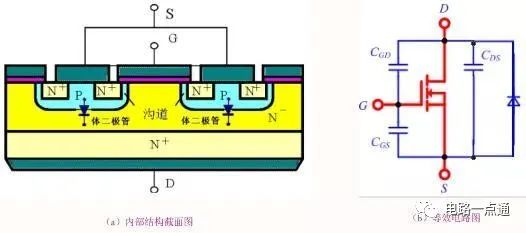

图一 N沟道增强型VDMOSFET

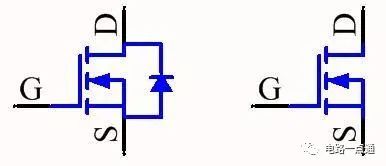

图二 电路图符号

图一为N沟通增强型VDMOSFET断面示意图及等效电路图,在电路图中一般使用图二所示的两种图形符号。图形符号中的箭头方向与反并联寄生二极管的方向是一致的。电力电子器件的损耗发热,是必须深刻理解的内容。对照图三所示的损耗示意图,分析损耗的组成。

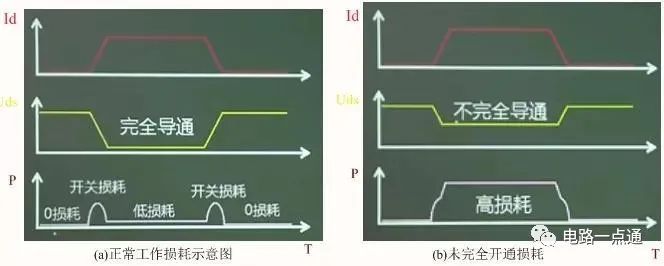

图三 损耗分析示意图

先看图三(a),断态损耗:功率MOSFET(P-MOS)关断时,漏极电流Id近视为零,漏、源极承受最大工作电压Uds,损耗P=Id*Uds=0; 通态损耗:Id达到最大工作电流,P-MOS完全导通,漏源之间电阻Rds达最小值,Uds=Id*Rds下降到很低,P=Uds*Id比较小,处于正常的低损耗发热状态;

开关损耗包括导通过程损耗和关断过程损耗。导通过程中,Id逐渐上开,Uds逐渐减小,Id*Uds之积形成损耗面积,面积与开通速度有关,开通越快,面积越小,损耗P也就越小;关断过程中,Id逐渐下降,Uds逐渐增大,关断越快,损耗面积越小。

看图三(b),在没有正确驱动P-MOS时,导致其未完全开通,此时Rds比较大,Uds没能下降到很低的值,在Id也比较大时,会形成巨大的通态损耗,使P-MOS过热损坏。

基于以上认知,下面以具体电路说明驱动电路的相关要求。为快速建立驱动电压,要求驱动电路输出电阻小,驱动电流足够大;由于关断时间一般都大于开通时间,关断时施加负驱动电压可减小关断时间和关断损耗;栅极串入几十欧小电阻,可抑制可能产生的驱动信号振荡。

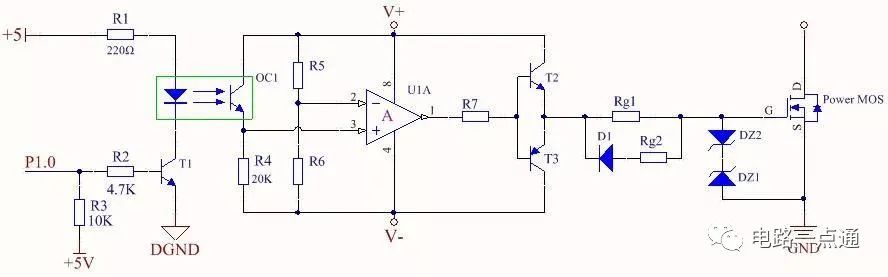

图四 光耦隔离推挽驱动电路

图四驱动电路中,光耦OC1起隔离传导干扰和电平转换作用;远放A构成比较器,用于驱动信号整形,使脉冲边沿更加陡峭;T2、T3构成互补推挽电路,共射输出,输出电阻小,任何时刻只有一个能导通。T2、T3不可接成共集电极输出,该结构在电压跳变过程中,会发生T1、T2同时导通的后果;D1、Rg2单独提供低阻放电回路,以进一步减小关断时间,D1需用快恢复二极管。控制器P1.0输出低电平时,比较器输出负电平,T3导通输出负驱动电压,栅极电容放电,MOS管快速关断;P1.0输出高电平时,比较器输出正电平,T2导通输出正驱动电压,栅极电容充电,MOS管快速开通。

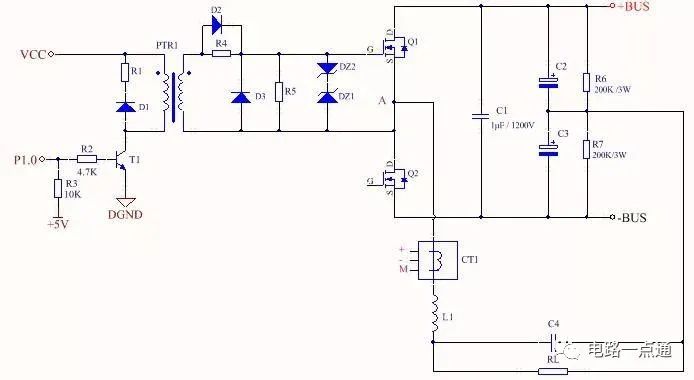

图五 脉冲变压器隔离驱动

在驱动如图五所示主电路时,随着低压侧Q2的截止与导通,A点的电位是浮动,即高压侧Q1管的源极电位是变动的,一般方法难以施加栅源驱动电压Ugs ,同时主电路的电压一般都比较高,难以保证驱动电路安全工作,在这种情形下,最好的办法是用脉冲变压器(PTR)进行隔离,PTR可以隔离一切电位,且能把确定的电位差传递到次级,即能保证栅源之间有合适的驱动电压,而不管S极电位如何变动,既解决了电位浮动问题,又实现了危险电压的隔离。对PTR的要求是:耦合电容要小,使之具有抗干扰能力;漏感小,瞬时传输功率高;体积要小,抗电强度高。在图五的PTR隔离驱动电路中,R1、D1起续流作用,防止反电势损坏T1;D2、D3用于脉冲整形,确保G极使用正脉冲快速充电;R4、R5提供放电回路;DZ1、DZ2起限制栅源电压的作用,使之不超过±20V,防止栅源之间的绝缘层被击穿。

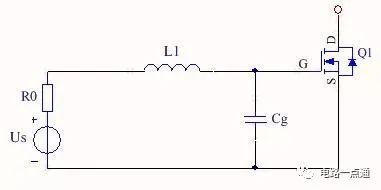

图六 驱动等效电路

任何驱动都可等效成图六所示的电路,其中R0为与栅极串联的驱动电路等效内阻,L1为细长弯曲铜箔或引线引起的寄生电感,Cg为栅极等效输入电容,它们构成了RLC串联电路。驱动脉冲中含有各种频率成份的信号分量,开通过程中,当某一频率与线路固有频率相同时,可能引起RLC电路的串联谐振现象,此时该频率信号的电流I达到最大值,当容抗Xc>>R0时,电容上的电压Uc=I*Xc有可能超出栅极极限电压,即使没有超出极限,也会引起驱动电压Ugs振荡,当Ugs在阈值电压Uth附近振荡时,会造成MOS管不能完全开通,反复进入高阻导通状态,引发极大损耗,发热严重;关断过程中,当R0很小时,会发生欠阻尼振荡,造成关断缓慢而产生较大的损耗。为抑制谐振,就要降低谐振品质因数Q=XL/R,需适当加大G极的串联电阻,并设法减小寄生电感;加大电阻和减小电感,也能使RLC串联电路进入临界阻尼或过阻尼状态而不发生关断时的振荡。

审核编辑:汤梓红

-

电力场效应管的主要类型和工作原理2024-09-13 2902

-

电力场效应管的结构和工作原理2023-05-01 2887

-

场效应管在电路中如何控制电流大小_场效应管测量方法图解2018-04-03 47964

-

电力场效应管驱动电路2013-03-29 2600

-

VMOS场效应管,VMOS场效应管是什么意思2010-03-04 1908

-

场效应管放大电路2009-11-09 3183

-

电力场效应管2007-10-07 2439

全部0条评论

快来发表一下你的评论吧 !