基本逻辑电路、时序电路、组合电路设计

描述

HDLBits: 在线学习 SystemVerilog(十)-Problem 43-59

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

缩略词索引:

SV:SystemVerilog

从今天开始新的一章-Circuits,包括基本逻辑电路、时序电路、组合电路等。

今天更新整个Basic Gates一小节题目(Problem 43-59)。

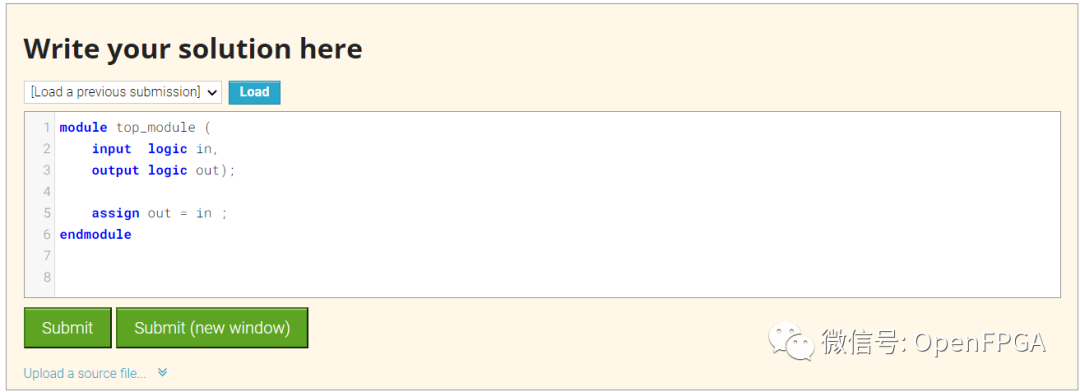

Problem 43-m2014_q4h

题目说明

实现如下电路:

图片来源:HDLBits

模块端口声明

module top_module ( input in, output out);

题目解析

这个题目没什么难度,看下面参考代码即可:

module top_module ( input logic in, output logic out); assign out = in ; endmodule

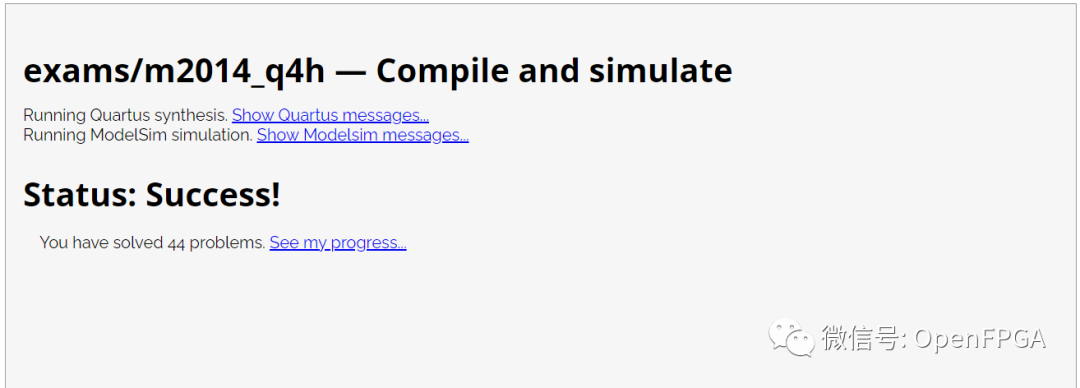

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

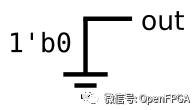

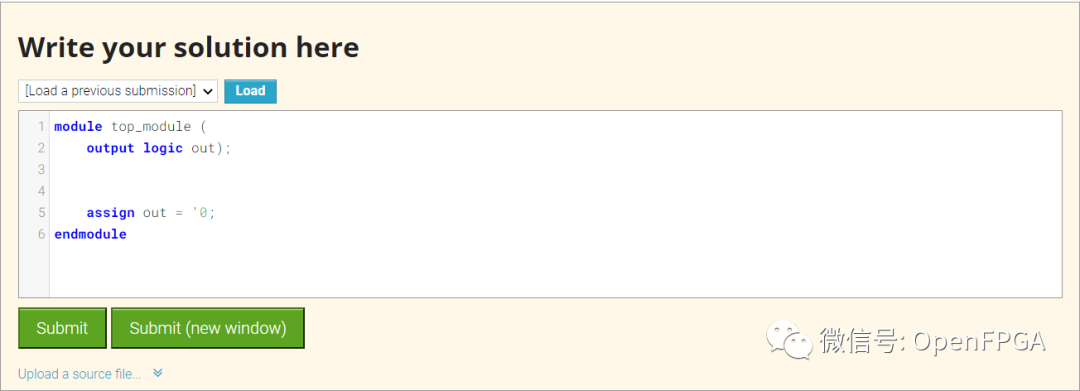

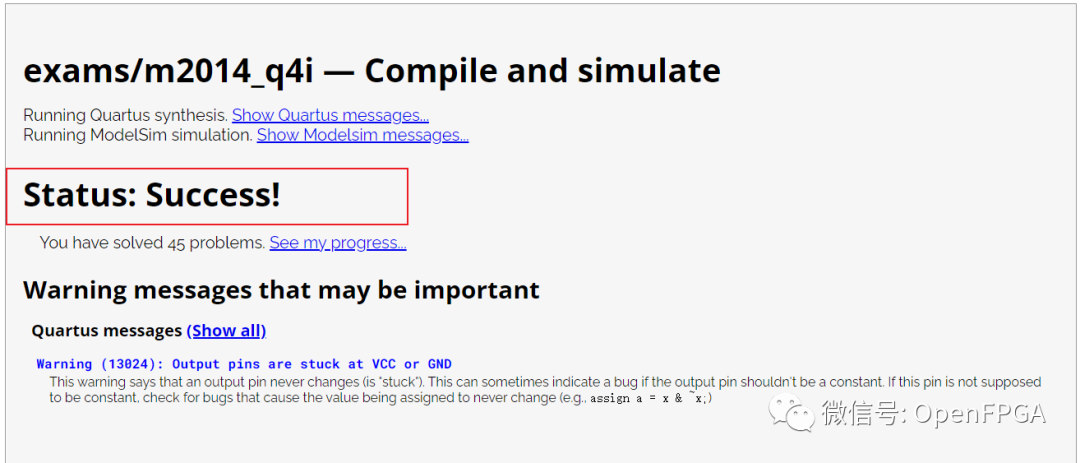

Problem 44-m2014 q4i

题目说明

实现下面电路:

图片来源:HDLBits

模块端口声明

module top_module ( output out);

题目解析

这道题难度不大核心代码只有一行。

简单解答

module top_module ( input logic [7:0] in, output logic parity ); assign parity = ^in ; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的无波形。

这一题就结束了。

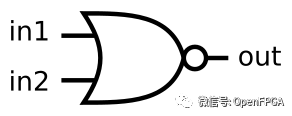

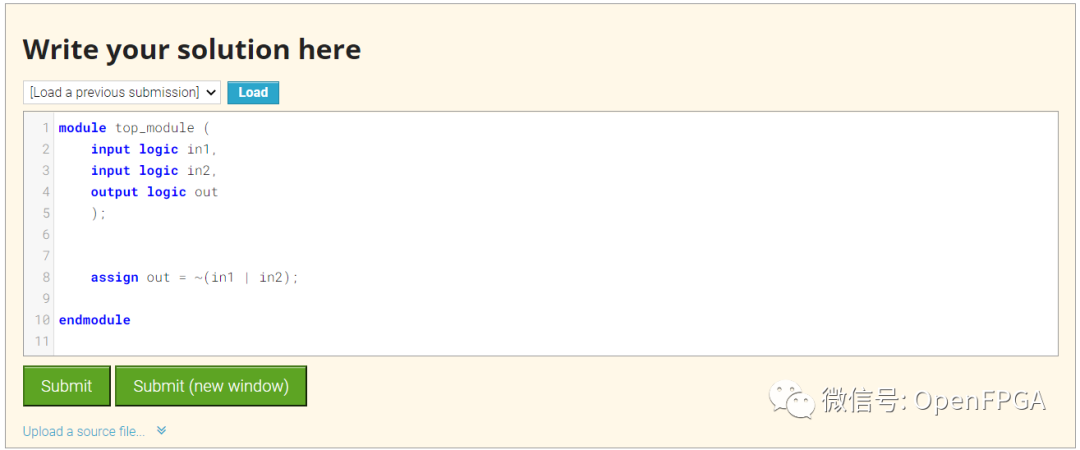

Problem 45-m2014_q4e

题目说明

实现以下电路:

图片来源:HDLBits

模块端口声明

module top_module ( input in1, input in2, output out);

题目解析

还是看懂电路即可。

module top_module ( input logic in1, input logic in2, output logic out ); assign out = ~(in1 | in2); endmodule

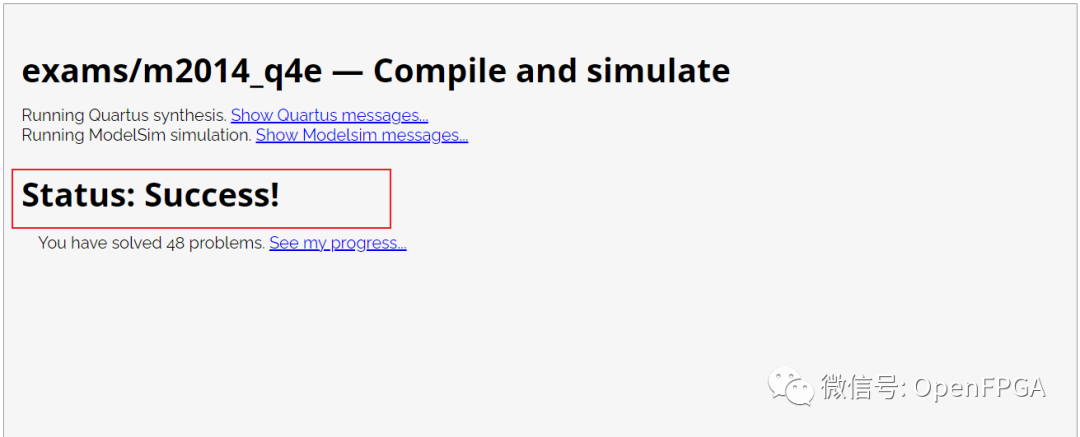

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

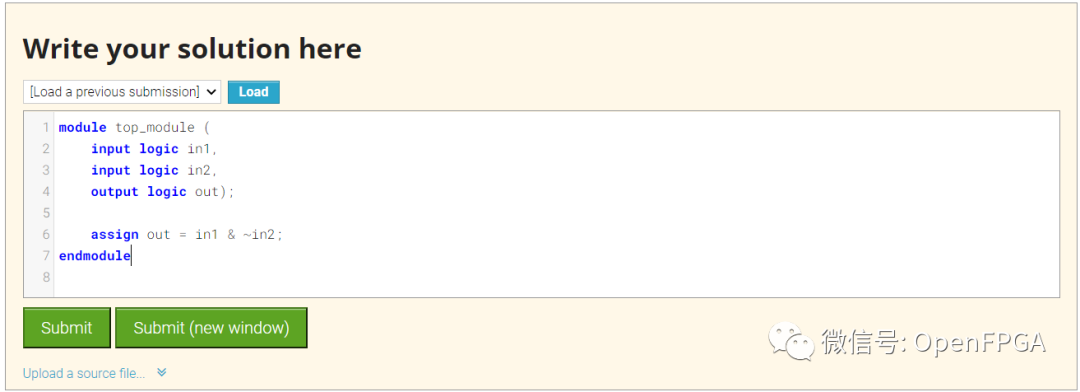

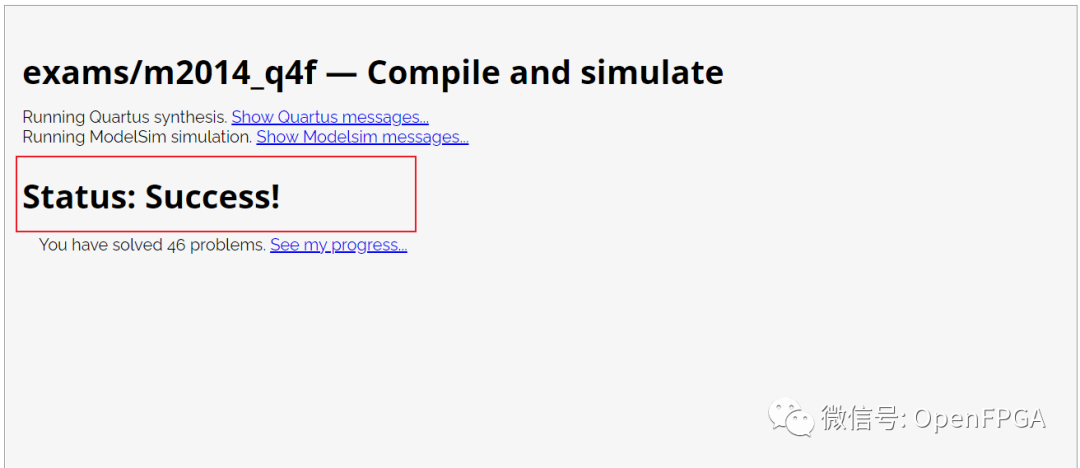

Problem 46-m2014_q4f

题目说明

实现以下电路

图片来源:HDLBits

模块端口声明

module top_module ( input in1, input in2, output out);

题目解析

注意输入端口前的非门。

module top_module ( input logic in1, input logic in2, output logic out); assign out = in1 & ~in2; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

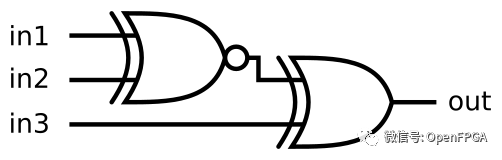

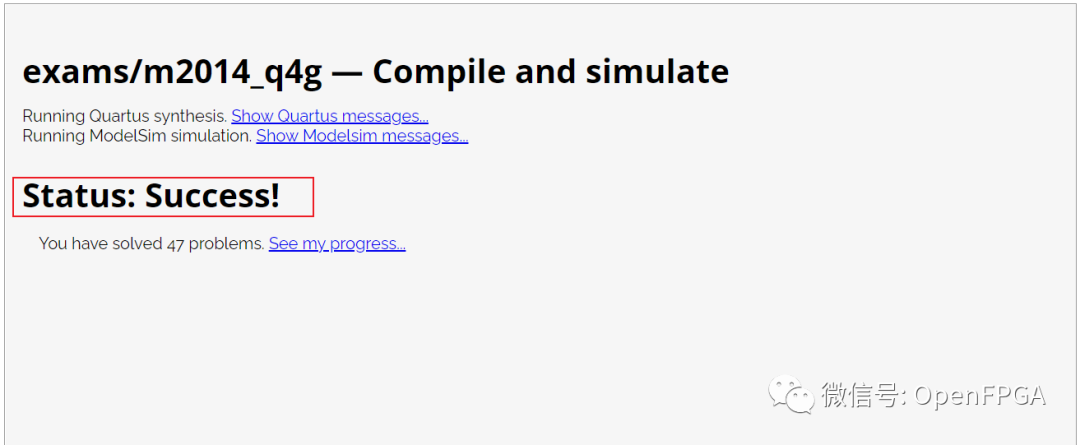

Problem 47-m2014_q4g

题目说明

实现以下电路:

图片来源:HDLBits

图片来源:HDLBits

模块端口声明

module top_module ( input in1, input in2, input in3, output out);

题目解析

还是看懂电路即可。

module top_module ( input logic in1, input logic in2, input logic in3, output logic out); assign out = (in1 ~^ in2) ^ in3; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

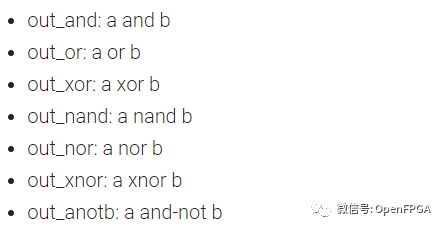

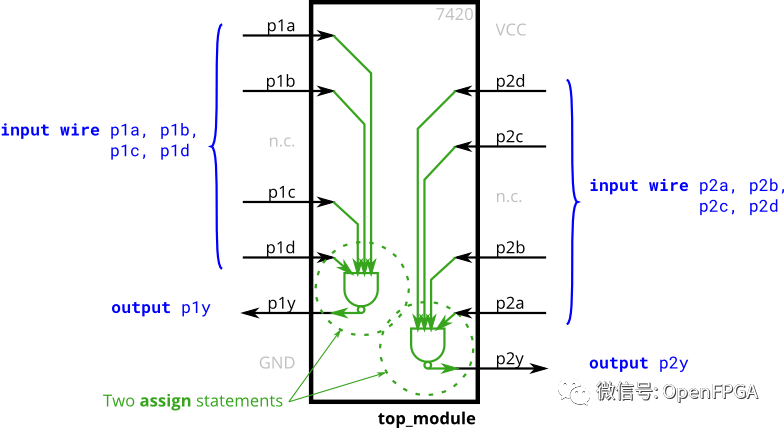

Problem 48-Gates

题目说明

本题希望我们用两输入的组合电路来实现如下功能,该电路共用于7个输出,具体情况如下:

模块端口声明

module top_module( input a, b, output out_and, output out_or, output out_xor, output out_nand, output out_nor, output out_xnor, output out_anotb );

题目解析

多种组合逻辑的实现。

module top_module( input logic a, b, output logic out_and, output logic out_or, output logic out_xor, output logic out_nand, output logic out_nor, output logic out_xnor, output logic out_anotb ); assign out_and = a & b; assign out_or = a | b; assign out_xor = a ^ b; assign out_nand = ~(a & b); assign out_nor = ~(a | b); assign out_xnor = a ~^ b; assign out_anotb = a & ~b; endmodule

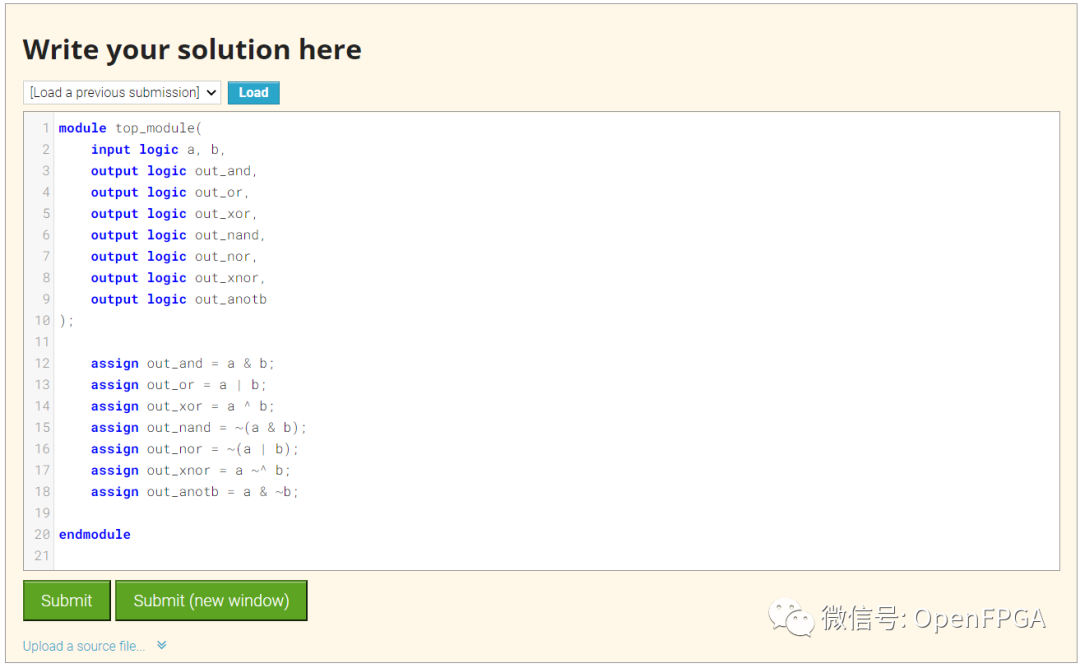

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

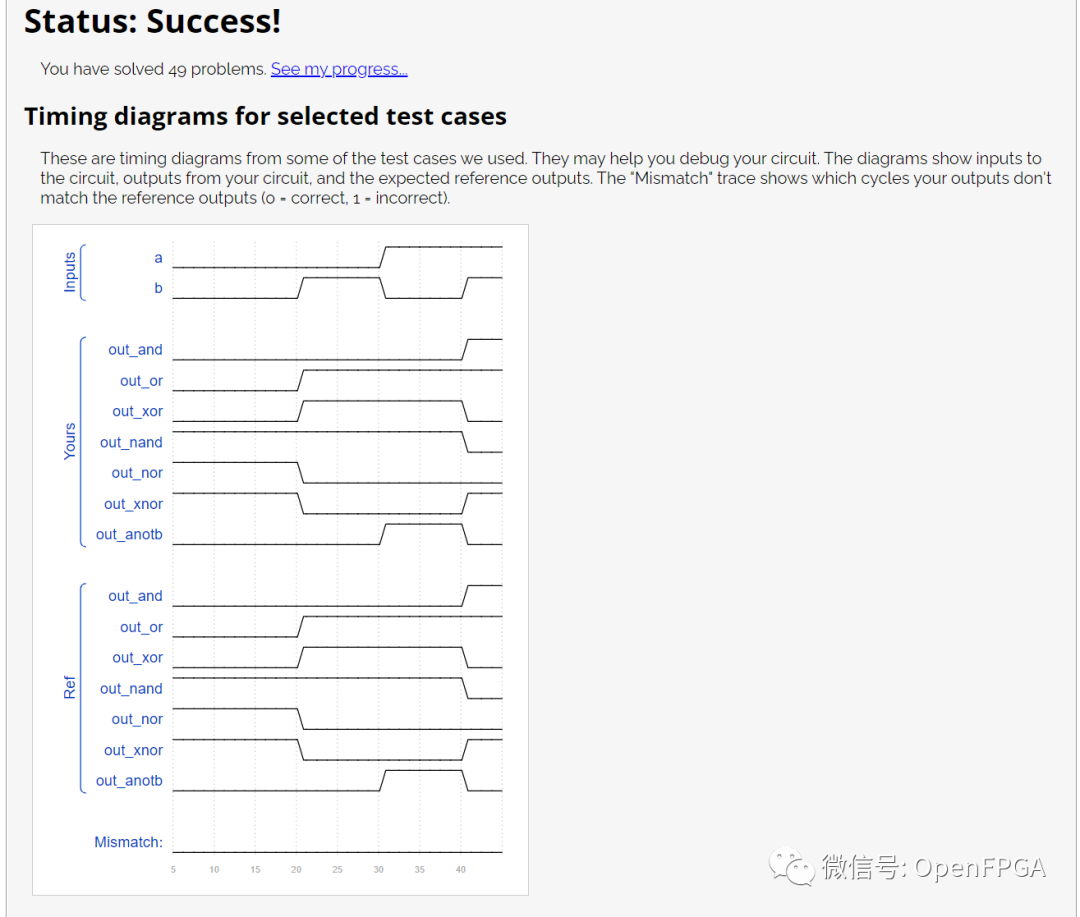

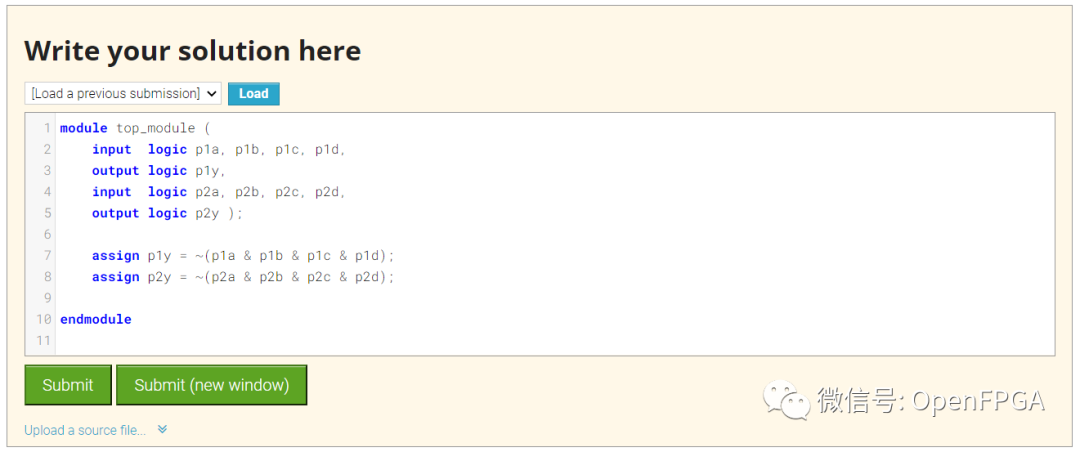

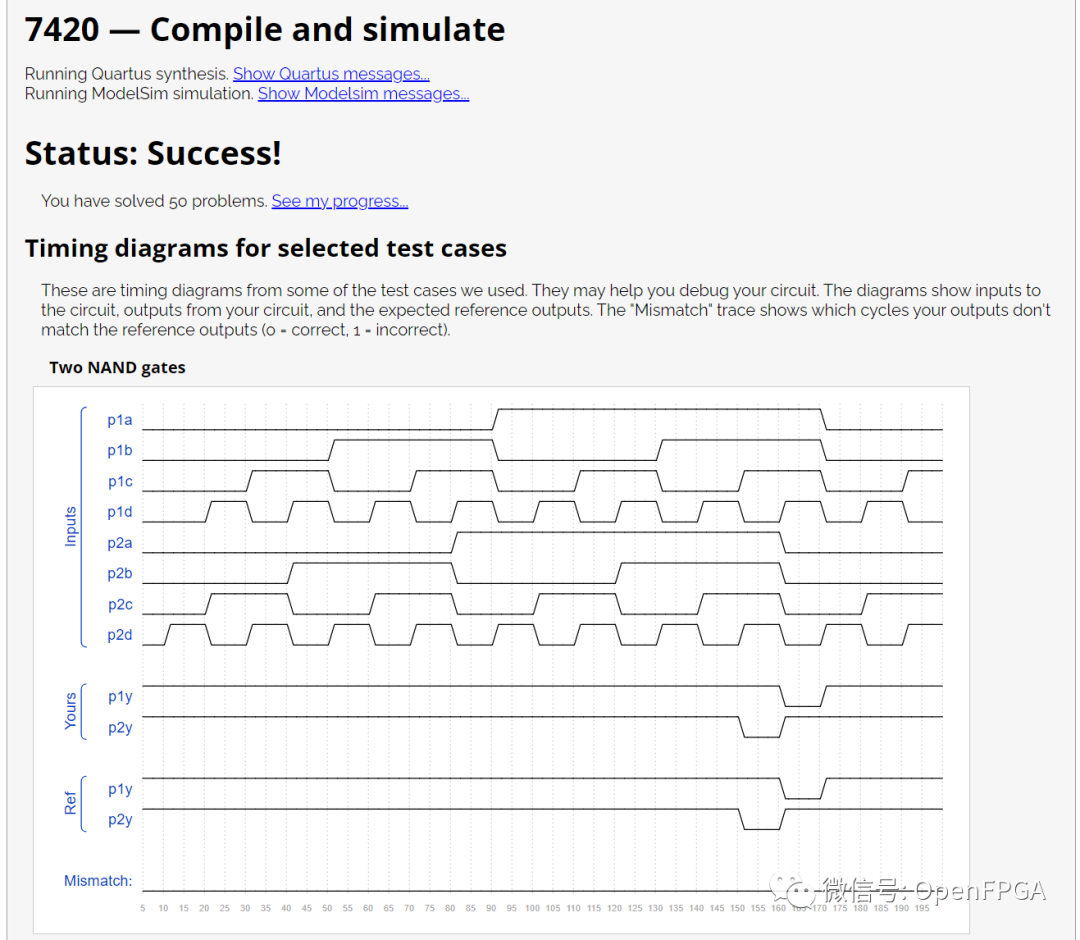

Problem 49-7420

题目说明

7420 chip是拥有两组4输入的与非门芯片,本练习需要构造一个与7420 chip功能一样的电路,拥有8个输入与2个输出。

图片来源:HDLBits

图片来源:HDLBits

模块端口声明

module top_module ( input p1a, p1b, p1c, p1d, output p1y, input p2a, p2b, p2c, p2d, output p2y );

题目解析

这个题目无需理解7420是干什么的,只需要按照图中电路图实现逻辑即可。

module top_module ( input logic p1a, p1b, p1c, p1d, output logic p1y, input logic p2a, p2b, p2c, p2d, output logic p2y ); assign p1y = ~(p1a & p1b & p1c & p1d); assign p2y = ~(p2a & p2b & p2c & p2d); endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

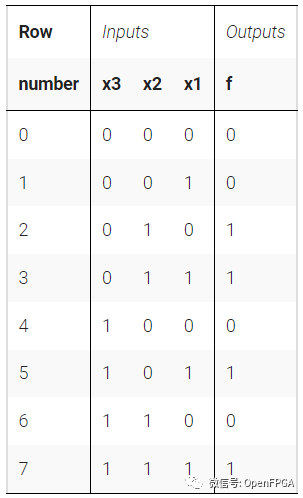

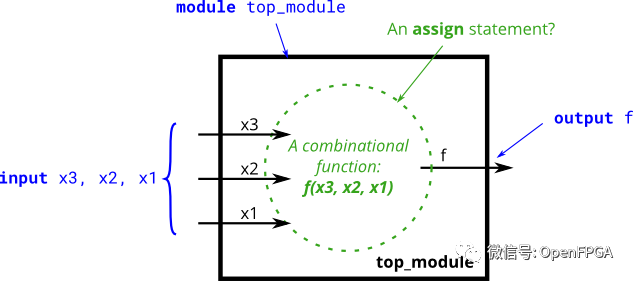

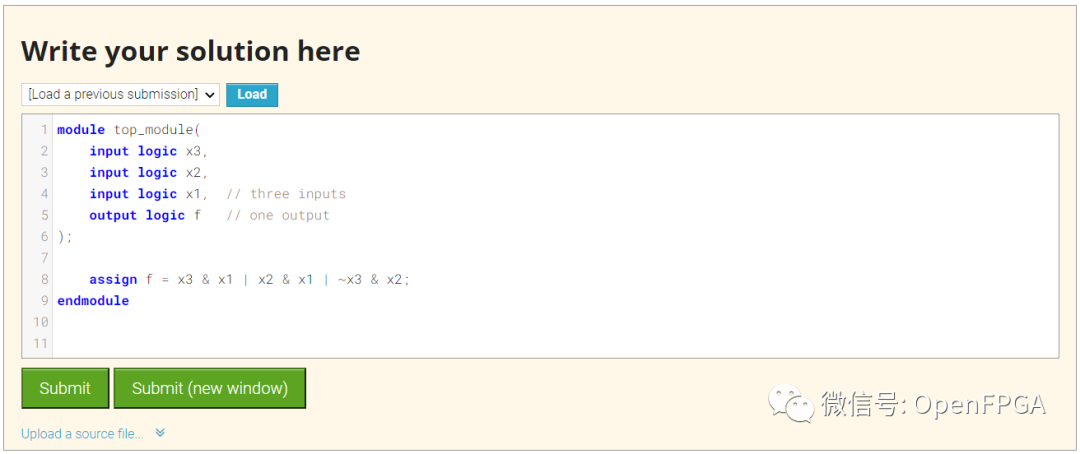

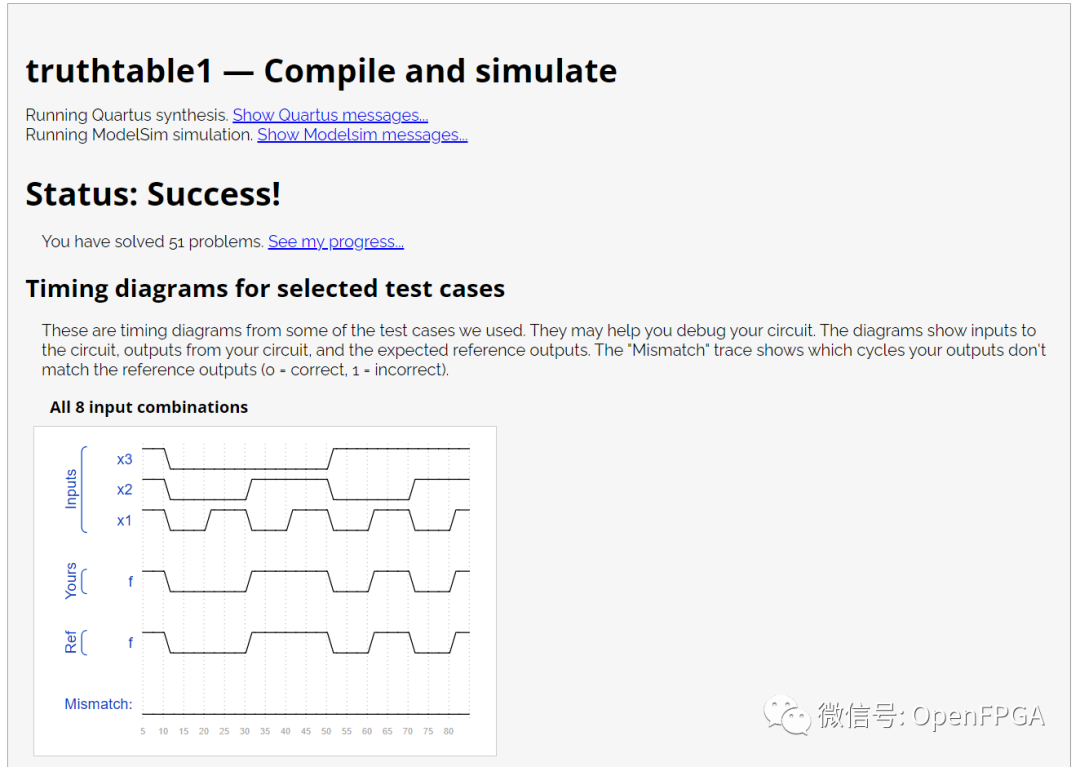

Problem 50-Truthtable1

开始练习真值表了,网站上有些实例讲解,我就不翻译了,学过数电的应该难度都不大。

题目说明

创建一个实现下述真值表的组合电路:

真值表如下:

图片来源:HDLBits

图片来源:HDLBits

最终实现的硬件框图如下:

图片来源:HDLBits

图片来源:HDLBits

TIPS:约一行代码解决问题

模块端口声明

module top_module( input x3, input x2, input x1, // three inputs output f // one output );

题目解析

这个题目重点是真值表化简,将上面的真值表化简成最小项表达式即可。具体可以看下数电书很容易得到结果。

module top_module( input logic x3, input logic x2, input logic x1, // three inputs output logic f // one output ); assign f = x3 & x1 | x2 & x1 | ~x3 & x2; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

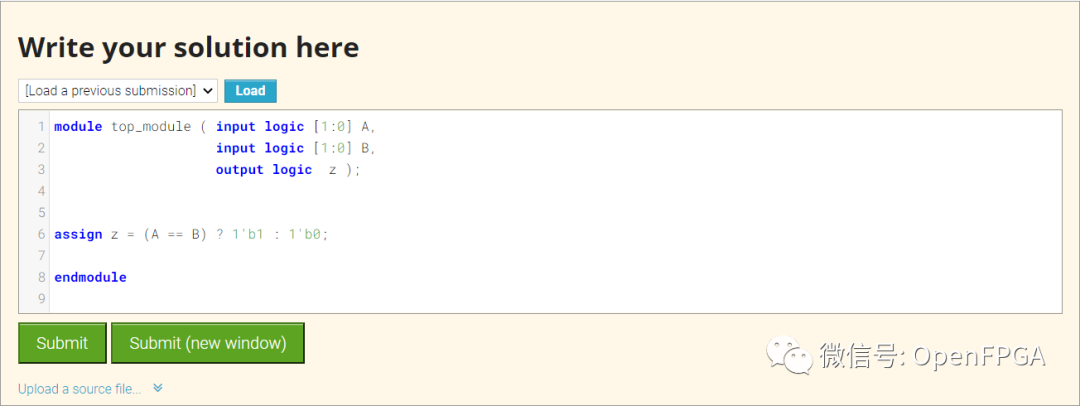

Problem 51-Mt2015_eq2

题目说明

创建一个具有两个 2 位输入A[1:0]和B[1:0]的电路,并产生一个输出z。如果A = B ,则z的值应为 1 ,否则z应为 0。

模块端口声明

module top_module ( input [1:0] A, input [1:0] B, output z );

题目解析

这个题目重点是灵活使用三元运算符,因为这个语法比较简单,所以大家注意一下使用方式即可~

module top_module ( input logic [1:0] A, input logic [1:0] B, output logic z ); assign z = (A == B) ? 1'b1 : 1'b0; endmodule

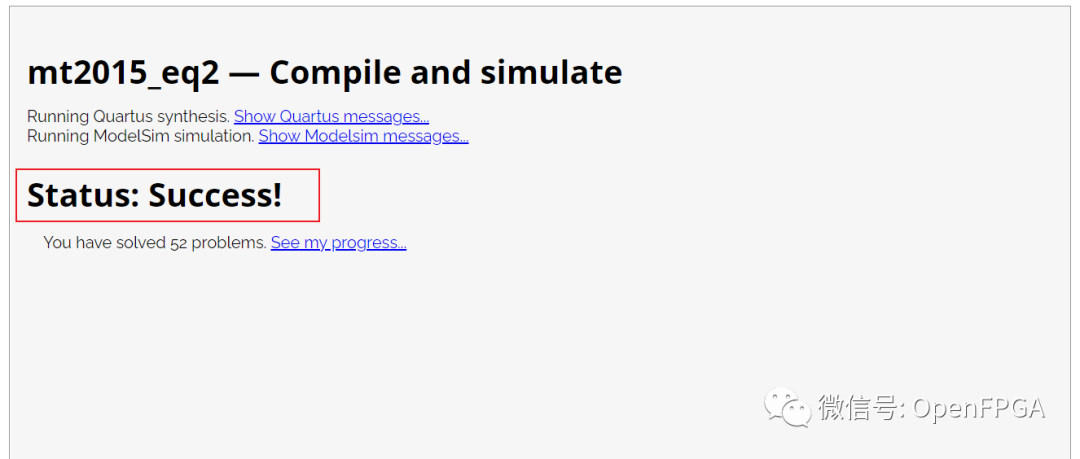

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

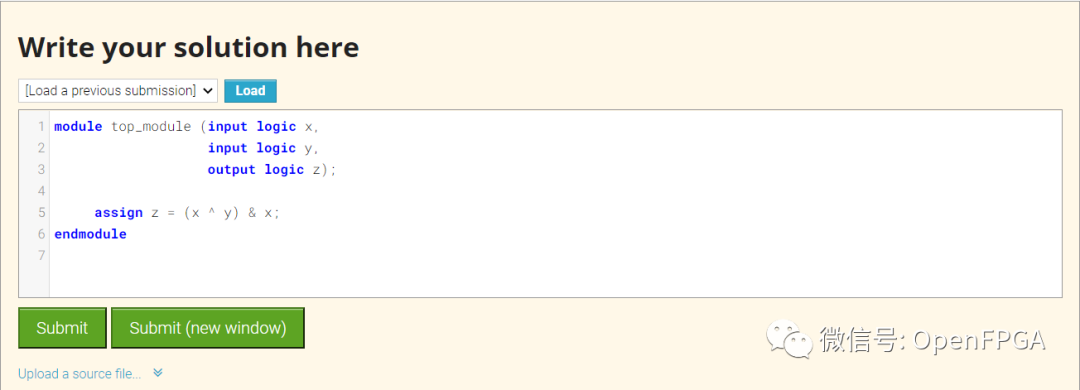

Problem 52-Mt2015_q4a

题目说明

实现模块 A ,该模块实现函数z = (x^y) & x。

模块端口声明

module top_module (input x, input y, output z);

题目解析

module top_module (input logic x, input logic y, output logic z); assign z = (x ^ y) & x; endmodule

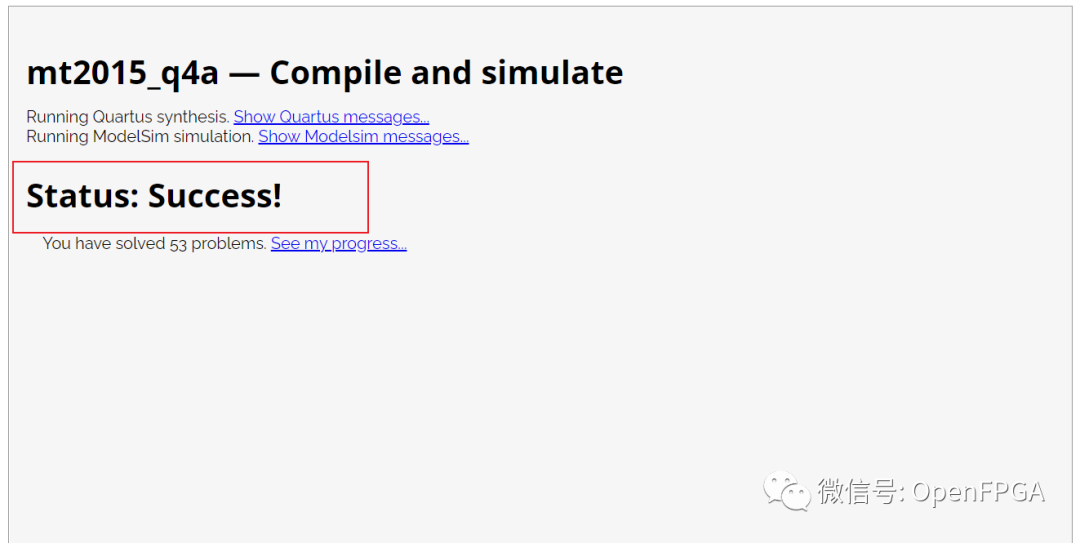

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

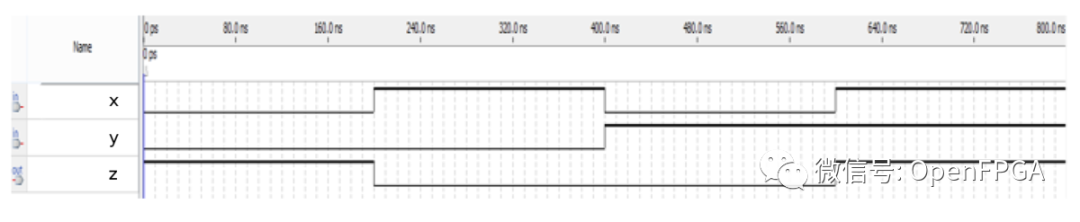

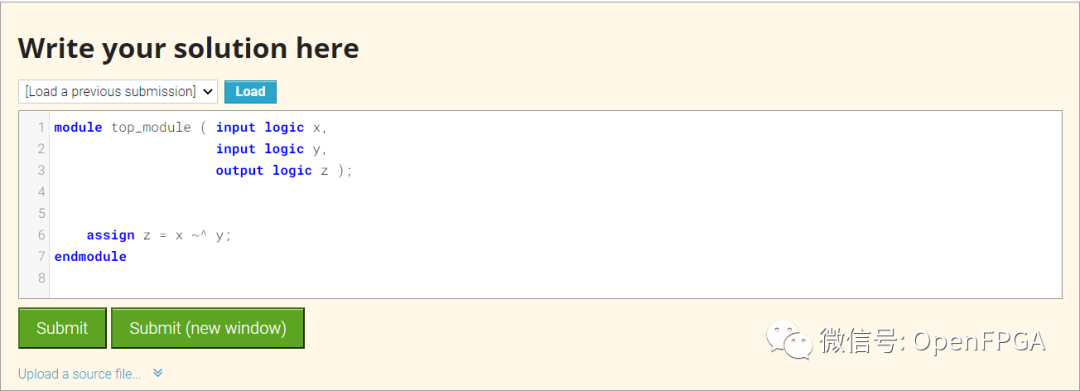

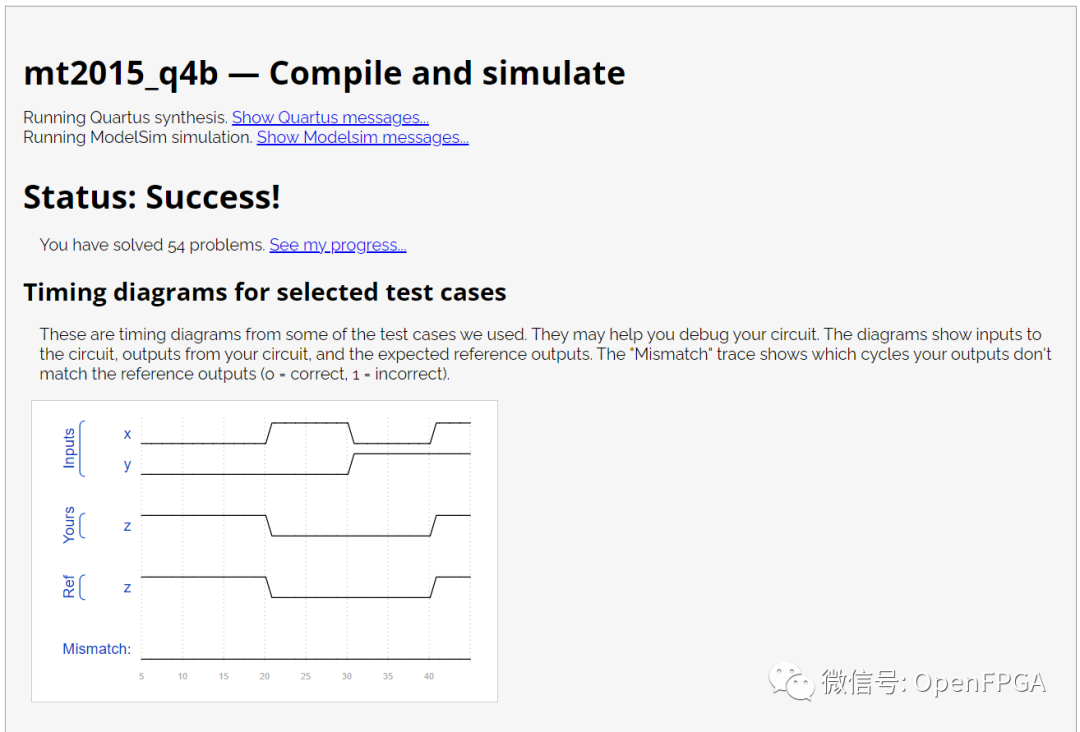

Problem 53-Mt2015_q4b

题目说明

电路B可以用下面的仿真波形来描述:

图片来源:HDLBits

图片来源:HDLBits

模块端口声明

module top_module ( input x, input y, output z );

题目解析

这个题目可以使用采点的方式,选择几个特殊点,制作成真值表,然后化简即可。

或者从波形上看特点:根据观察所得输出 z 为 x 与 y 的同或输出,即相同为1, 不同为0;故实现代码如下:

module top_module ( input logic x, input logic y, output logic z ); assign z = x ~^ y; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

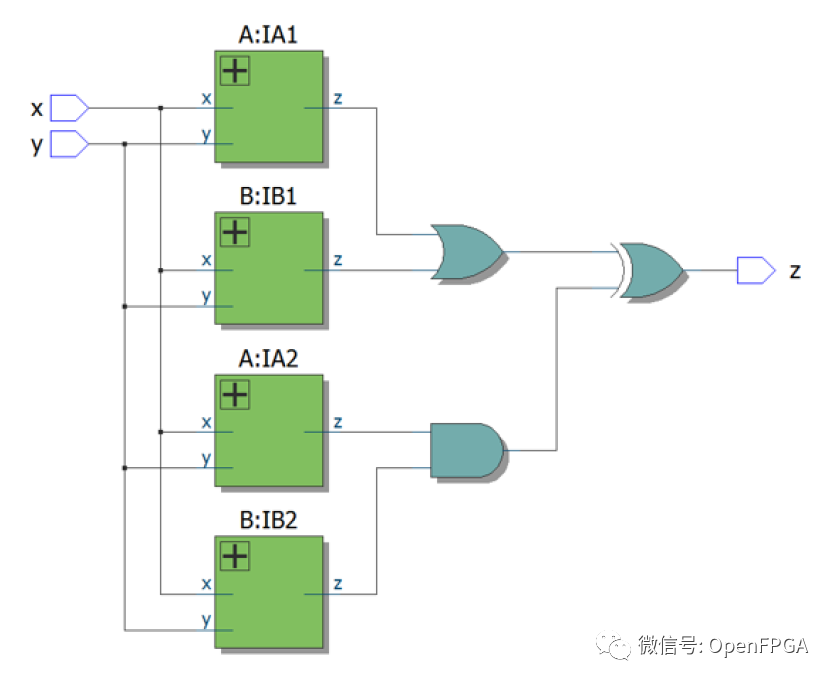

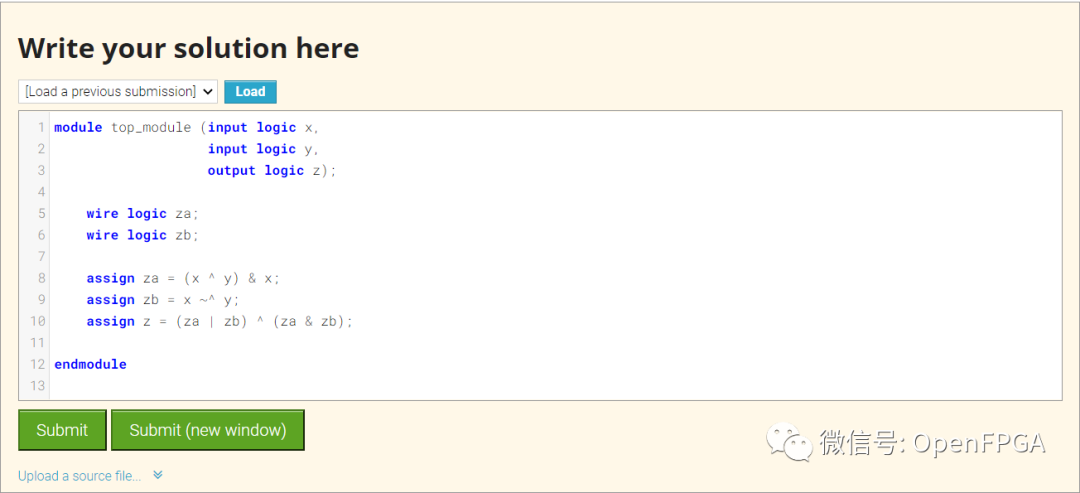

Problem 54-Mt2015_q4

题目说明

根据子模块Problem 52 与 53 来实现如下电路:

图片来源:HDLBits

图片来源:HDLBits

模块端口声明

module top_module (input x, input y, output z);

题目解析

这个题目重点知道题目中A、B代表什么,其实这两个就是上面两道题目实现的子模块,然后在将这两个模块的输出进行逻辑操作即可。

module top_module (input logic x, input logic y, output logic z); wire logic za; wire logic zb; assign za = (x ^ y) & x; assign zb = x ~^ y; assign z = (za | zb) ^ (za & zb); endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

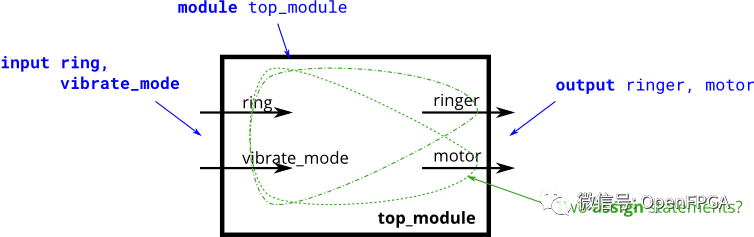

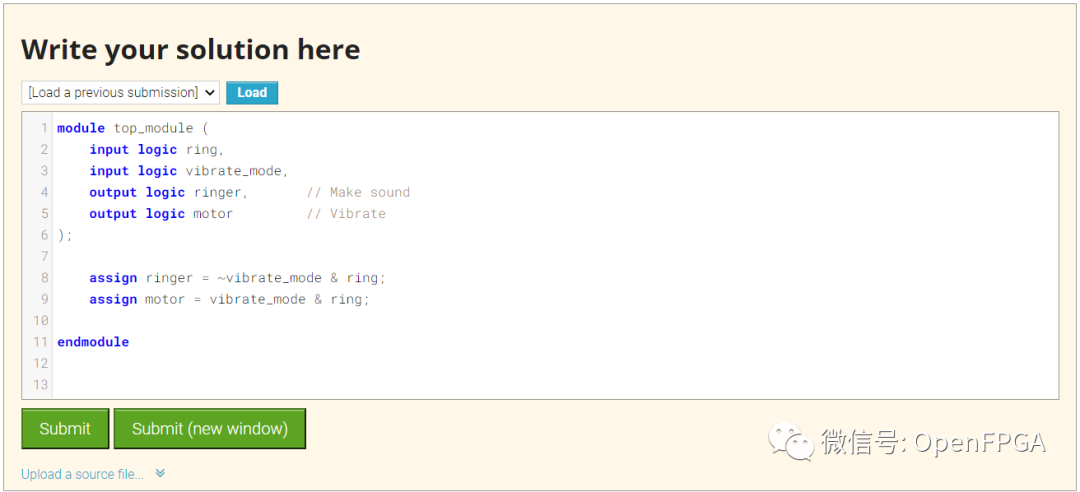

Problem 55-Ringer

题目说明

假设您正在设计一个手机的振铃器和振动电机控制电路。每当电话需要从来电中振铃 (input ring) 时,您的电路必须打开振铃器 (output motor = 1 ) 或电机 (output ringer = 1),但不能同时打开这两个。如果手机处于振动模式 (input vibrate = 1),请打开电机( output motor = 1 )。否则,打开铃声。

我们尝试仅适用assign语句来实现该组合电路。

设计提示:在设计电路时,人们经常不得不“倒退”地考虑问题,从输出开始,然后再向输入倒退,这是属于软件编程思想。硬件电路的编程与软件的编程是存在差异的,一般进行软件编程时,我们是先关注输入( if (input are _)),再关注输出( then (output are ))。而在硬件编程时,我们需要转变思维方式,在确保输出是正确的情况下,再思考输入。( The (output should be _) when (inputs are __))。

上面的问题描述是用适合软件编程的命令式写成的(if ring then do this),所以你必须把它转换成更适合硬件实现的声明式(assign ringer = ___)。能够在两种风格之间进行思考和转换是硬件设计所需的最重要技能之一。

图片来源:HDLBits

图片来源:HDLBits

模块端口声明

module top_module ( input ring, input vibrate_mode, output ringer, // Make sound output motor // Vibrate );

题目解析

题目难度不大,重点是根据输出的两个信号,裁决输入逻辑。

module top_module ( input logic ring, input logic vibrate_mode, output logic ringer, // Make sound output logic motor // Vibrate ); assign ringer = ~vibrate_mode & ring; assign motor = vibrate_mode & ring; endmodule

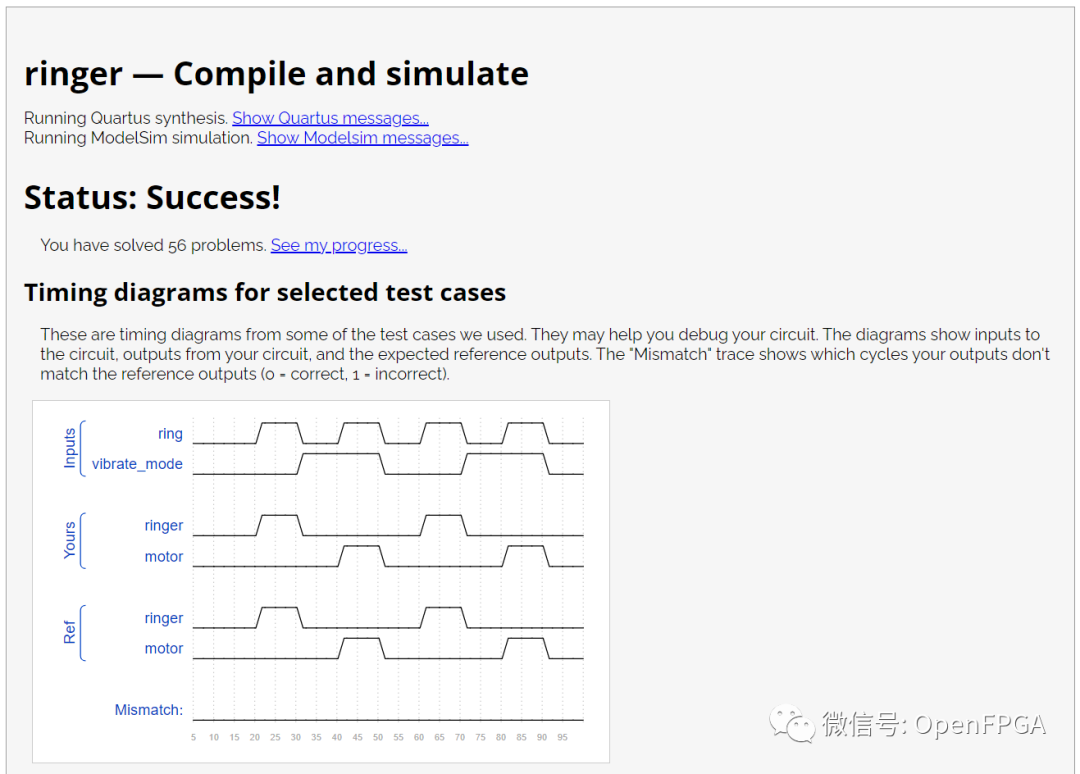

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

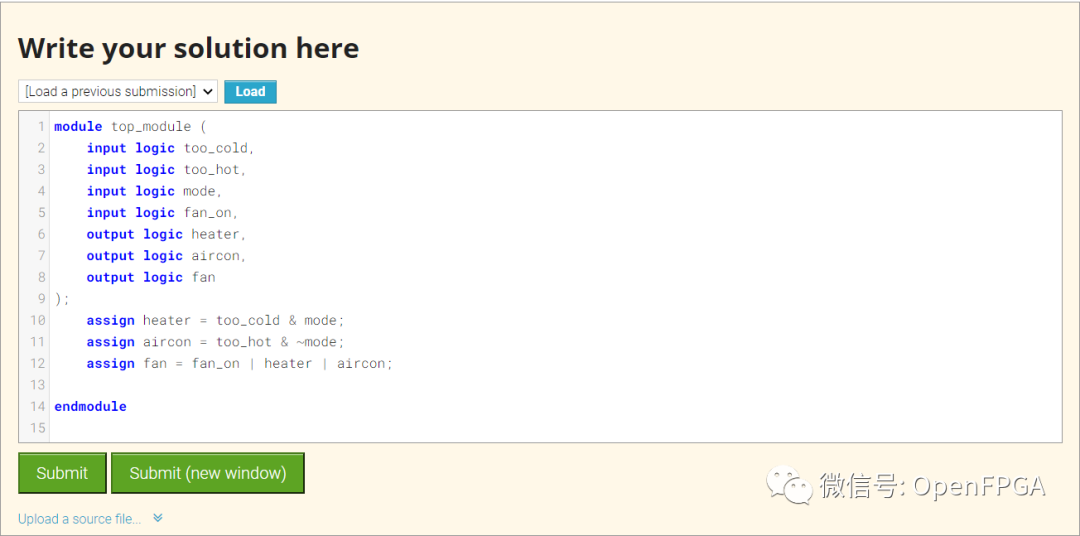

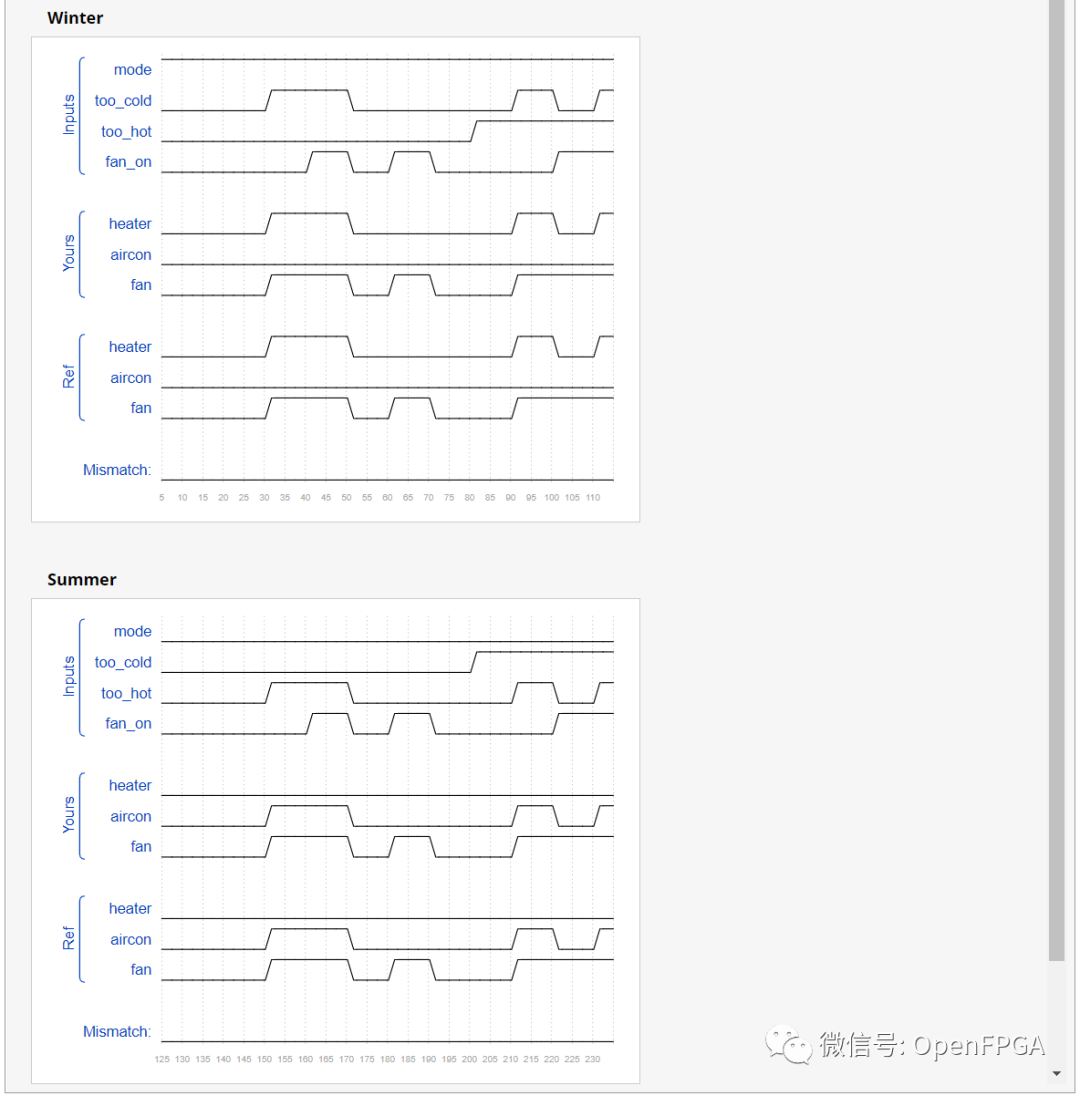

Problem 56-Thermostat

题目说明

一个冷/热恒温控制器可以同时在冬季和夏季对温度进行调节。实现一个可以根据需要打开和关闭加热器、空调和鼓风机的电路。

恒温器可以处于以下两种模式之一:加热 ( mode = 1) 和冷却 ( mode = 0)。在制热模式下,当天气太冷时打开加热器(too_cold = 1),但不要使用空调。在制冷模式下,空调过热时打开空调(too_hot = 1),但不要打开加热器。当加热器或空调打开时,还要打开风扇以循环空气。此外,即使加热器和空调关闭,用户也可以请求将风扇打开(fan_on = 1)。

尝试仅使用assign语句,看看是否可以将问题描述转换为逻辑电路。

模块端口声明

module top_module ( input too_cold, input too_hot, input mode, input fan_on, output heater, output aircon, output fan );

题目解析

这个题目解决方式参考上一题。

module top_module ( input logic too_cold, input logic too_hot, input logic mode, input logic fan_on, output logic heater, output logic aircon, output logic fan ); assign heater = too_cold & mode; assign aircon = too_hot & ~mode; assign fan = fan_on | heater | aircon; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

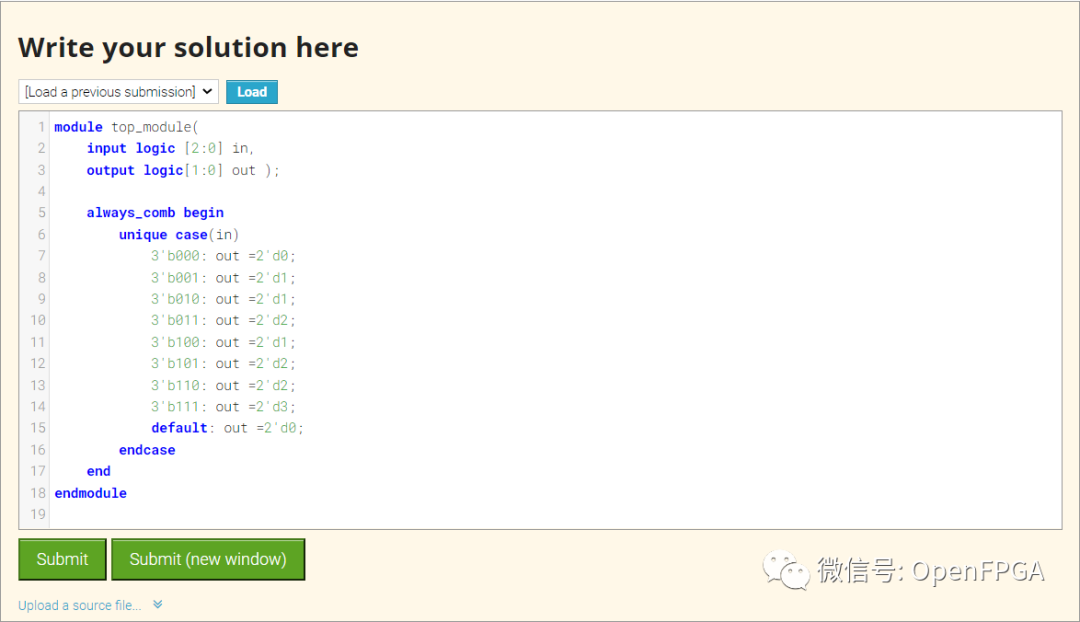

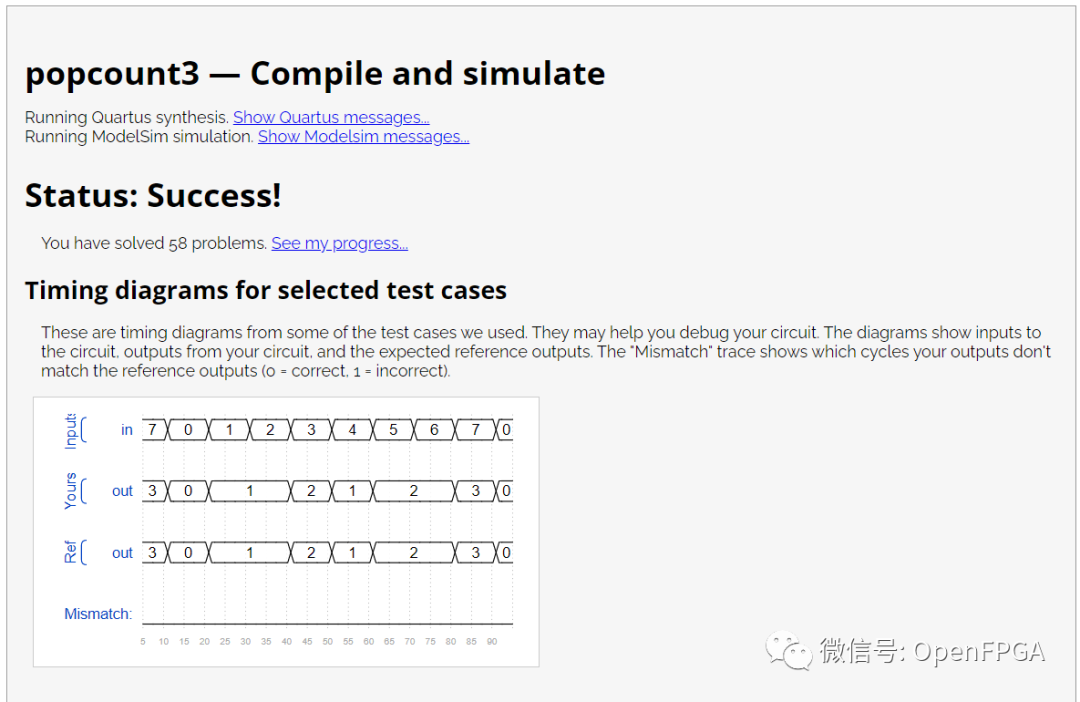

Problem 57-Conditional

题目说明

又是一道计“1”电路。

模块端口声明

module top_module( input [2:0] in, output [1:0] out );

题目解析

有很多种方式,我们使用组合电路实现,也可以使用for循环。

module top_module( input logic [2:0] in, output logic[1:0] out ); always_comb begin unique case(in) 3'b000: out =2'd0; 3'b001: out =2'd1; 3'b010: out =2'd1; 3'b011: out =2'd2; 3'b100: out =2'd1; 3'b101: out =2'd2; 3'b110: out =2'd2; 3'b111: out =2'd3; default: out =2'd0; endcase end endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

PS:FOR循环

module top_module( input [2:0] in, output [1:0] out ); always @(*) begin out = 2'b00; for(integer i = 0; i<3; i++) begin if(in[i] == 1'b1) out = out + 1'b1; end end endmodule

这一题就结束了。

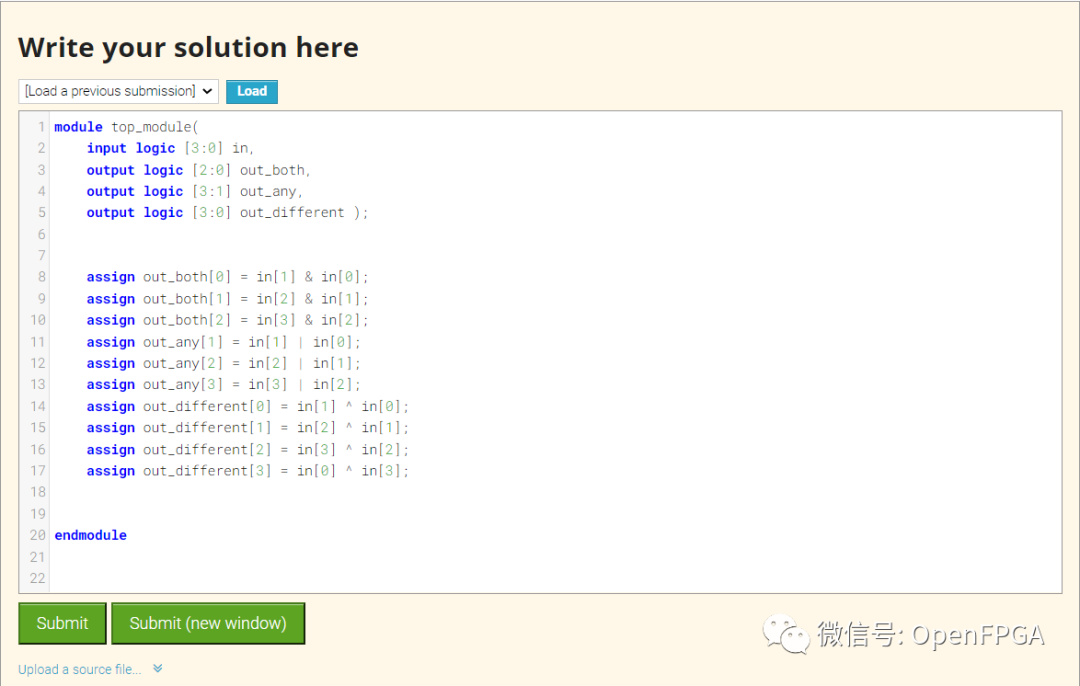

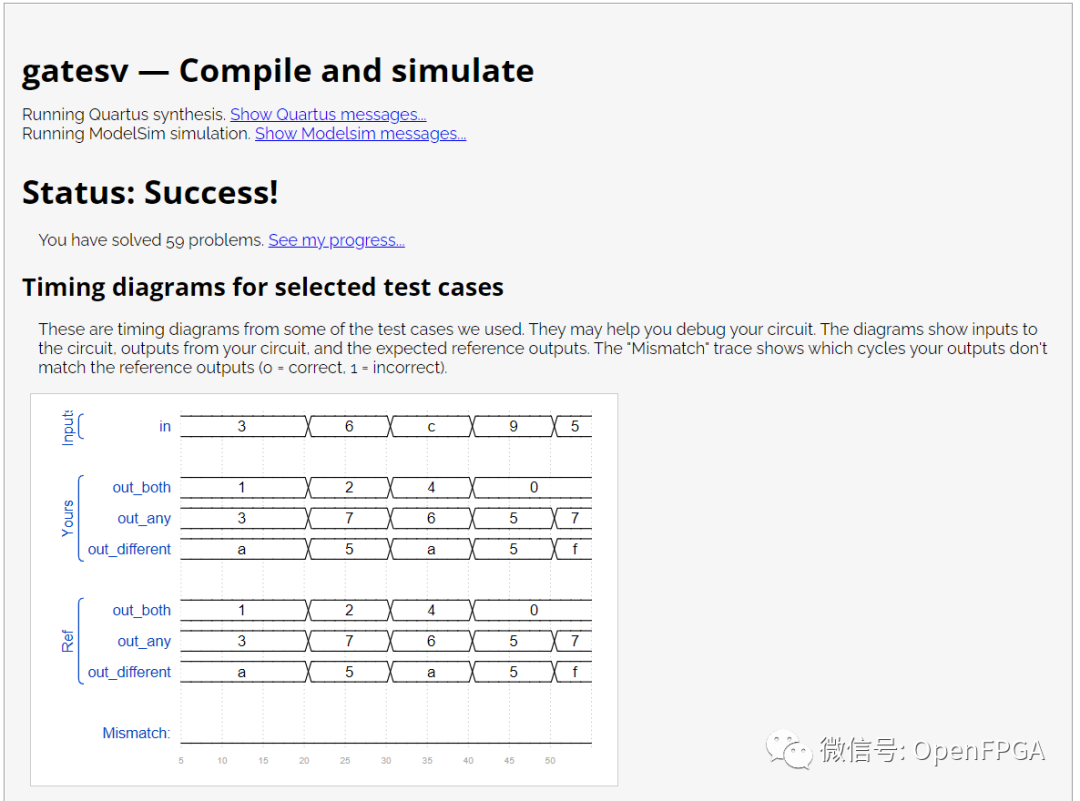

Problem 58-Gatesv

题目说明

在给定一个四位输入向量[3:0]。我们想知道每个位与其相邻的位之间的一些关系:

out_both:此输出向量的每个位指示相应的输入位及其左侧的“邻居”(较高的索引)是否都是“1” 。例如,out_both[2]表明in[2]和in[3]是否都为 1。由于in[3]左边没有“邻居”,所以我们不需要知道out_both[3] .

out_any:此输出向量的每个位指示相应的输入位及其右侧的“邻居”是否为“1”。例如,out_any[2]指示in[2]或in[1]是否为 1。由于in[0]右侧没有邻居,因此我们不需要知道out_any[0] .

out_different:此输出向量的每个位指示相应的输入位是否与其左侧的“邻居”不同。例如,out_diff[2]指示in[2]是否与in[3]不同。对于这部分,将向量视为环绕,因此in[3]左侧的邻居是in[0]。

模块端口声明

module top_module( input [3:0] in, output [2:0] out_both, output [3:1] out_any, output [3:0] out_different );

题目解析

这个题目重点理解这个相同或者不同之间的逻辑关系(就是与或非这三种关系,仔细思考,就没什么问题了)。

module top_module( input logic [3:0] in, output logic [2:0] out_both, output logic [3:1] out_any, output logic [3:0] out_different ); assign out_both[0] = in[1] & in[0]; assign out_both[1] = in[2] & in[1]; assign out_both[2] = in[3] & in[2]; assign out_any[1] = in[1] | in[0]; assign out_any[2] = in[2] | in[1]; assign out_any[3] = in[3] | in[2]; assign out_different[0] = in[1] ^ in[0]; assign out_different[1] = in[2] ^ in[1]; assign out_different[2] = in[3] ^ in[2]; assign out_different[3] = in[0] ^ in[3]; endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

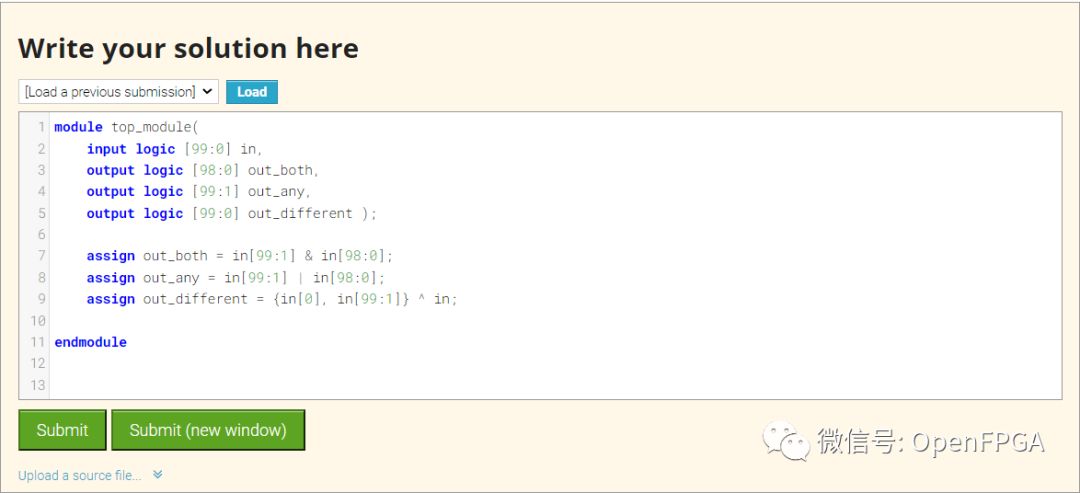

Problem 59-Gatesv100

题目说明

这一条道题和上一题完全相同,只不过输入向量变成了[99:0],其他说明没变。

模块端口声明

module top_module( input [99:0] in, output [98:0] out_both, output [99:1] out_any, output [99:0] out_different );

题目解析

这个题目的解决方式,就不能使用上面那种罗列所有可能情况的解决方式了(太多了),所以我们需要观察上面那一题的规律来解决问题,这一题最简单的方式不会超过三行语句,但是难度还是不大。

module top_module(

input logic [99:0] in,

output logic [98:0] out_both,

output logic [99:1] out_any,

output logic [99:0] out_different );

assign out_both = in[99:1] & in[98:0];

assign out_any = in[99:1] | in[98:0];

assign out_different = {in[0], in[99:1]} ^ in;

endmodule

点击Submit,等待一会就能看到下图结果:

注意图中无波形。

这一题就结束了。

总结

今天的几道题就结束了,整体是从需求设计组合逻辑电路,再从波形图设计,还有两道从实际使用角度设计,对于组合电路的设计理解非常有帮助。

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

代码链接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

审核编辑:汤梓红

-

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么2024-03-26 7067

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14372

-

时序逻辑电路设计之同步计数器2023-05-22 5640

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9225

-

什么是时序逻辑电路2019-02-26 33192

-

组合逻辑电路的特点详解2018-01-30 40323

-

CMOS逻辑电路高级技术与时序电路2010-08-13 579

-

时序逻辑电路2010-08-10 951

-

组合逻辑电路设计基础2010-05-06 831

-

组合逻辑电路课件2009-07-15 722

-

时序逻辑电路设计2009-03-18 1050

-

组合逻辑电路设计实验2008-09-12 2549

全部0条评论

快来发表一下你的评论吧 !