FPGA流水灯的设计流程

可编程逻辑

描述

4.4 流水灯的设计输入

4.4.1 建立FPGA工程

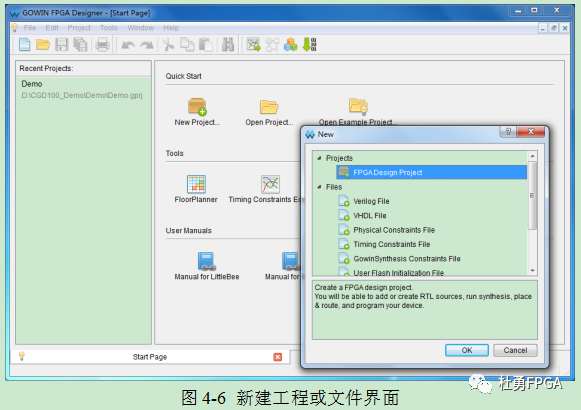

完成项目需求分析、电路图分析以及方案设计后,接下来可以进行FPGA设计了。如果用户的计算机已安装云源软件GOWIN FPGA Designer,双击桌面上的程序图标,即可打开GOWIN FPGA Designer。在工作界面中依次单击菜单“File→New”,可打开新建工程(Projects)或文件(Files)类型选择对话框,如图4-6所示。

图4-6 新建工程或文件界面

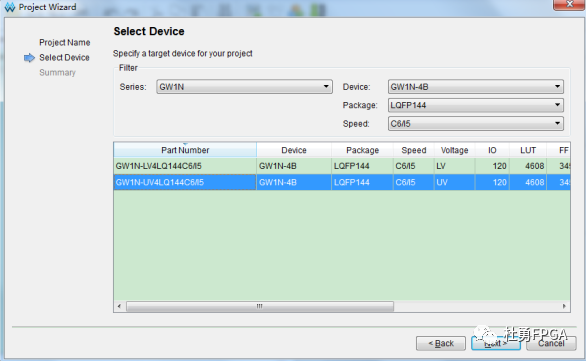

选中“Projects→FPGA Design Project”条目,或直接单击主界面中的“Quick Start→New Project”图标,即可打开新建工程对话框,在对话框中设置工程的名称(waterlight)和存放路径,单击“Next”打开器件选择(Select Device)对话框,如图4-7所示。

图4-7 FPGA 器件选择界面

根据CGD100开发板上的FPGA器件型号,在器件系列(Series)列表框中选择GW1N,器件(Device)列表中选择GW1N-4B,封装(Package)列表中选择LQFP144,速度等级(Speed)中选择C6/I5,图中的列表框中自动筛选出CGD100开发板对应的FPGA型号GW1N-UV4LQ144C6/I5,选中该器件型号,依次单击“Next→Finish”完成工程的创建,且软件自动返回到主界面。

此时打开工程路径所指向的文件夹,可以发现目录中出现了两个子文件夹“impl”、“src”以及CPRJ类型的工程文件waterlight。其中,impl文件夹存放工程编译后的一些过程文件,src文件夹存放工程中新建的资源文件。可以双击waterlight.gprj直接启动云源软件并打开该FPGA工程。

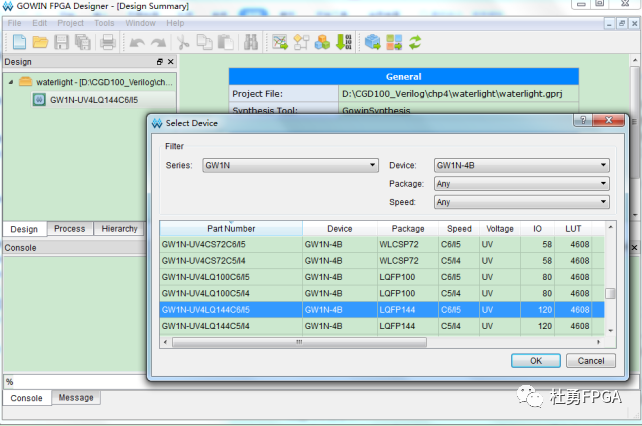

完成工程创建后,如需重新指定FPGA设计的目标器件,可以单击云源软件主界面中的目标器件名称,打开器件设置界面重新指定目标器件,如图4-8所示。

图4-8 创建工程后重新设置目标FPGA器件界面

4.4.2 Verilog HDL程序输入

完成FPGA工程建立后,开始编写Verilog HDL程序代码进行FPGA设计。AMD、Intel公司的FPGA开发环境均提供了原理图方式及HDL代码两种输入方式,云源软件仅提供了HDL代码输入方式。原理图的设计输入方式类似于绘制电路图的设计方式,虽然直观,但十分不便于程序移植和后期代码的维护修改,因此应用很少。本书均采用HDL代码输入的方式进行FPGA程序设计。

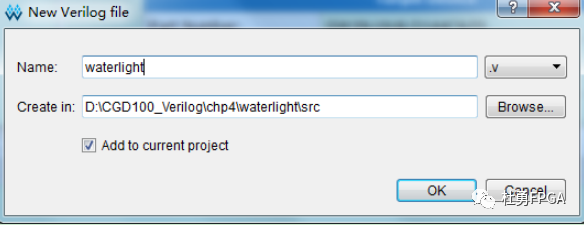

在GWIN FPGA Designer主工作界面中依次单击菜单“File→New”,打开新建资源界面,在资源界面中选中“Files→Verilog File”,单击“OK”,在文件名编辑框(Name)中输入Verilog HDL文件名waterlight,文件存放目录编辑框(Create In)自动设置为当前工程目录下的src文件夹下,如图4-9所示。

图4-9 新建Verilog文件界面

单击“OK”按键,完成Verilog HDL文件的创建,软件主界面的工作区中自动生成名为“waterlight.v”的文件,且该文件处于打开状态,可以在文件中输入设计代码。

在文件中输入下列代码。

//waterlight.v文件

module waterlight(

input clk50m, //系统时钟:50MHz

input rst_n, //复位信号:低电平有效

output reg [7:0] led //8个LED灯

);

reg [29:0] cn=0;

always @(posedge clk50m or negedge rst_n)

if (!rst_n) begin

cn <= 0;

led <= 8'hff;

end

else begin

if (cn>30'd8000_0000) cn <=0;

else cn <= cn + 1;

if (cn<30'd1000_0000) led <=8'b0000_0001;

else if (cn<30'd2000_0000) led <=8'b0000_0010;

else if (cn<30'd3000_0000) led <=8'b0000_0100;

else if (cn<30'd4000_0000) led <=8'b0000_1000;

else if (cn<30'd5000_0000) led <=8'b0001_0000;

else if (cn<30'd6000_0000) led <=8'b0010_0000;

else if (cn<30'd7000_0000) led <=8'b0100_0000;

else led <=8'b1000_0000;

end

endmodule

上述文件代码实现的是一个8位流水灯功能电路,每个灯点亮0.2s的时间,依次循环点亮,实现流水灯效果。本章仅关注FPGA的基本开发流程,关于流水灯的设计思路及Verilog HDL语法细节将在后续章节逐步展开讨论。

完成代码输入后保存文件。流水灯程序共有10个信号接口:时钟信号clk50m、复位信号rst_n,以及8根LED灯信号。要使设计的程序能够在FPGA开发板上正确运行,需要将程序的端口信号与CGD100电路板上的FPGA管脚关联起来。完成信号与管脚关联过程称为物理管脚约束。

新建类型为“Physical Constraints File”,在文件中输入下列代码。

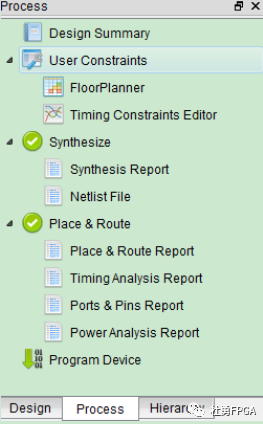

//CGD100.cst文件IO_LOC "clk50m" 7;IO_PORT "clk50m" IO_TYPE=LVCMOS33;IO_LOC "rst_n" 65; //k8IO_PORT "rst_n" IO_TYPE=LVCMOS33;IO_LOC "led[0]" 23;IO_LOC "led[1]" 24;IO_LOC "led[2]" 25;IO_LOC "led[3]" 26;IO_LOC "led[4]" 27;IO_LOC "led[5]" 28;IO_LOC "led[6]" 29;IO_LOC "led[7]" 30;IO_PORT "led[0]" IO_TYPE=LVCMOS33;IO_PORT "led[1]" IO_TYPE=LVCMOS33;IO_PORT "led[2]" IO_TYPE=LVCMOS33;IO_PORT "led[3]" IO_TYPE=LVCMOS33;IO_PORT "led[4]" IO_TYPE=LVCMOS33;IO_PORT "led[5]" IO_TYPE=LVCMOS33;IO_PORT "led[6]" IO_TYPE=LVCMOS33;IO_PORT "led[7]" IO_TYPE=LVCMOS33;至此,我们完成了流水灯例程的所有代码输入工作。双击GOWIN FPGA Designer主界面中的“Run All”工具按键,软件自动完成工程的综合及布局布线工作。如果代码输入正确,则软件界面左侧“Process”窗口中的“Synthesize”和“Place & Route”条目均会出现绿色的勾,表示程序综合及布局布线正确,如图4-10所示。

图4-10 程序综合及布局布线成功后的界面

4.5程序文件下载

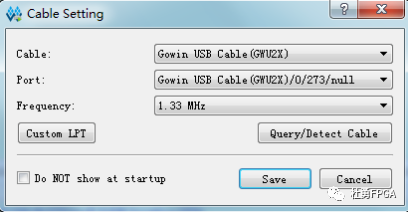

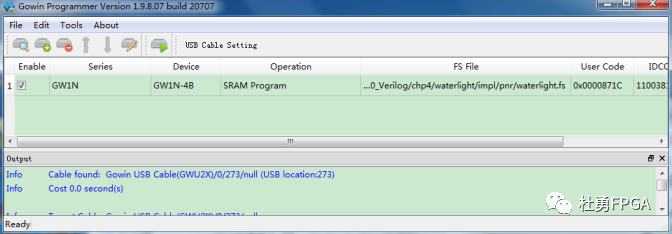

程序布局布线成功后,在工程目录的“implpnr”路径下会生成扩展名为fs的程序文件。对于流水灯工程实例来讲,生成的程序文件为waterlight.fs。采用USB线连接CGD100开发板和电脑,双击“ Program Device”条目,启动程序下载工具Gowin Programmer,同时弹出下载线设置对话框,如图4-11所示。

图4-11 程序下载线设置对话框

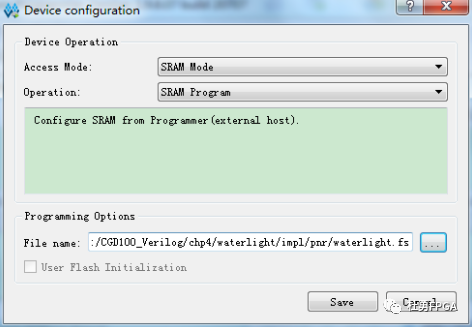

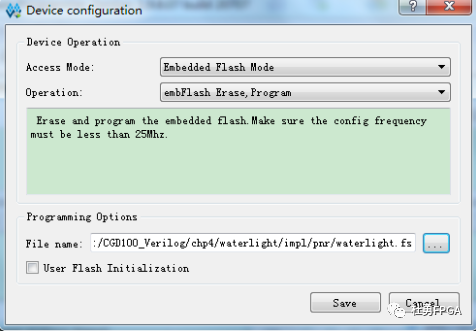

按图4-11设置下载线状态,单击“Save”,返回到Gowin Programmer界面。设置“Series”为GW1N,“Device”为GW1N-4B。单击“Operation”,打开下载模式设置界面。FPGA最主要的程序下载模式有两种:SRAM模式及Embedded Flash模式,前者模式在掉电后程序即丢失,后者模式在掉电后程序不丢失。对于SRAM模式来讲,在下载模式设置界面中,“Access Mode”选择SRAM Mode,“Operation”选择“SRAM Program”;对于Embedded Flash模式,在下载模式设置界面中,“Access Mode”选择Embedded Flash Mode,“Operation”选择“embFlash Erase,Program”。在“File name”编辑框中设置下载文件为工程布局布线后生成的waterlight.fs。两种程序下载模式的设置界面如图4-12、4-13所示。

图4-12 SRAM模式下载模式设置界面

图4-13 Embedded Flash下载模式设置界面

图4-14 Gowin Programmer配置界面

完成设置后的Gowin Programmer界面如图4-14所示。单击“Program/Configure”工具按钮即可完成程序的下载。程序下载完成后,可以观察到CGD100的8个LED灯呈现流水灯效果。

4.6 小结

本章以流水灯实例为例详细介绍了FPGA的设计流程。相对于AMD、Intel等FPGA厂商的FPGA开发环境来讲,高云云源软件的开发界面及流程都要简单得多,因此更适合FPGA初学者快速掌握FPGA的设计流程。本章的学习要点可归纳为:

(1)了解FPGA的设计流程,并将设计流程与PCB设计流程进行对比分析。

(2)掌握云源软件的基本使用方法及步骤。

(3)理解SRAM及Embedded Flash两种下载模式的特点。

审核编辑:汤梓红

-

基于Verilog FPGA 流水灯设计2017-08-09 17710

-

【紫光同创国产FPGA教程】【第二章】LED流水灯实验及仿真2021-02-02 9590

-

基于FPGA的音乐流水灯控制系统设计2011-10-20 5138

-

基于Verilog FPGA 流水灯设计_流水灯源码_明德扬资料2017-08-02 8564

-

如何上手FPGA实现简单的流水灯效果2022-01-18 1719

-

基于FPGA Vivado的流水灯样例设计资料分享2022-02-07 1092

-

LED流水灯程序【汇编版】2015-12-29 1325

-

利用FPGA DIY开发板控制流水灯功能实现2018-06-20 4022

-

数字设计FPGA应用:流水灯的设计2019-12-04 4498

-

使用FPGA实现流水灯的详细资料说明2019-07-11 1645

-

使用FPGA实现流水灯设计的资料合集2021-01-18 1280

-

详解基于FPGA的数字电路对流水灯的实验2021-03-19 5598

-

如何通过FPGA实现一个流水灯?2021-06-06 9562

-

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计2021-12-04 1000

-

基于FPGA开发板流水灯的设计实现2023-06-20 2282

全部0条评论

快来发表一下你的评论吧 !