关于有符号数据类型的示例

描述

我们学习一下Systemverilog中的有符号数据类型的赋值。

module top;

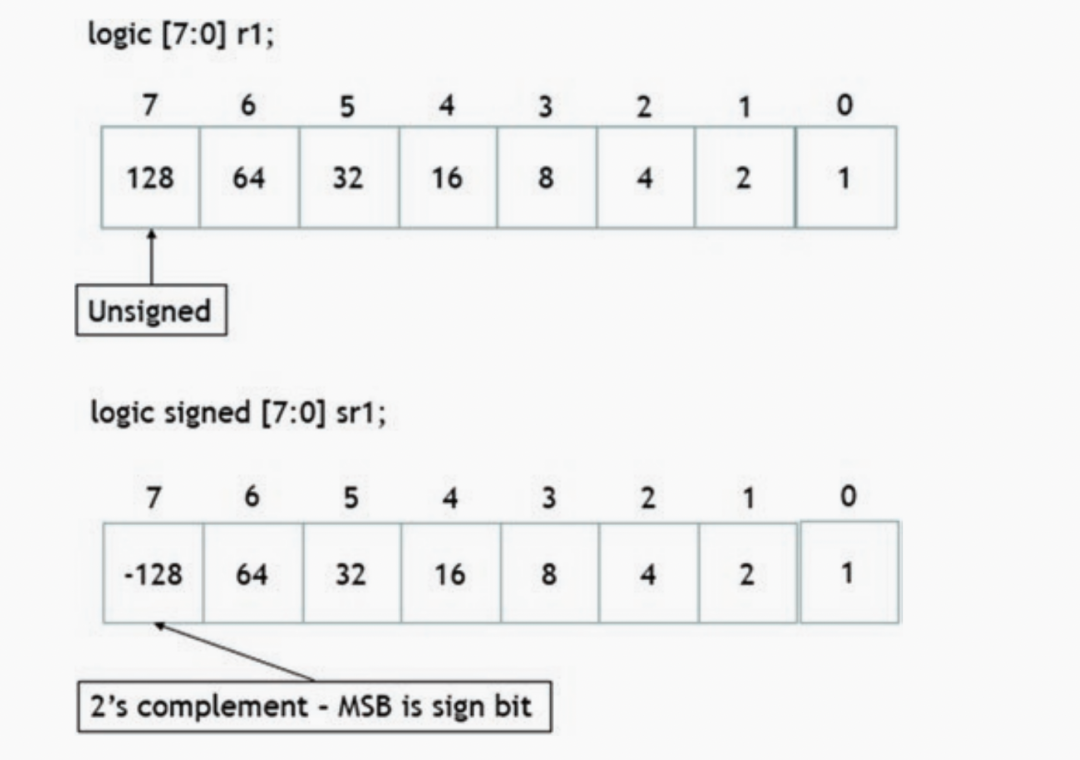

logic [7:0] r1;

logic signed [7:0] sr1;

initial begin

r1 = -2;

$display($stime,,,"r1=%d",r1);

sr1 = -2;

$display($stime,,,"sr1=%d",sr1);

r1 = r1+1;

$display($stime,,,"r1=%d",r1);

sr1 = sr1+1;

$display($stime,,,"sr1=%d",sr1);

end

endmodule

Simulation log:

# run –all # 0 r1=254 # 0 sr1= -2 # 0 r1=255 # 0 sr1= -1 # exit

" r1 "被声明为默认的无符号8位向量,而" sr1 "被声明为有符号8位向量。

当我们赋值r1 =−2时,因为“r1”是无符号的,所以它实际上会拿到值254(相当于十进制数字−2)。但是“sr1”会拿到值−2。

当我们给“r1”加一个1时,它的计算结果是255(254 + 1)。当我们给“sr1”加一个1时,它的计算结果是- 1(−2 + 1)。

默认情况下,logic, reg, wire,input,output都是无符号的,但是也可以声明为signed:

wire signed [7:0] w; module sm (input signed [7:0] iBus, output logic signed [7:0] oBus);

下面还有一些简单的示例:

logic signed [3:0] sr = -1; ( sr = 4’sb1111) logic signed [7:0] sr1 = 1; (sr1 = 8’sb00000001) logic [7:0] adds = sr + sr1; ( adds = 8’b00000000) logic [7:0] usr = 1; logic signed [7:0] s_add; s_add = sr + usr; (s_add = 15+1 = 8’sb00010000) (signed + unsigned = unsigned; sr is treated as unsigned 15)

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

关于verilog中的无符号数和有符号数2020-11-18 18634

-

采集的数据转换成有符号数的问题2012-05-02 6431

-

1.2FreeRTOS中的数据类型2020-07-22 1874

-

双状态无符号/有符号数据类型2021-01-18 2198

-

Verilog 变量声明与数据类型二2021-08-06 2119

-

SpinalHDL的UInt与SInt数据类型能够进行有符号/无符号数操作2022-07-14 4891

-

是否可以使用ActiveX API获取符号数据类型?2023-03-21 504

-

fpga 有符号数、无符号数2018-10-09 6923

-

plc位、字节、字、双字、有符号、无符号数据类型的关系2021-12-29 1597

-

汇编基础知识教程之数据类型与寄存器2023-01-30 1881

-

PLC数据类型2023-04-17 996

-

PLC数据类型汇总表2023-09-19 6042

-

FreeRTOS使用的数据类型有哪些2023-09-28 1715

-

Redis的数据类型有哪些2023-10-09 1684

-

verilog中数据的符号属性(有符号数和无符号数)探究根源2023-12-10 3282

全部0条评论

快来发表一下你的评论吧 !