SiP 封装优势及种类

制造/封装

描述

1 SiP

1.1 SiP 技术

SiP可以说是先进的封装技术、表面安装技术、机械装配技术的融合。根据ITRS(International Technology Roadmap for Semiconductors)的定义:系统级封装是多个具有不同功能的有源电子元件的组合,组装在一个单元中,提供与系统或子系统相关的多种功能。一个SiP可以选择性地包含无源器件、MEMS、光学元件以及其他封装和设备。

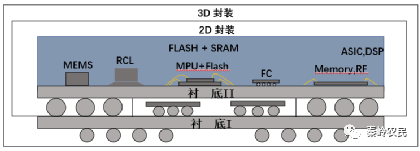

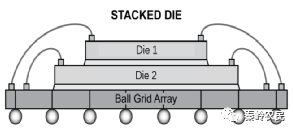

SiP 封装技术采取多种裸芯片或模块进行排列组装,若就排列方式区分可大体分为平面式2D封装和3D封装的结构。采用堆叠的3D技术可以增加使用晶圆或模块的数量,从而在垂直方向上增加可放置晶圆的层数,进一步增强SiP技术的功能整合能力;而其内部接合技术可以是单纯的线键合(Wire Bonding),也可使用倒装键合(Flip chip),也可二者混用。如下图2.17 SiP芯片封装示意图。

图2.17 SiP封装结构图

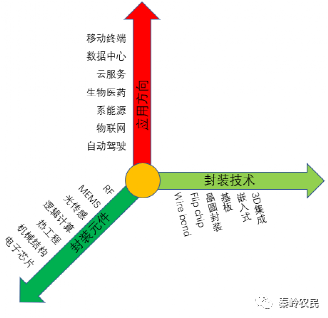

除了2D和3D的封装结构外,另一种以多功能性基板整合组件的方式,也可纳入SiP的范围。此技术主要是将不同组件内藏于多功能基板中,亦可视为是SiP的概念,达到功能整合的目的。不同的芯片,排列方式,与不同内部结合技术搭配,使SiP 的封装形态产生多样化的组合,并可按照客户或产品的需求加以客制化或弹性生产,如下图2.18所示。

图1 SiP封装技术

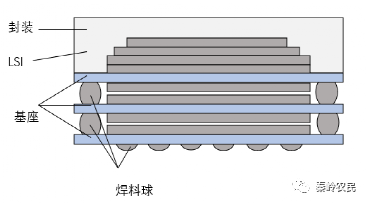

SiP技术路线表明,越来越多的半导体芯片和封装将彼此堆叠,以实现更深层次的3D封装。图2.19 是8芯片堆叠SiP,将现有多芯片封装结合在一个堆叠中。微晶片的减薄化是SiP增长面对的重要技术挑战。现在用于生产200mm和300mm微晶片的焊接设备可处理厚度为50um的晶片,因此允许更密集地堆叠芯片。

图2 8芯片堆叠SiP

1.2 SiP 封装优势

在IC封装领域,是一种先进的封装,其内涵丰富,优点突出,已有若干重要突破,架构上将芯片平面放置改为堆叠式封装,使密度增加,性能大大提高,代表着凤凰技术的发展趋势,在多方面存在极大的优势特性,体现在以下几个方面。

1)SiP 实现是系统的集成。采用要给封装体来完成一个系统目标产品的全部互联以及功能和性能参数,可同时利用引线键合与倒装焊互连技术以及别的IC芯片堆叠等直接内连技术,将多个IC芯片与分立有源和无源器件封装在一个管壳内。

2)封装面积增大,SiP在同一个封装种叠加两个或者多个芯片。把垂直方向的空间利用起来,同时不必增加引出管脚,芯片叠装在同一个壳体内,整体封装面积大大减少。

3)采用超薄的芯片堆叠与TSV技术使得多层芯片的堆叠封装体积减小,最先进的封装技术可以实现多层芯片堆叠厚度。

4)SiP 可将不同的材料,兼容不同的GaAs,Si,InP,SiC,陶瓷,PCB等多种材料进行组合进行一体化封装。

5)所有元件在一个封装壳体内,缩短了电路连接,见笑了阻抗、射频、热等损耗影响。提高了光,电等信号的性能。

6)短产品研制和投放市场的周期,SiP在对系统进行功能分析和划分后,可充分利用商品化生产的芯片资源,经过合理的电路互连结构及封装设计,易于修改、生产,力求以最佳方式和最低成本达到系统的设计性能,无需像SoC那样进行版图级布局布线,从而减少了设计、验证、调试的复杂性与系统实现量产的时间,可比SoC节省更多的系统设计和生产费用,投放市场的时间至少可减少1/4;

1.3 SiP 封装种类

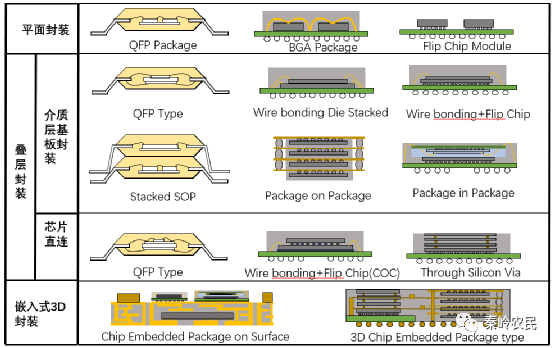

SiP涉及许多类型的封装技术,如超精密表面贴装技术(SMT)、封装堆叠技术,封装嵌入式技术、超薄晶圆键合技术、硅通孔(TSV)技术以及芯片倒装(Flip Chip)技术等。 封装结构复杂形式多样,图2.20所示为基本的几种分类形式。

图3 SiP几种分类形式

从上面也可以看到SiP是先进的封装技术和表面组装技术的融合。SiP并没有一定的结构形态,芯片的排列方式可为平面式2D装和立体式3D封装。由于2D封装无法满足系统的复杂性,必须充分利用垂直方向来进一步扩展系统集成度,故3D成为实现小尺寸高集成度封装的主流技术。3D主要有三种类型:埋置型、有源基板型、叠层型。其中叠层型是 当前广泛采用的封装形式。叠层型是在2D基础上,把多个裸芯片、封装芯片、多芯片组件甚至圆片进行垂直互连,构成立体叠层封装。可以通过三种方法实现:叠层裸芯片封装、封装堆叠直连和嵌入式3D封装。业界认定3D封装是扩展SiP应用的最佳方案,其中叠层裸芯片、封装堆叠、硅通孔互连等都是当前和将来3D封装的主流技术。

并排放置(平面封装)的 SiP 是一种传统的多芯片模块封装形式,其中使用了引线键合或倒装芯片键合技术。这种结构的主要优点是使数据传输率更高。对于具有 GHz 级信号传输的高性能应用,导体损耗和介电损耗会引起信号衰减,并导致低压差分信号中的眼图不清晰。信号走线设计的足够宽以抵消GHz传输的集肤效应,但走线的物理尺寸,包括横截面尺寸和介电层厚度都要精确制作,以更好的与spice模型模拟相互匹配。另一方面,晶圆工艺的进步伴随着核心电压较低的器件,这导致噪声容限更小,最终导致对噪声的敏感性增加。散布在芯片上的倒装凸块可作为具有稳定参考电压电平的先进芯片的稳定电源传输系统。

对于堆叠结构,可以区分如下几种:芯片堆叠、PoP、PiP、TSV。

1)堆叠芯片

是一种两个或更多芯片堆叠并粘合在一个封装中的组装技术。这最初是作为一种将两个内存芯片放在一个封装中以使内存密度翻倍的方法而开发的。 无论第二个芯片是在第一个芯片的顶部还是在它旁边,都经常使用术语“堆叠芯片”。技术已经进步,可以堆叠许多芯片,但总数量受到封装厚度的限制。芯片堆叠技术已被证明可以多达 24 个芯片堆叠。然而,大多数使用9 芯片高度的堆叠芯片封装技术的来解决复杂的测试、良率和运输挑战。芯片堆叠也广泛应用在传统的基于引线框架的封装中,包括QFP、MLF 和 SOP 封装形式。如下图2.21的堆叠芯片封装形式。

图4 堆叠芯片封装结构

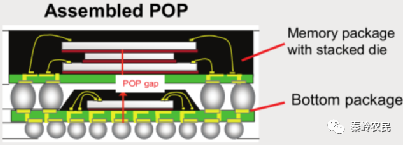

2)PoP(Package-on-Package)

是用于将逻辑器件和存储器器件进行叠层封装的技术。通常情况下底层多为逻辑器件,例如移动电话基带(调制解调器)处理器或应用处理器,上层为存储器,例如闪存或者叠层内存芯片。显然,这种垂直组合封装的一个优点是节省了电路板空间。适用于需要在更小空间内实现更多功能的应用,例如数码相机、PDA、MP3 播放器和移动游戏设备等。

图5 PoP芯片封装结构

PoP封装技术有以下几个有点:

1)存储器件和逻辑器件可以单独地进行测试或替换,保障了良品率;

2)双层POP封装节省了基板面积, 更大的纵向空间允许更多层的封装;

3)可以沿PCB的纵向将Dram,DdramSram,Flash,和 微处理器进行混合装联;

4)对于不同厂家的芯片, 提供了设计灵活性,可以简单地混合装联在一起以满足客户的需求,降低了设计的复杂性和成本;

5)目前该技术可以取得在垂直方向进行层芯片外部叠加装联;

6)顶底层器件叠层组装的电器连接,实现了更快的数据传输速率,可以应对逻辑器件和存储器件之间的高速互联。

POP的工艺流程

PoP的组装方式目前有两种。一种是预制PoP工序,即先将PoP的多层封装堆叠到一起,焊接成一个元器件,再贴装到PCB上,最后再进行一次回流焊。一种是在板PoP工序上,依次将底部的BGA和顶部BGA封装在PCB上,然后过一次回流焊。

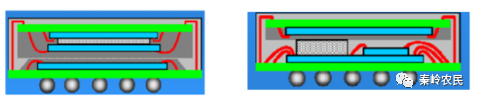

3)PiP (Package In Package)

一般称堆叠封装又称封装内的封装,还称器件内置器件,是在同一个封装腔体内堆叠多个芯片形成3D 封装的一种技术方案。封装内芯片通过金线键合堆叠到基板上,同样的堆叠,通过金线再将两个堆叠之间的基板键合,然后整个封装成一个元件便是PiP(器件内置器件)。PiP封装技术最初是由KINGMAX公司研发的一种电子产品封装技术,该技术整合了PCB基板组装及半导体封装制作流程,可以将小型存储卡所需 要的零部件(控制器、闪存集成电路、基础材质、无源计算组件)直接封装,制成功能完整的Flash存储卡产 品。PiP一体化封装技术具有下列技术优势:超大容量、高读写速度、坚固耐用、强防水、防静电、耐高温等, 因此常运用于SD卡、XD卡、MM卡等系列数码存储卡上。

PiP封装的优点:

1)外形高度较低;

2)可以采用标准的SMT电路板装配工艺;

3)单个器件的装配成本较低。

PiP封装的局限性

(1)由于在封装之前单个芯片不可以单独测试,所以总成本会高(封装良率问题);

(2)事先需要确定存储器结构,器件只能有设计服务公司决定,没有终端使用者选择的自由。

图2.23 PiP封装结构

4)TSV

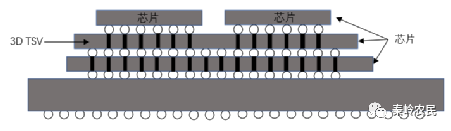

W2W的堆叠是将完成扩散的晶圆研磨成薄片,逐层堆叠而成。层与层之间通过直径在10µm以下的细微通孔而实现连接。此种技术称为TSV(Through silicon via)。与常见IC封装的引线键合或凸点键合技术不同,TSV能够使芯片在三维方向堆叠的密度更大、外形尺寸更小,并且大大改善芯片速度和降低功耗,成为3D芯片新的发展方向。如图2.24所示,堆叠的三层芯片通过硅通道互连。

图6 3D芯片TSV堆叠

-

SiP蓝牙芯片在项目开发及应用中具有什么优势?2025-02-19 4893

-

SIP封装技术:引领电子封装新革命!2025-01-15 3837

-

传统SIP封装中的SIP是什么?2023-05-19 4641

-

SiP封装的优势及应用2023-04-13 2729

-

陶瓷封装SiP腔体结构介绍2023-02-10 6247

-

系统级封装SiP在PCB的设计优势2022-08-09 2875

-

SIP封装和采用SiP工艺的DFN封装是什么2021-09-22 9235

-

SiP与Chiplet成先进封装技术发展热点2020-09-17 10955

-

SIP系统封装技术浅析2020-05-28 3708

-

基于LTCC技术实现SIP的优势和特点讨论2019-07-29 2857

-

求SIP封装厂家2015-11-08 12297

-

SIP(封装系统),SIP(封装系统)是什么意思2010-03-26 20917

-

SIP封装2006-04-01 1968

全部0条评论

快来发表一下你的评论吧 !