什么是Chiplet技术?chiplet芯片封装为啥突然热起来

制造/封装

描述

最近两天经常看到Chiplet这个词,以为是什么新技术呢,google一下这不就是几年前都在提的先进封装吗。最近资本市场带动了芯片投资市场,和chiplet有关的公司身价直接飞天。带着好奇今天扒一扒chiplet是什么:

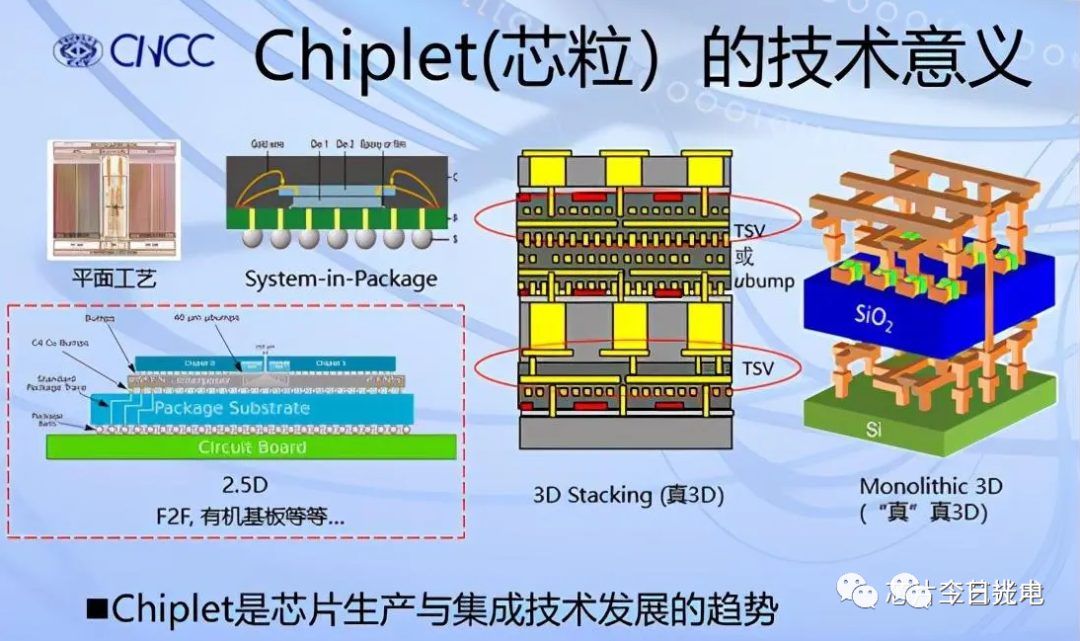

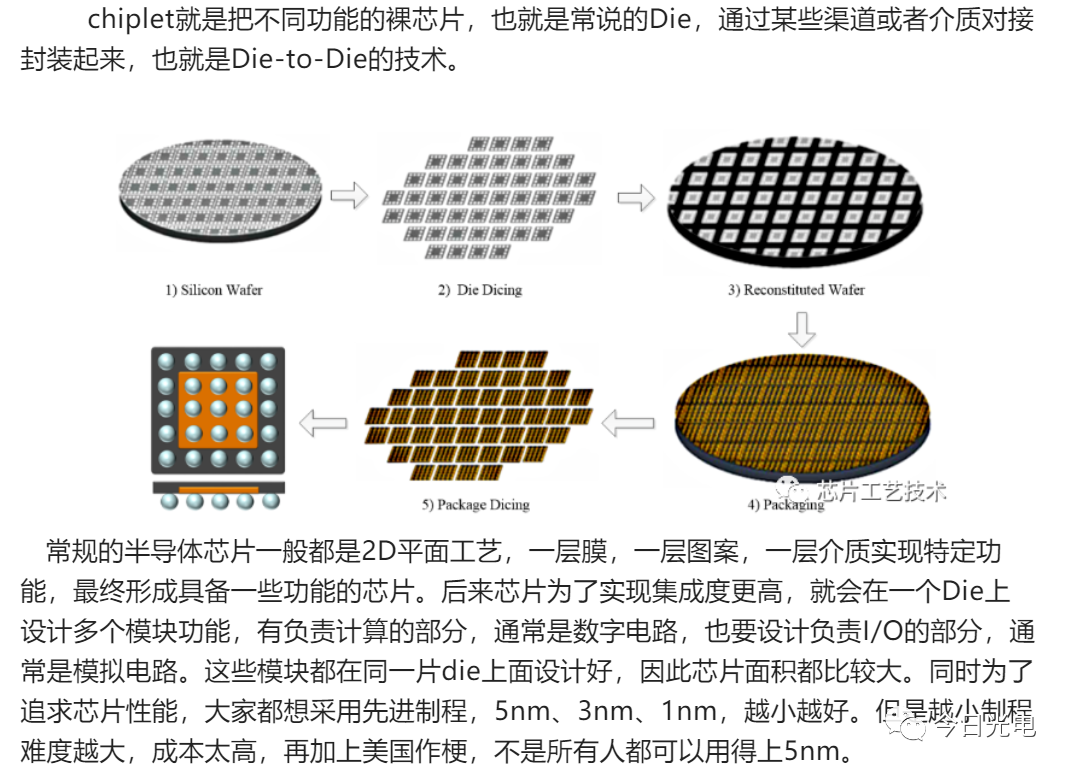

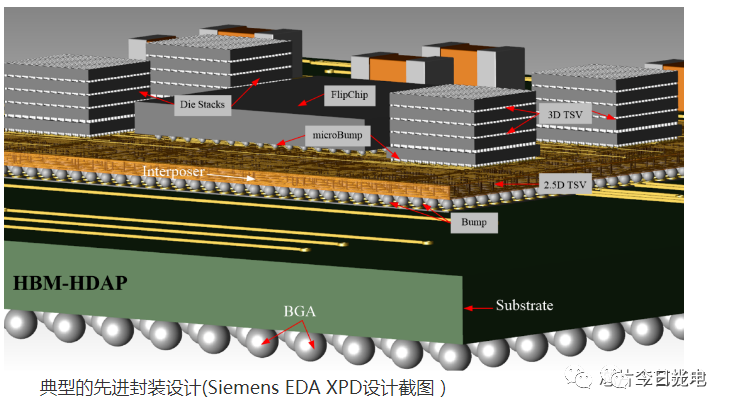

Chiplet的概念其实很简单,就是硅片级别的重用。从系统端出发,首先将复杂功能进行分解,然后开发出多种具有单一特定功能、可相互进行模块化组装的裸芯片,如实现数据存储、计算、信号处理、数据流管理等功能,并最终以此为基础,建立一个Chiplet的芯片网络。

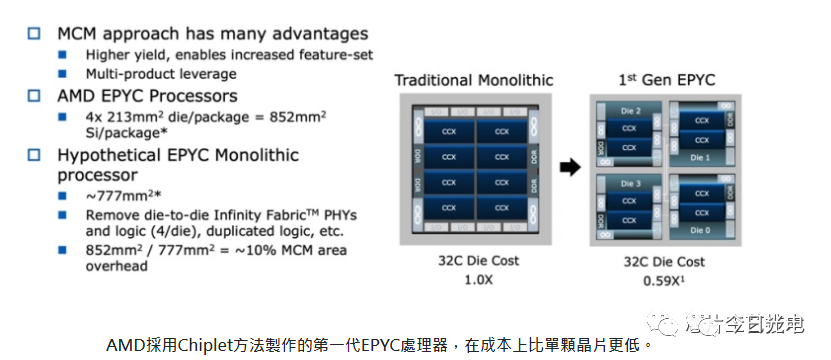

其实对于芯片,数字电路采用先进制程可以明显提高运算性能,但是模拟电路采用先进制程性能提升并不大,有点浪费。

因此就可以想,把本来一个大的die,切割成两块或者多块。数字电路部分采用新制程,模拟电路采用老制程,这样既简化了设计步骤,又提高了先进制程的利用率,I/O模块也更经济。

另外采用chiplet降低了单位面积内的芯片设计量,可以适当减少芯片集成度,我的理解是采用14nm的工艺制程说不定可以干5nm的事情。

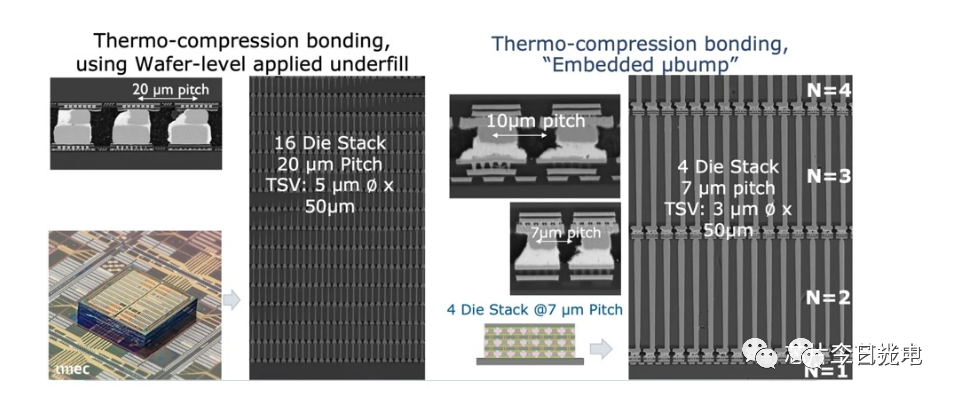

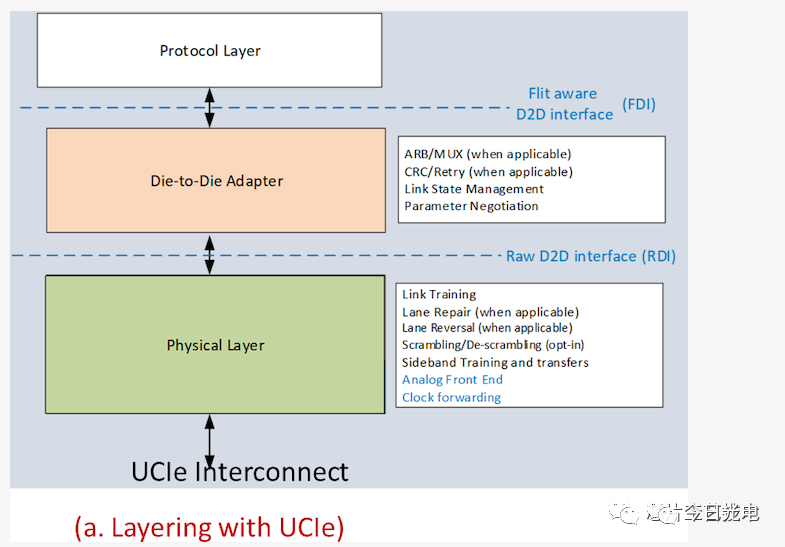

明白了为什么采用chiplet,但是如何用chiplet,就需要die和die之间的互联了。和我们做电路一样的,芯片之间的互联也需要协议,特别是对于这种先进封装,并没有行业规定,每个芯片厂家设计的金属对接口位置可能都不同,因此急需一个标准的出台。

2022年三月份出现的UCIe, 即Universal Chiplet Interconnect Express,是Intel、AMD、ARM、高通、三星、台积电、日月光、Google Cloud、Meta和微软等公司联合推出的Die-to-Die互连标准,其主要目的是统一Chiplet(芯粒)之间的互连接口标准,打造一个开放性的Chiplet生态系统。UCIe在解决Chiplet标准化方面具有划时代意义。

到目前为止,已经成功商用的Die-to-Die互连接口协议多达十几种,主要分为串行接口协议和并行接口协议。比较而言,串行接口一般延迟比较大,而并行接口可以做到更低延迟,但也会消耗更多的Die-to-Die互连管脚;而且因为要尽量保证多组管脚之间延迟的一致,所以每个管脚不易做到高速率。

UCIe 成员分为三个级别:发起人、贡献者和采用者。发起人由董事会组成并具有领导作用。贡献者和发起者公司可以参与工作组,而采用者只能看到最终规范并获得知识产权保护。

贡献者成员名单如下:

来源:芯片工艺技术:感谢原创作者的辛勤付出

-

半导体芯片先进封装——CHIPLET2022-10-06 31227

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1497

-

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet2021-01-04 61059

-

光芯片走向Chiplet,颠覆先进封装2022-08-24 3335

-

先进封装Chiplet全球格局分析2023-01-05 1756

-

什么是Chiplet?Chiplet与SOC技术的区别2023-03-29 4114

-

Chiplet技术给EDA带来了哪些挑战?2023-04-03 974

-

先进封装Chiplet的优缺点与应用场景2023-06-13 2317

-

半导体Chiplet技术及与SOC技术的区别2023-05-16 3064

-

探讨Chiplet封装的优势和挑战2023-07-06 1313

-

Chiplet关键技术与挑战2023-07-17 2532

-

Chiplet主流封装技术都有哪些?2023-09-28 3297

-

先进封装 Chiplet 技术与 AI 芯片发展2023-12-08 2559

-

什么是Chiplet技术?2024-01-25 4519

-

解锁Chiplet潜力:封装技术是关键2025-01-05 2573

全部0条评论

快来发表一下你的评论吧 !