是否有一种最佳的方法来进行封装内的Die测试以减少测试时间

描述

年度ITC活动于9月的最后一周举行,我们一直在关注来自EDA供应商的所有新闻亮点,因为花在测试器上的时间可能是一个主要成本,而在生产过程中发现缺陷芯片的价值是非常关键的。小芯片、2.5D和3D IC设计已经引起了测试界的关注,我们了解到西门子EDA刚刚宣布用他们的DFT方法来解决新的测试需求。Vidya Neerkundar是DFT产品Tessent系列的产品经理,她介绍了最新情况。

DFT的挑战

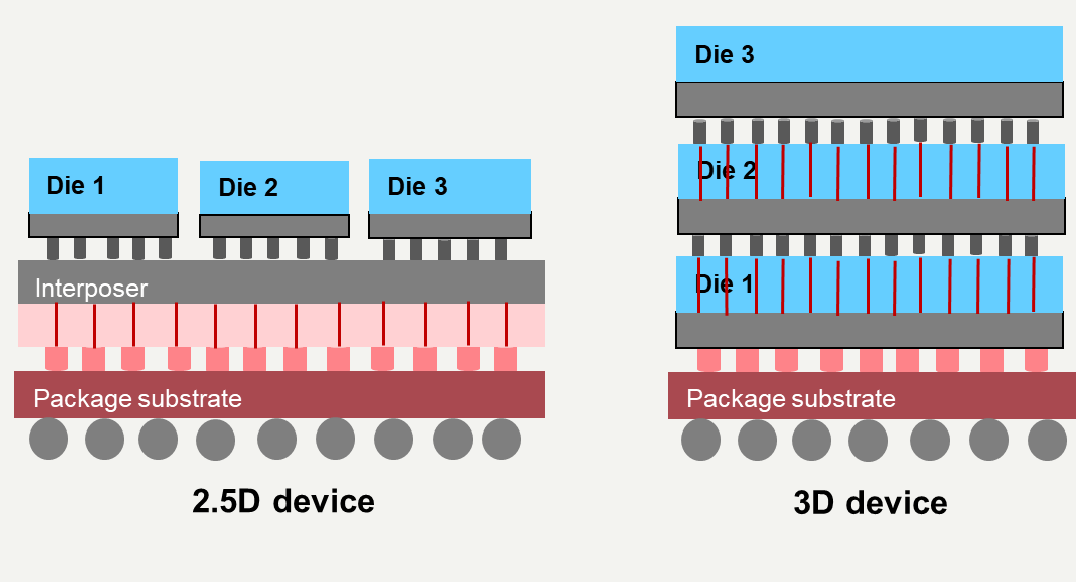

在IC设计的大部分历史中,一个封装中都只有一个Die,或者是多芯片模块(MCM)。对于有多个Die的2.5D和3D IC,如何进行单独的Die测试,然后使它们适用于最终的封装?

如果其中每个Die的DFT架构彼此不同呢?

是否有一种最佳的方法来进行封装内的Die测试,以减少测试时间?

2.5D和3D小芯片

Tessent Multi-die

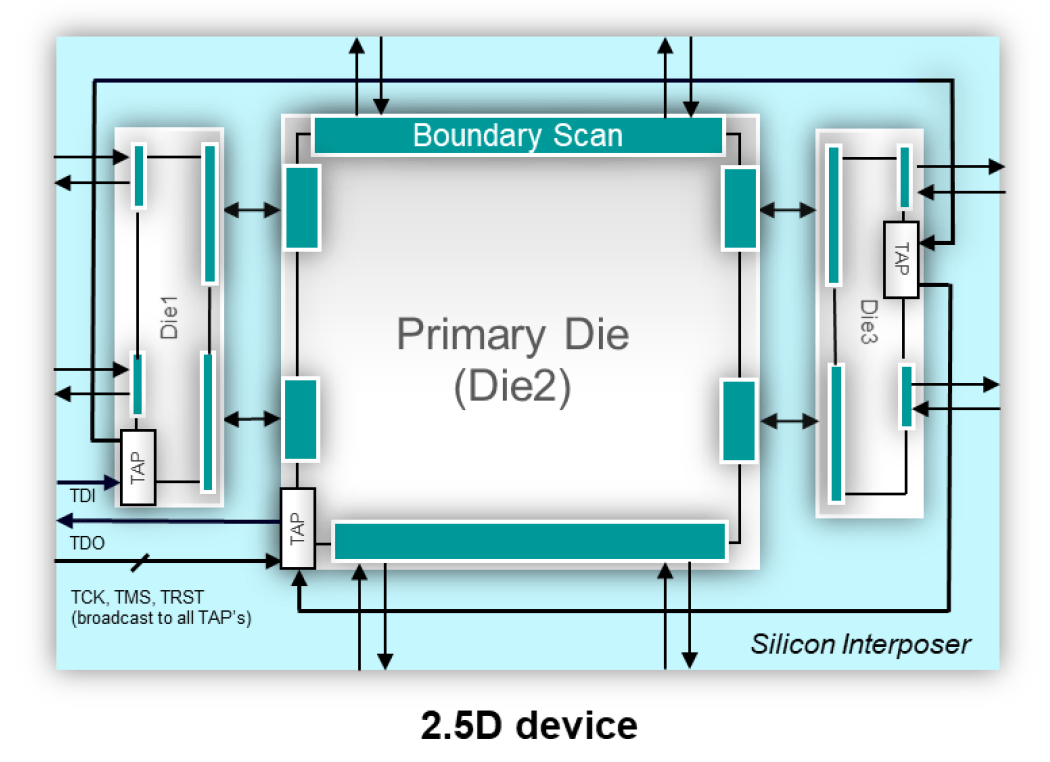

西门子的开发团队扩展了他们的技术,支持使用Tessent Multi-die 的2.5D和3D IC封装。Tessent流扫描网络使用2D分层扫描测试。现在,这种方法将2D分层DFT扩展到2.5D和3D IC。以下是2.5D设备中三个小芯片的情况:

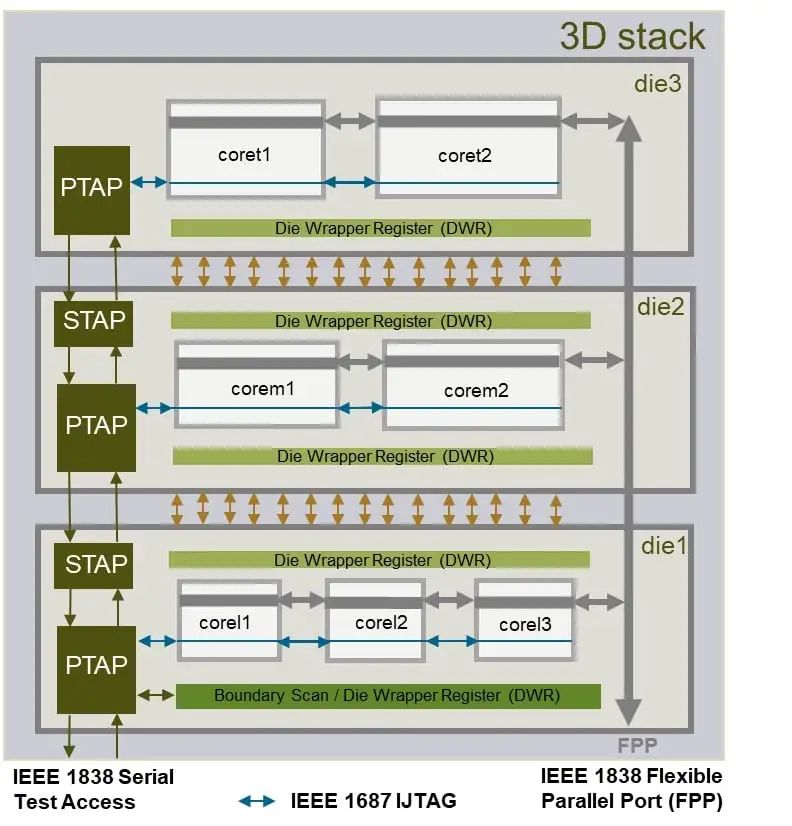

IEEE为3D堆叠集成电路的测试访问架构创建了一个标准,称为IEEE 1838-2019。IEEE 1687使用另一个标准IEEE 1149.1定义了集成电路内嵌入仪器的访问和控制,该标准带有测试访问端口。Tessent Multi-die支持所有这些标准。

芯片设计中的每个Die都有一个边界扫描描述语言(BSDL)文件,然后Tessent Multi-die将创建包级BSDL。

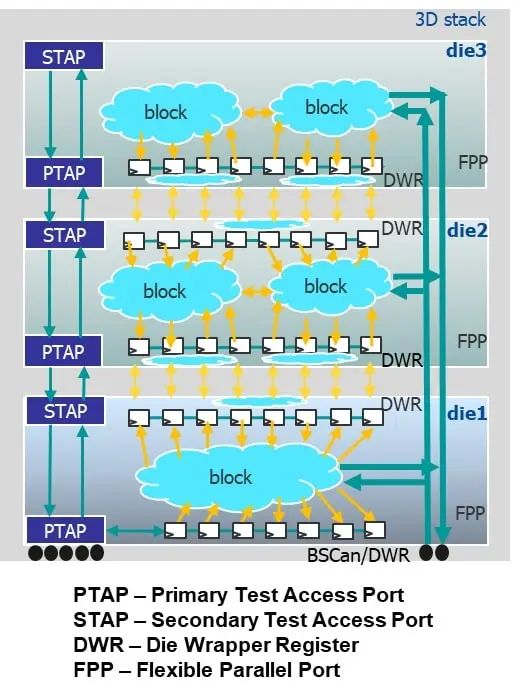

IEEE 1838标准

该以Die为中心的测试标准于2019年11月获得委员会批准,并允许将一个Die作为多Die堆栈的一部分进行测试。为了测试目的,使用一个柔性并行端口(FPP)、Die包装寄存器(DWR)和测试访问端口(TAP)连接Die的3D堆栈:

用于测试的3D堆栈

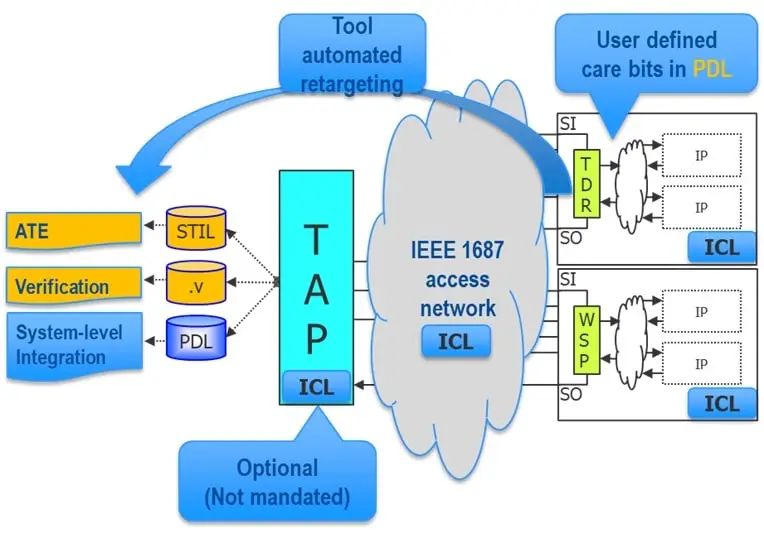

IEEE 1687 -内部JTAG

这个2014年的标准有助于简化嵌在每个Die内的仪器的使用。有一种仪器连接语言(ICL)和过程描述语言(PDL)来定义仪器。ATE系统和内部JTAG之间的流程如下所示:

IEEE 1687流

IEEE 1149.1 JTG

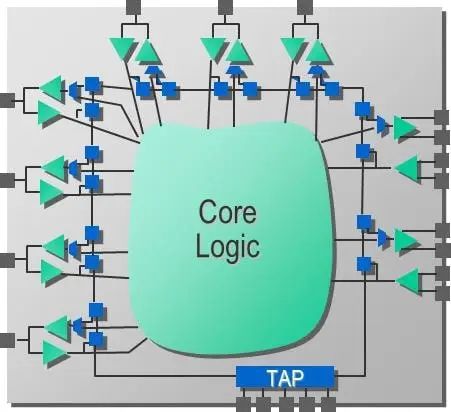

带有测试访问端口的边界扫描标准可以追溯到1990年,边界扫描描述语言(BSDL)出现于2001年。该标准定义了指令和测试数据如何在芯片内部流动。

IEEE 1149.1 JTAG

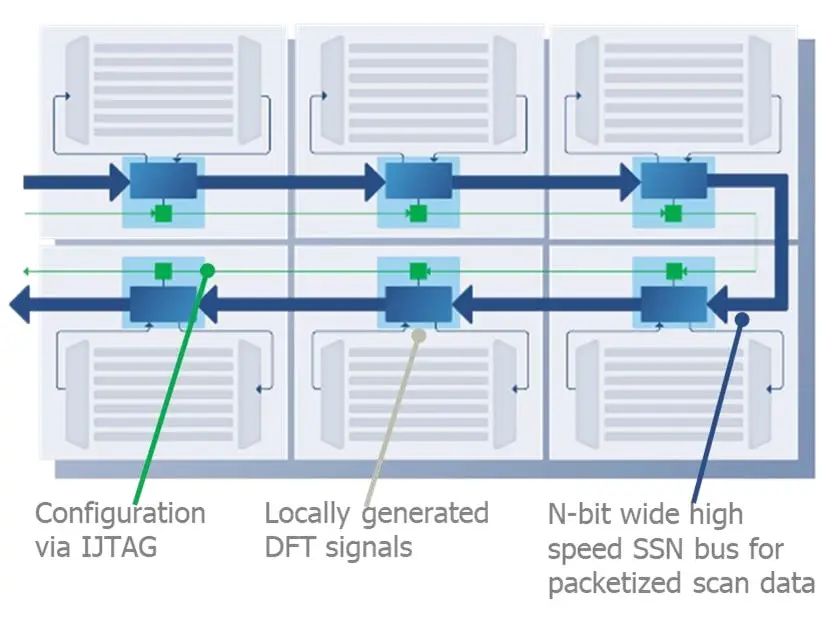

将所有这些测试标准放在一起,我们可以看到Tessent Multi-die如何连接到3D堆栈中的每个芯片。每个Die内核的测试模式和测试调度是通过Tessent流扫描网络(SSN)完成的。

Tessent流扫描网络

SSN基本上是将测试数据传输分组,从而将核心DFT和芯片DFT解耦,允许同时测试的核心独立移动。实际的好处是为DFT规划节省时间,更容易进行路由和定时关闭,并最多可以减少4倍的测试时间。

总结

代工厂、设计、测试和IEEE之间的密切合作创造了一个充满活力的2.5D和3D生态系统,所有的技术都已到位,以推进半导体创新。西门子EDA在使用IEEE标准的同时扩展了他们的Tessent软件,以接受新的测试挑战。Tessent Multi-die与所有其他的Tessent产品和平台集成在一起,因此我们不必将工具和流程拼凑在一起。

审核编辑:刘清

-

一种新的PCB测试技术:边界扫描测试技术2018-09-10 2918

-

什么是电缆测试以及如何完成电缆测试2018-10-26 1710

-

什么是保护装置测试以及如何完成2018-11-02 1701

-

是否有一种方法来确定GPIF接口在等待GPIF主机的数据时干还是空2019-05-27 1390

-

天线测试及评估有哪些方法?2019-08-07 2730

-

天线测试有哪些方法?2019-08-08 2306

-

如何使用Die-to-Die PHY IP 对系统级封装 (SiP) 进行高效的量产测试?2020-10-25 3725

-

软件驱动程序是否有一种相当简单的方法来检测安装了哪个rtc设备?2023-04-06 606

-

ESP32C3射频测试,是否需要使用Wi-Fi Adaptivity方法来进行Wi-Fi范围测试?2023-04-12 783

-

加密场景下的一种测试方法2017-09-07 735

-

用自动测试方法来替代手工接线测试,对网分测试端口进行扩展2018-03-20 10316

-

通过解决测试时间减少ASIC设计中的DFT占用空间2022-06-02 3051

-

最后一种方法来整理你的电阻器2022-12-19 719

-

QT原生的QJson是否有更优雅的方法来封装一些Json对象2023-10-08 3278

-

一种简单的方法来将振荡器相位噪声转换为时间抖动2023-11-23 488

全部0条评论

快来发表一下你的评论吧 !