低损耗高效率高耐压,荣湃Pai8131性能解析

描述

半桥是由两个功率器件(如MOSFET)以图腾柱的形式连接,以中间点作为输出,提供方波信号。这种结构在 PWM 电机控制、DC-AC逆变、电子镇流器等场合有着广泛的应用。而从应用领域的角度来说,其应用也十分广泛,分布于AC-DC商用电源-服务器和工作站、消费类电子、工业电机、医疗电子、家用设备等。

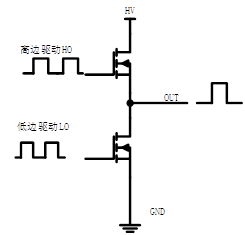

图1:以MOSFET构成的两种半桥结构

图1显示了两种以MOSFET构成的半桥结构。左边结构上端是P沟道MOSFET,和下端N沟道MOSFET相连,公共端漏极作为输出;右边结构上端是N沟道MOSFET,和下端N沟道MOSFET相连。当然,如今很多场合,特别是大功率领域,NMOS由于其更低的导通电阻RDS(ON),几乎完全替换掉了上端的PMOS。

工作原理简介

以图1右边的结构为例,高边MOS导通时,低边MOS不通。同样地,低边MOS导通时,高边MOS不通。

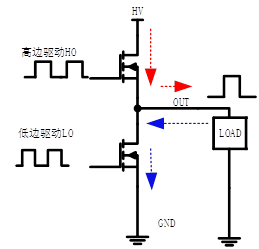

高边MOS和低边MOS由驱动器驱动,当驱动器的输出HO为高时,高边MOS导通,OUT电压几乎等于HV。其电流路径为,从HV流经高边MOS,最后流向外部负载,如图2中红色箭头;

当驱动器的输出LO为高时,低边MOS导通,OUT电压几乎等于零。其电流路径为,从负载流向低边MOS,如图2中蓝色箭头。

图2:半桥结构中不同功率管导通时的电流路径

死区时间

前面提到了半桥结构中的高低边MOS的工作情况,高边MOS和低边MOS是分时导通的,输出才能相应产生一个方波,驱动后级负载。思考一个问题,假设在高边MOS导通的时候,低边驱动信号LO因为某些原因,如干扰或驱动器内部其他问题等异常拉高了,此时低边MOS也会导通,由于低边MOS对地提供了一个更低阻抗的回路,电流直接从高边MOS流向低边MOS。这显然会对输出造成影响,严重的情况下,甚至可能造成MOS管失效,整个系统被彻底损坏。

因此,考虑到MOS的关断时间和高低边驱动器内部反向器的延时以及失配等问题,实际的驱动器都会设置死区时间。所谓的死区时间,就是上下管不允许同时导通的时间,分别位于上管关断到下管导通,下管关断到上管导通。当高边MOS关断后,死区功能被触发,只有经过死区时间DT之后,低边MOS才允许导通。同样,低边MOS关断后,同样要经过死区时间DT之后,高边MOS才允许导通。

系统效率和EMI的考虑

半桥结构无论是应用于什么场景,半桥拓扑也好,还是普通的DC-DC拓扑,或者是其他的电机应用,本质上都是对能量进行变换。这就涉及到一个转换效率的问题。就半桥结构而言,绝大部分的损耗,都集中在高低边MOS的开关损耗。一般而言,开关管损耗包括两个部分:

01

导通损耗

MOS管导通之后本身的导通电阻产生的损耗,其正比于MOS管的导通电阻RDS(ON),降低导通电阻就能直接降低这一部分损耗。

02

交越损耗

MOS管导通过程的损耗。

实际的MOS管由于其物理结构的原因,存在极间电容,Cgs、Cds、Cgd。这几个电容的存在,导致整个MOS管的导通过程不能瞬间完成,实际上MOS管的导通过程也比较复杂,详细的导通过程这里也不做介绍。如果基于简单的模型的话,MOS管的导通过程其实就是Cgs充电的过程,Vgs缓慢上升直到超过阈值电压Vgs(th),源漏开始导通。

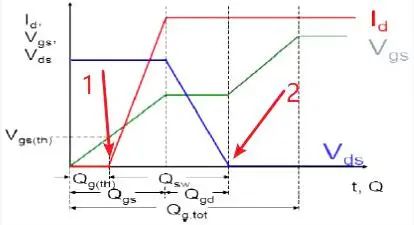

图3:开关管导通过程的简单模型

如图3,源漏电流Id的上升和源漏电压Vds的下降均有一个过程,这部分就是交越损耗。意味着,Vgs上升越慢,VDS下降就约满,交越损耗就越大。因此,简单来说,Vgs电压上升速率越快,交越损耗就越低。另外,交越损耗还直接受频率的影响,频率越高,损耗越大。

实际上,还有一部分损耗,即驱动损耗,一般而言驱动损耗相对约导通损耗和交越损耗而言可以忽略不计,这里也不作介绍。当MOS管选定之后,其导通电阻也已经固定,导通损耗这一部分已经无法改变,要想提高效率,必须要从交越损耗这部分入手。提高驱动电压的斜率,就是最直接的办法。

EMC/EMI

所有的开关系统,几乎都面临着电磁干扰的问题。功率开关管工作在On-Off 快速循环转换的状态,dv/dt和di/dt都在急剧变换,因此,功率开关管既是电场耦合的主要干扰源,也是磁场耦合的主要干扰源。

在电路中的电感及寄生电感中快速的电流变化产生磁场从而产生较高的电压尖峰:UL=L*di/dt;在电路中的电容及寄生电容中快速的电压变化产生电场从而产生较高的电流尖峰:ic=C*du/dt。磁场和电场的噪声与变化的电压和电流及耦合通道如寄生的电感和电容直接相关。直观的理解,减小电压变化率du/dt和电流变化率di/dt及减小相应的杂散电感和电容值可以减小由于上述磁场和电场产生的噪声,从而减小EMI干扰。

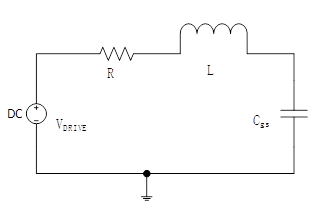

图4:驱动到栅极的等效电路

实际的PCB由于走线等因素,必然会引入寄生电感,这些寄生电感的引入导致原本的RC一阶电路直接变为RLC二阶电路。如果为了尽可能的降低损耗而将激励的斜率设置很高,则响应很有可能会出现振铃现象,甚至于出现谐振现象,无论是上述两种情况中的哪一种,都会带来头疼的EMI问题,甚至于系统不工作。因此,必须要在降低损耗和减小EMI二者之间做折衷处理。处理的方式就如图4,增加驱动电阻R,以增加阻尼系数。一般考虑设置阻尼系数为0.707,刚好处于临界阻尼状态。

荣湃推出基于独创的iDivider技术的半桥驱动芯片——Pai8131,很好的满足了这些问题。为了防止高低边MOS共通,一方面,Pai8131半桥驱动芯片提供520ns的典型死区时间,屏蔽了上下驱动电路的反向器失配带来的影响;另外一方面,Pai8131提供最大100V/ns的共模瞬态耐受能力。当HS端对COMM端存在100V/ns的共模干扰时,驱动信号依然不会出错,保证系统正常工作。

另外,Pai8131提供0.29A/0.6A的source/sink能力,在驱动高低边MOS时,能够更快的让驱动电压达到开启阈值Vgs(th),让MOS能够更快的导通,尽可能的降低交越损耗,提高系统转换效率。

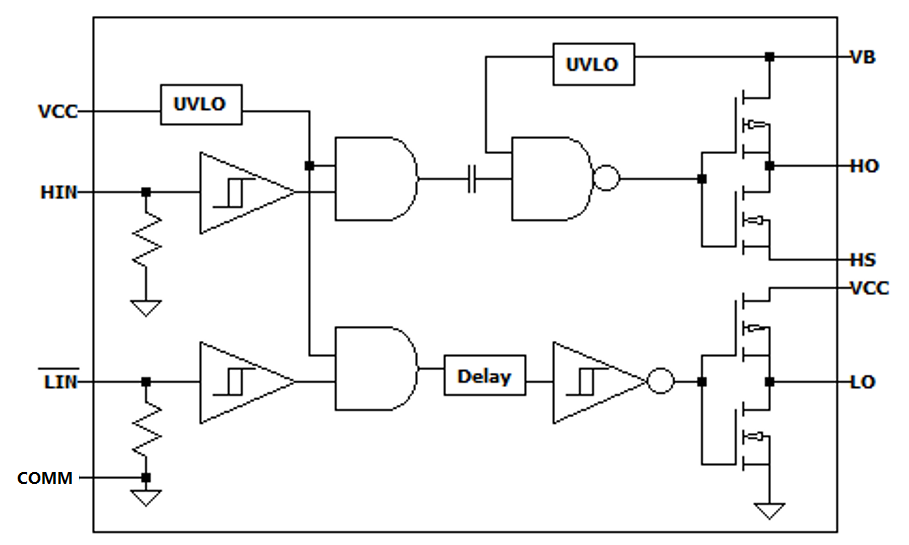

图5:Pai8131系统框图

Pai8131还创新性地将容隔技术应用于高边驱动,使用电容隔离来替代常规的level shift。在实现电平转换的同时,还提供了极高的高低边驱动信号之间的耐压能力,标称耐压可达-700~+700V。

其他性能参数如下:

耐受负向瞬态电压

100 dV/dt 耐受能力

栅极驱动器电源范围10~20V

内置UVLO功能

3.3V、5V、15V逻辑电平兼容

互通预防功能

两个通道传播延时匹配

内部设置死区时间

Pai8131提供了常规的高性价比的NB SOIC8的小封装,还提供一个低至400uA的静态电流,在驱动器不工作时,保证了极低的静态功耗。在能源问题越来越严重的当下,凭借其优异的性能和极低的成本,成为各相关应用领域的优先选择。

审核编辑 :李倩

-

实现工业设备的辅助电源应用要求的高耐压与低损耗2018-12-05 2075

-

高效率高线性的功放怎么实现?2019-09-17 3615

-

高效率同步降压芯片 高耐压--ZCC1496完全替代MP14962019-11-21 1645

-

高效率 同步降压芯片,高耐压--ZCC1496完全替代MP14962019-11-23 2546

-

高耐压 高效率 同步降压芯片 ZCC1496完全替代MP14962019-12-04 2358

-

针对高输出阻抗能源的低损耗全波桥和高效率降压转换器2020-05-08 1544

-

代理荣湃2PAI π160M60六通道数字隔离器 增加ESD功能 电机控制 隔离式开关电源方案使用2021-06-30 1079

-

高效率高功率密度电力电子技术及案例分析2021-07-22 1230

-

荣湃开发隔离驱动器Pai8233系列产品2022-04-01 3468

-

荣湃最新推出半桥驱动芯片—Pai8131A2022-08-03 2991

-

荣湃半桥驱动芯片具备哪些出色性能表现2022-10-11 10229

-

荣湃隔离放大器Pai8300的五大性能优势2022-12-30 3109

-

荣湃半导体发布全新Pai8265xx系列栅极驱动器2024-03-12 2531

-

30KPA168A单向二极管:高耐压,低损耗,性能卓越2025-03-15 17548

全部0条评论

快来发表一下你的评论吧 !