Verilog定位手段

描述

verilog定位手段:关键信号统计

1、Verilog定位手段-关键信号:高电平计数还是低电平计数?

在IC设计中,进行需要对关键信号的特定状态进行计数,方便debug时进行状态判断。如对流控、反压等信号进行计数。有时候需要进行判断,是高电平计数还是低电平计数。

判断标准是:选择高电平或者低电平计数,要保证能够观察到异常情况

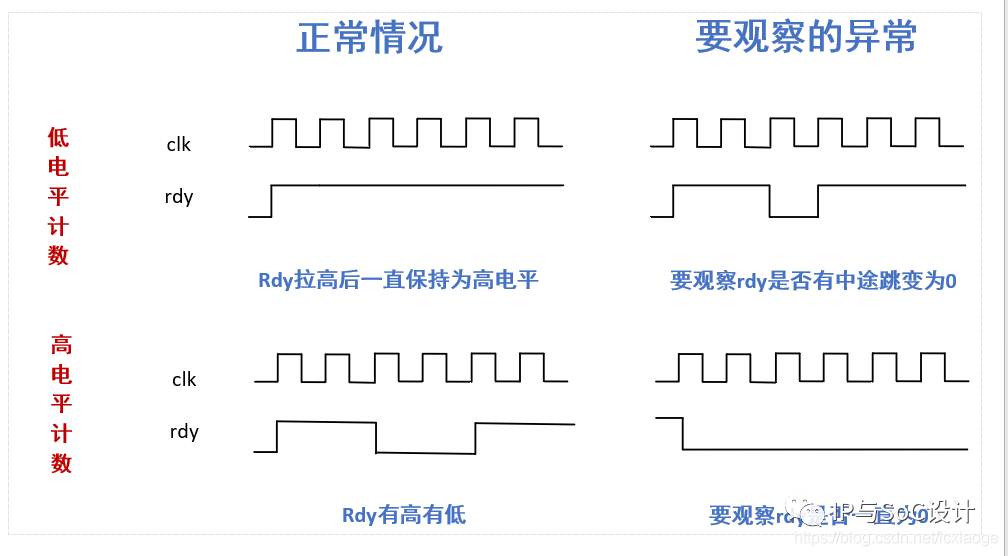

如下图所示:

情况1:正常情况下rdy拉高后一直保持为1,不应该会出现右侧异常,偶尔为0,因此采用低电平计数,如果出现异常,则计数器cnt不为0。如果采用高电平计数,则很难发现右侧异常

情况2:正常情况下rdy有高电平也有低电平,异常情况是一直为低电平,因此采用高电平计数,如果计数器cnt一直保持不变,则说明rdy一直处于低电平的异常状态。

verilog定位手段:速率计算

1、Verilog定位手段:速率统计?

在IC设计中,有些模块的应用有速率的要求,因此在FPGA阶段以及样片测试阶段,需要针对应用场景对速率进行计算,如果在RTL设计阶段能够添加相关的统计寄存器,能够高效准确的计算出传输速率。如MAC,itlkn,DMA,都需要添加相应的统计计算器计算当前状态的速率的相关信息,方便计算速率。

2、如何添加速率统计?

常见方法是:

添加寄存器,记录一段时间内输入数据的个数,如itlkn、MAC

添加寄存器,记录传输一定数据量所需要的时钟周期数量,如DMA

以DMA为例,简单介绍DMA是如何添加速率统计寄存器的:

案例1:CPU主动发起请求:

添加寄存器cycle_num_cnt,统计时钟周期,从CPU发起请求开始、cycle_num_cnt开始每个周期加1,直到DMA模块将数据搬运完成,此时停止计数,此时记录的时机包含,DMA响应请求信号的时间、以及DMA模块搬运数据的时间。

案例解析:

DMA模块时钟为125MHz,每个周期为8ns,CPU发起DMA请求,数据量为1024*128bit,DMA搬运完成后,cycle_num_cnt保持为4812,此时平均传输速率为

1024*128 bit/4812*8ns=3.4Gbps

案例2:DMA主动发起请求

DMA主动发起请求传输数据,可以记录从发出第一个数据到最后一个数据所需要的时钟周期,一次搬运大量的数据,减少测量误差,也能获得准确的速率。

verilog定位手段:link状态统计

1、Verilog定位手段:link状态监控

依据IEEE802.3协议设计的MAC、PCS具有link_up状态信号。PCIE接口具有链路训练成功信号,此处也称之为link_up信号。

针对link状态、可以做如下监控:

1.link_up状态实时可读

2.Link_up有效状态计数统计

3.Link_up从有效跳转到无效状态的次数统计--即link_down次数统计

实时状态可读,可以获得当前状态

有效状态统计,可以知道链路建立成功多次时间了

link_down次数统计,可以知道在实际使用过程中,发生多少次link-down。

审核编辑:汤梓红

-

分享一些优秀的verilog代码 高质量verilog代码的六要素2023-07-18 2119

-

白话科普芯片漏电定位手段2019-02-25 4829

-

基于Verilog的车牌精确定位2019-03-03 5284

-

PLD/FPGA硬件语言设计verilog HDL2011-03-12 2063

-

verilog是什么_verilog的用途和特征是什么2018-05-14 47405

-

Verilog教程之Verilog的命令格式资料说明2019-01-09 1111

-

Verilog语法基础2019-03-08 13952

-

高质量Verilog代码有什么特点2019-03-30 2349

-

浅谈Verilog-95、Verilog-2001与System Verilog之间的区别2021-06-21 12554

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2407

-

IC设计知识点:verilog定位手段之关键信号统计2022-10-31 1672

-

电厂人员定位-安全管控技术手段2023-07-27 1428

-

养老院人员定位管理技术手段、作用及发展趋势2024-09-19 1241

-

Verilog 测试平台设计方法 Verilog FPGA开发指南2024-12-17 1952

-

室内定位精确导航技术支持的技术手段有哪些2024-12-20 1417

全部0条评论

快来发表一下你的评论吧 !