SystemVerilog中的Unpacked Unions

描述

unpacked union中各个成员的大小可以是不同的。

举一个例子

typedef Union {

logic [5:0] a;

logic [3:0] b;

logic c;

} myUnionType

myUnionType myUnion;

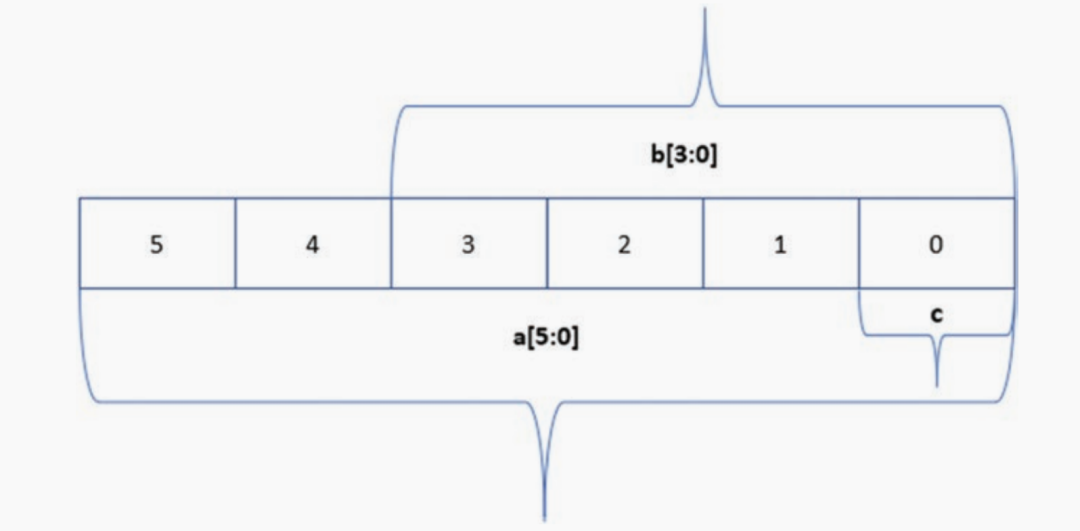

上面的union成员大小都是不同的,这个union整体的大小取决于其中size最大的成员,如下图示例:

logic [5:0] a

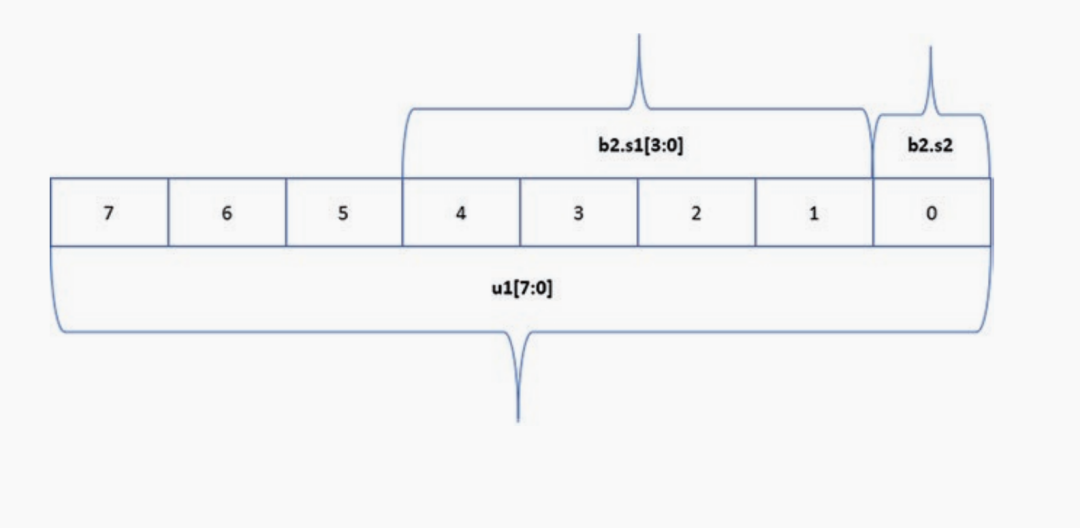

再看一下unpacked union中存在struct成员内存分配的示例:

typedef struct packed {

bit [3:0] s1;

bit s2;

} myStruct;

typedef union {

logic [7:0] u1;

myStruct b2;

} mUnionT;

mUnionT Union1;

对于这个union,最大 size的成员是“logic [7:0]

b1.”所以,这个union整体的大小是

对于一个union,如果你写入成员1,再读取成员2,实际上你读取的就是刚刚写入的成员1,这恰恰也说明了union的本质,即同一个物理存储实体。

module union_example;

logic [31:0] x;

typedef union {

int a;

byte b;

bit [15:0] c;

} data;

data d1;

initial begin

d1.a = 32'h ffff_ffff; //write to d1.a

x = d1.b; //read from d1.b

$display("x = %h",x);

d1.b = 8'h 01; //write to d1.b

x = d1.a; //read from d1.a

$display("x = %h",x);

d1.c = 16'h 1010; //write to d1.c

x = d1.a; //read from d1.a

$display("x = %h",x);

end

endmodule

仿真log:

x = ffffffff x = 00000001 x = 00001010 V C S S i m u l a t i o n R e p o r t

上面的例子声明了一个unpacked union “data.”,然后例化了一个data 类型的数据"d1"

在initial语句块中,我们首先写入union中的成员“int a”:

d1.a = 32'h ffff_ffff; //write to d1.a

注意,此时我们没有向“d1.b”写入任何内容。但既然union只有一个物理存储实体,所以这些成员具有相同的值。所以,当我们从" d1 "读取数据b

x = d1.b; //read from d1.b

仿真log会打印

x = ffffffff

反之亦然,当我们向b写入数据,数据也会反映到a上。

d1.b = 8'h 01; //write to d1.b

此时a会打印:

x = 00000001

成员c的写入同样也会反映到成员a,如打印log所示。

这再次表明union中的所有成员共享一个物理存储空间,对于RTL的可综合性,要求这些成员的大小相同。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SystemVerilog 中各种不同的联合解析2020-11-19 2775

-

SystemVerilog中的Virtual Methods2022-11-28 1185

-

SystemVerilog中的“const”类属性2022-11-29 2585

-

SystemVerilog中的联合(union)介绍2023-10-08 2619

-

SystemVerilog的断言手册2009-07-22 1734

-

SystemVerilog中$cast的应用2022-10-17 4130

-

unpacked数组和packed数组的主要区别2022-10-18 3909

-

SystemVerilog中的操作方法2022-10-31 4498

-

SystemVerilog中可以嵌套的数据结构2022-11-03 2845

-

SystemVerilog中的struct2022-11-07 3452

-

SystemVerilog中的tagged Unions是什么2022-11-10 2139

-

SystemVerilog中的Packed Union2022-11-12 1746

-

SystemVerilog中的Shallow Copy2022-11-21 1571

-

SystemVerilog中的Semaphores2022-12-12 4466

-

Systemverilog中的Driving Strength讲解2023-06-14 2748

全部0条评论

快来发表一下你的评论吧 !