SystemVerilog中的Packed Union

描述

packed union相比unpacked union最大的一个区别就是,在packed union中,所有成员的大小必须相同,这就保证了不管union中存储了哪一个成员,最终这个union的大小是一样的。也正是加了这个限制,所以packed union是可综合的。

类似于packed struct,我们可以对这个union整体进行算法、切分等运算。

typedef union packed {

int a;

bit [31:0] c;

} data;

上面的union声明加入了packed关键字。因为两个成员的大小相同:“int”是32位,“bit [31:0] c”是32位。所以声明为unpacked union是没问题的。

typedef union packed {

logic [9:0] data;

struct packed {

bit p1;

bit [2:0] p2;

bit [1:0] p3;

bit p4;

bit [2:0] p5;

} p_modes;

} myUnion

myUnion Union1;

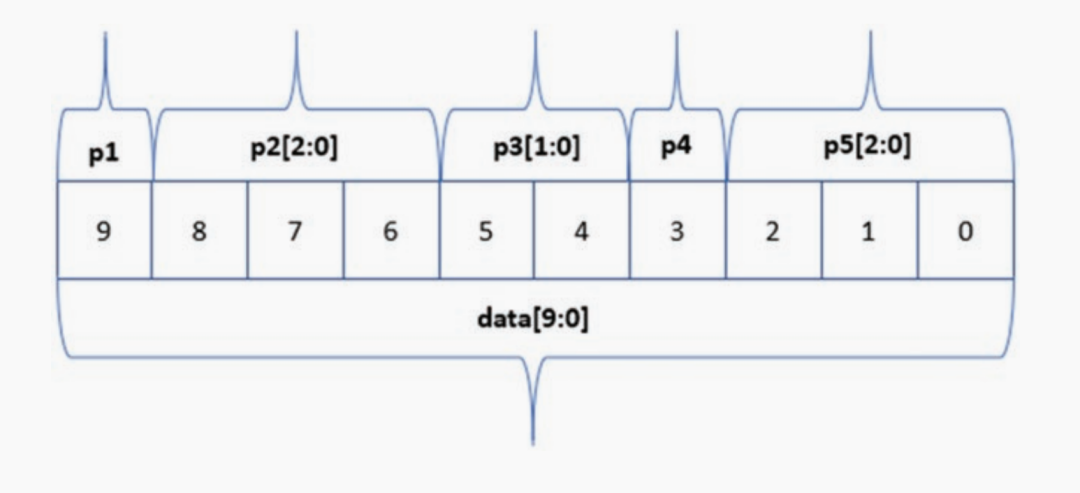

在上面的union中有2个成员,分别都是10比特大小 “struct” “p_modes” 和“data” ,在物理内存中分配如下:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

union和union all有什么区别2023-12-06 2206

-

SystemVerilog中的联合(union)介绍2023-10-08 2618

-

SystemVerilog中的Semaphores2022-12-12 4466

-

SystemVerilog中的Virtual Methods2022-11-28 1184

-

SystemVerilog中的Shallow Copy2022-11-21 1571

-

SystemVerilog中的Unpacked Unions2022-11-11 1232

-

SystemVerilog中的tagged Unions是什么2022-11-10 2139

-

Systemverilog中的union2022-11-09 1554

-

SystemVerilog中的Packed Structure2022-11-07 3385

-

unpacked数组和packed数组的主要区别2022-10-18 3908

-

union 的概念及在嵌入式编程中的应用2022-02-07 532

-

SystemVerilog 中各种不同的联合解析2020-11-19 2775

-

请问UNION与UNION ALL的区别是什么?2020-11-17 12953

全部0条评论

快来发表一下你的评论吧 !