分享几个先进IC封装的案例

描述

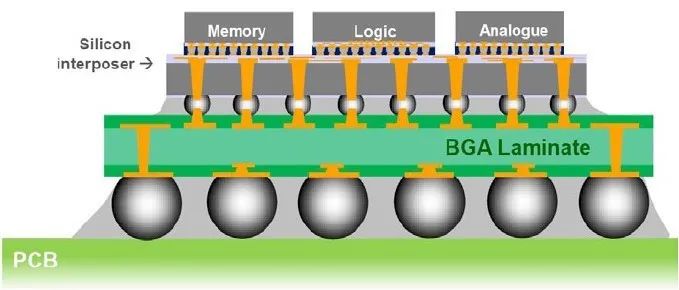

2.5D封装

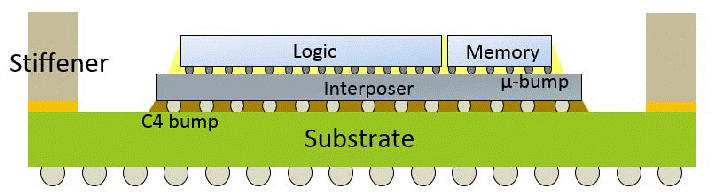

2.5D封装是传统2D IC封装技术的进展,可实现更精细的线路与空间利用。在2.5D封装中,裸晶堆栈或并排放置在具有硅通孔(TSV)的中介层(interposer)顶部。其底座,即中介层,可提供芯片之间的连接性。

2.5D封装通常用于高端ASIC、FPGA、GPU和内存立方体。2008年,赛灵思(Xilinx)将其大型FPGA划分为四个良率更高的较小芯片,并将这些芯片连接到硅中介层。2.5D封装由此诞生,并最终广泛用于高带宽内存(HBM)处理器整合。

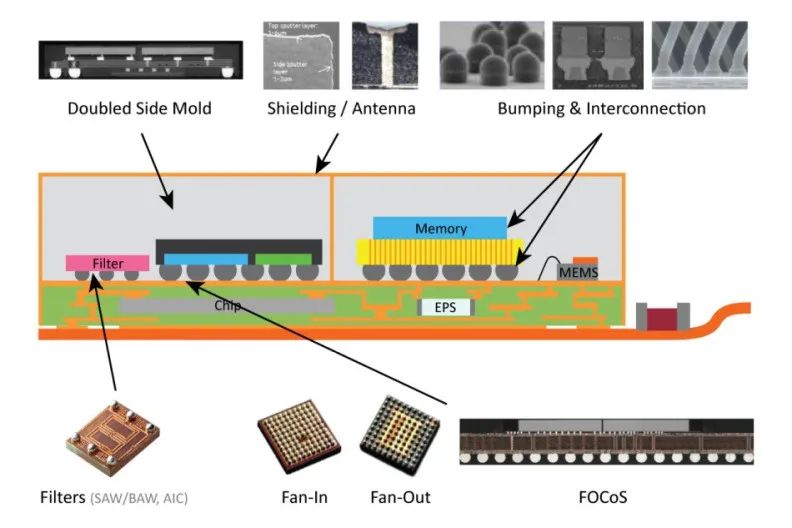

图1、2.5D封装示意图。(图片来源:Research Gate)

3D封装

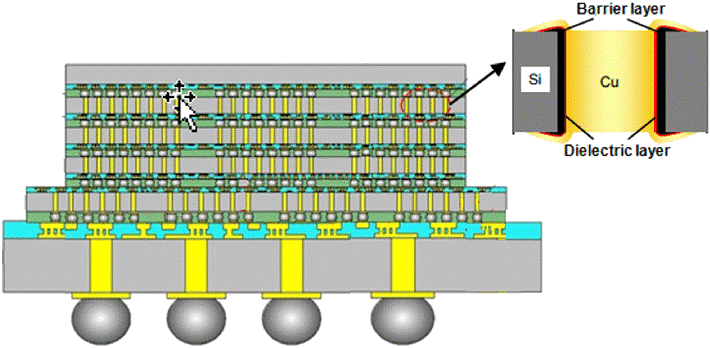

在3D IC封装中,逻辑裸晶堆栈在一起或与储存裸晶堆栈在一起,无需建构大型的系统单芯片(SoC)。裸晶之间透过主动中介层连接,2.5D IC封装是利用导电凸块或TSV将组件堆栈在中介层上,3D IC封装则将多层硅晶圆与采用TSV的组件连接在一起。

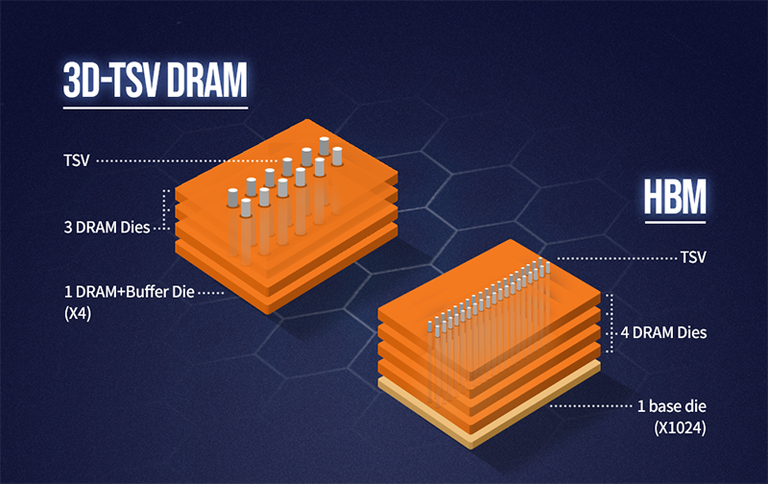

TSV技术是2.5D和3D IC封装中的关键使能技术,半导体产业一直使用HBM技术生产3D IC封装的DRAM芯片。

图2 、从3D封装的截面图可以看出,透过金属铜TSV实现了硅芯片之间的垂直互连。(数据源:Research Gate)

Chiplet

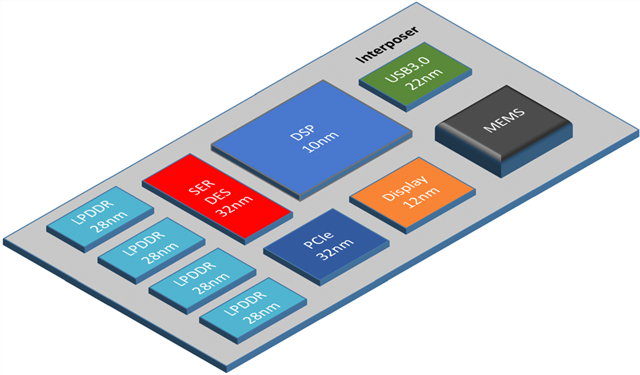

芯片库中有一系列模块化芯片可以采用裸晶到裸晶互连技术整合到封装中。Chiplet是3D IC封装的另一种形式,可以实现CMOS组件与非CMOS组件的异质整合(Heterogeneous integration)。换句话说,它们是较小型的SoC,也叫做chiplet,而不是封装中的大型SoC。

将大型SoC分解为较小的小芯片,与单颗裸晶相比具有更高的良率和更低的成本。Chiplet使设计人员可以充分利用各种IP,而不用考虑采用何种工艺节点,以及采用何种技术制造。他们可以采用多种材料,包括硅、玻璃和层压板来制造芯片。

图3、基于Chiplet的系统是由中介层上的多个Chiplet组成。(图片来源:Cadence) 扇出(Fan out)

在扇出封装中,“连结”(connection)被扇出芯片表面,从而提供更多的外部I/O。它使用环氧树脂成型材料(EMC)完全嵌入裸晶,不需要诸如晶圆凸块、上助焊剂、倒装芯片、清洁、底部喷洒充胶和固化等工艺流程,因此也无需中介层,使异质整合变得更加简单。

扇出技术是比其他封装类型具有更多I/O的小型封装。2016年,苹果(Apple)借助台积电(TSMC)的封装技术,将其16纳米应用处理器与移动DRAM整合到iPhone 7的一个封装中,从而将这项技术推向舞台。

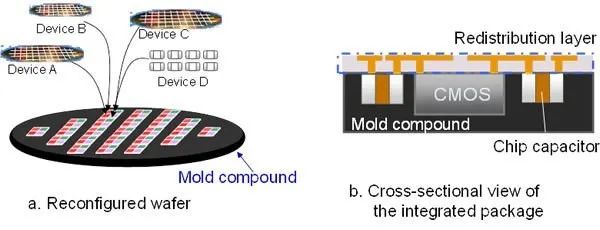

扇出晶圆级封装(FOWLP)

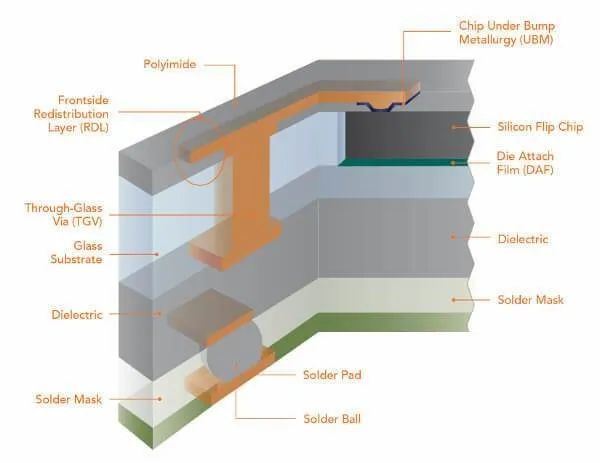

FOWLP技术是针对晶圆级封装(WLP)的改进,可以为硅芯片提供更多外部连接。它将芯片嵌入环氧树脂成型材料中,然后在晶圆表面建构高密度重分布层(RDL)并施加焊锡球,形成重构晶圆(reconstituted wafer)。

它通常先将经过处理的晶圆切成单颗裸晶,然后将裸晶分散放置在载体结构(carrier structure)上,并填充间隙以形成重构晶圆。FOWLP在封装和应用电路板之间提供了大量连接,而且由于基板比裸晶要大,裸晶的间距实际上更宽松。

图4、在此FOWLP封装示例中,硅倒装芯片嵌入到玻璃基板中,重分布层透过芯片扇出至玻璃通孔。(图片来源:Samtec)

异质整合

将分开制造的不同组件整合到更高级别的组件中,可以增强功能并改进工作特性,因此半导体组件制造商能够将采用不同工艺流程的功能组件组合到一个组件中。

异质整合类似于系统级封装(SiP),但它并不是将多颗裸晶整合在单个基板上,而是将多个IP以Chiplet的形式整合在单个基板上。异质整合的基本思想是将多个具有不同功能的组件组合在同一个封装中。

图5、异质整合中的一些技术建构区块。(图片来源:ASE Group)

HBM

HBM是一种标准化的堆栈储存技术,可为堆栈内部,以及内存与逻辑组件之间的数据提供高带宽信道。HBM封装将内存裸晶堆栈起来,并透过TSV将它们连接在一起,从而创建更多的I/O和带宽。

HBM是一种JEDEC标准,它在封装内垂直整合了多层DRAM组件,封装内还有应用处理器、GPU和SoC。HBM主要以2.5D封装的形式实现,用于高端服务器和网络芯片。现在发布的HBM2版本解决了初始HBM版本中的容量和时钟速率限制问题。

图6、HBM封装将内存裸晶彼此堆栈,并利用TSV将它们连接起来以创建更多I/O和带宽。(图片来源:SK Hynix)

中介层

中介层是封装中多芯片裸晶或电路板传递电信号的管道,是插口或接头之间的电接口,可以将信号传播更远,也可以连接到板子上的其他插口。

中介层可以由硅和有机材料制成,充当多颗裸晶和电路板之间的桥梁。硅中介层是一种经过验证的技术,具有较高的细间距I/O密度和TSV形成能力,在2.5D和3D IC芯片封装中扮演着关键角色。

图7、系统分区中介层的典型实现。(数据源:Yole Développement)

重分布层

重分布层包含铜连接线或走线,用于实现封装各个部分之间的电气连接。它是金属或高分子介电材料层,裸晶可以堆栈在封装中,从而缩小大芯片组的I/O间距。重分布层已成为2.5D和3D封装解决方案中不可或缺的一部分,使其上的芯片可以利用中介层相互进行通讯。

图8、使用重分布层的整合封装。(图片来源:Fujitsu)

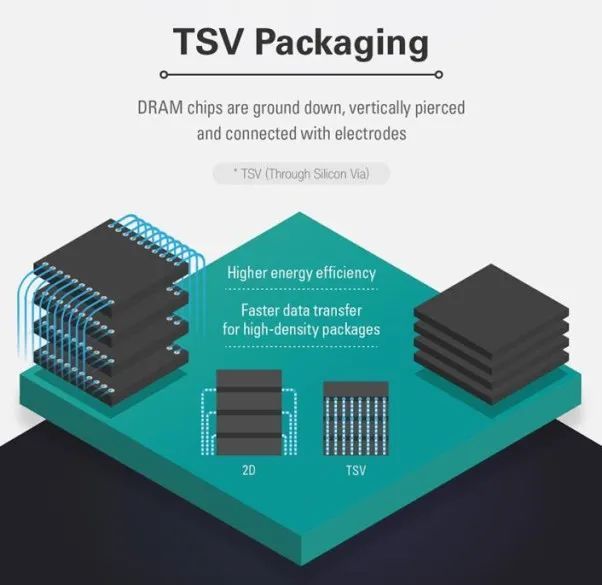

TSV

TSV是2.5D和3D封装解决方案的关键实现技术,是在晶圆中填充铜,提供贯通硅晶圆裸晶的垂直互连。它贯穿整个芯片以提供电气连接,形成从芯片一侧到另一侧的最短路径。

从晶圆的正面将通孔或孔洞蚀刻到一定深度,然后将其绝缘,并沉积导电材料(通常为铜)进行填充。芯片制造完成后,从晶圆的背面将其减薄,以暴露通孔和沉积在晶圆背面的金属,从而完成TSV互连。

图9、在TSV封装中,DRAM芯片接地、穿透并与电极相连。(图片来源:Samsung Electronics)

审核编辑:刘清

-

先进IC封装中最常用10个术语解析2020-11-19 7380

-

浅谈先进封装的四要素2023-12-21 2889

-

IC封装技术:解析中国与世界的差距及未来走向北京中科同志科技股份有限公司 2023-08-10

-

简单介绍IC的高性能封装2010-01-28 4819

-

Mentor推出独特端到端Xpedition高密度先进封装流程2017-06-27 2568

-

10个基本的高级IC封装术语2022-08-12 2946

-

变则通,国内先进封装大跨步走2022-04-08 2119

-

先进封装演进,ic载板的种类有哪些?2023-09-22 5374

-

什么是先进封装?先进封装技术包括哪些技术2023-10-31 4233

-

先进封装基本术语2023-11-24 2184

-

全球先进IC载板市场分析2024-03-18 2116

-

先进IC载板市场的变革与机遇2024-04-17 2002

-

芯片封装IC载板2024-12-14 3157

-

先进封装中RDL工艺介绍2025-01-03 7186

-

IC封装产线分类详解:金属封装、陶瓷封装与先进封装2025-03-26 3096

全部0条评论

快来发表一下你的评论吧 !