芯片厂商从SoC架构转向Chiplet

描述

诞生50几年来,摩尔定律一直是半导体行业的主要推动力。当我们谈论摩尔定律时,所谈的不仅是一项晶体管数量相关的经验法则,更是一本为行业公认的经济账,一种足以驱动各大芯片制造商未来产品战略的方法论。

片上系统(SoC)作为完美践行了这一法则的模范架构,在多年中帮助很多企业在商业上取得了巨大的成功。但在进入10nm制造节点之后,SoC的量产成本逐渐突破了市场所能承受的极限,其市场表现也与当初的预测愈行愈远。当然,摩尔定律也并非一成不变,它需要有更符合未来创新需求的灵活商业模式,以适应更长时间的增长。在这样的趋势中,越来越多的芯片厂商开始从SoC架构转向Chiplet。

SoC:良率之下的成本危机

在半导体行业,良率已经成了与制程同等重要的行业性难题,生产大型SoC之所以难以为继,核心原因就是良率降低引起的硬件成本飙升,全球三大半导体代工厂无不为良率困扰。谁赢得了良率,谁就会赢得未来。简单的说,芯片良率就是晶圆上合格芯片数量与芯片总数的比值,这个数值越大,说明有用芯片数量越多,浪费越少,成本越低,利润越高。芯片尺寸和制程都会直接影响良率。与面积较小的芯片相比,大型单一芯片更容易出现不可逆转的缺陷。以台积电5nm工艺晶圆测试为例,18mm²芯片的平均良率约为80%,而100mm²芯片的良率则会骤降至32%。 先进工艺的发展也会进一步引发良率的挑战。随着工艺节点不断缩小,足以引发芯片严重问题的缺陷尺寸也越来越小。例如,对于45nm制造节点,<9nm的缺陷是可接受的,但对于5nm制造节点,仅仅1nm的缺陷就可能让芯片报废。此外,随着制造工艺提升,光刻技术的制造成本也越来越高,从而增加了成本。

增加芯片尺寸的芯片成本变化,先进工艺节点上的芯片制造的良率问题,已成为全球三大代工厂的竞争焦点。三星基于GAA结构的3nm制程芯片正式进入量产,由于其良率未能达到预期,其晶圆代工业务饱受争议(有消息称,三星3nm工艺良率仅在10%到20%之间)。此外,英特尔原计划于2021年底上市的7nm芯片,也因工艺存在缺陷,导致良率下降,发布时间推迟6个月。无法停步的良率危机表明半导体行业已经达到了一个临界点,而 Chiplet就是下一个阶段的答案。

Chiplet成本方程①

面积减法,良率提升

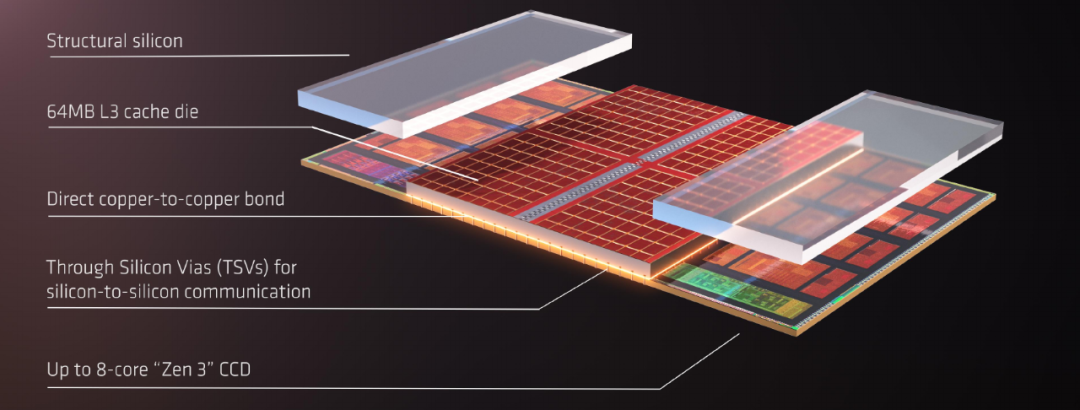

传统的SoC通常将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上。而Chiplet将复杂芯片拆解成一组具有单独功能的小芯片单元die,再通过die-to-die将模块(Top dies)芯片和底层基础(Base die)芯片封装组合在一起,减少整个芯片面积,以提升良率。 通过使用与SoC相同的标准光刻程序,芯片制造商可以用同样的晶圆生产出更多面积更小,良率更高的Chiplet,并进行单独的KGD(Known good die)测试,重新组装并封装到完整的芯片中。对于与SoC情况相同的故障分布,Chiplet上因缺陷导致的废弃约为SoC的4分之1。

AMD EPYC AMD最早在其第一代 EPYC 数据中心处理器重采用了Chiplet方案,“基于AMD内部良率模型和使用成熟工艺的缺陷密度数据,我们估计四个chiplet设计的最终成本仅为单片架构的约0.59。”

Chiplet成本方程②

制程加法,良率提升

除了良率问题,先进制程的费用也是制约芯片成本的一大因素。传统的SoC,所有模块都需要在相同工艺节点下制作。然而,并非所有芯片都适用于先进制程。例如,射频前端作为模拟芯片,其特征尺寸的缩小并不能带来性能的提升,在先进制程下,单位芯片成本不降反升。在Chiplet架构中,不同的模块可以被拆解出来,通过更适合的工艺节点来制造。如在运算核心采用先进制程,射频前端等模块采用成熟制程。设计师还可以将大型SRAM存储器从计算逻辑芯片中拆分出来,优化其制程,能带来更好的整体性能指标提升。由此可以大幅减少芯片对先进制程的依赖,从而降低芯片的量产成本。

不久的将来,芯片制造商将有望从不同代工厂处采购不同工艺、甚至不同材质生产的标准化Chiplet,快速把它们组装成一个SoC级的大芯片,以进行最终验证和测试,就像今天SoC设计师从不同供应商那里采购IP一样。

Chiplet成本方程③

设计难度减法,IP硬核复用

在芯片开发中,制造商不仅要面临与芯片尺寸和工艺节点提升带来的成本挑战,芯片的设计成本也在不断上涨。芯片设计成本通常包含工程师的人力成本、EDA等开发工具、设备、场地、IP等费用。 研发一款传统SoC芯片,需要设计出芯片上的所有模块,不但设计周期漫长,设计费用也居高不下。而Chiplet架构中,芯片在设计层面被分为核心芯粒和非核心芯粒两部分,客户可以直接向第三方公司采购非核心芯粒,从而简化芯片设计难度,提高设计成功率并缩短设计周期。此外,这些成熟的Chiplets,基于KGD(已知良品芯片)设计,可广泛复用于其他芯片中,在保证良率的前提下继续提升单颗芯片性能。

Chiplet成本方程④

上市周期减法

设计周期与上市时间息息相关。在激烈的市场竞争中,仅仅有一个好产品是不够的,企业必须要竭尽所能缩短上市周期,以确保竞争优势。相比传统SoC原型设计之后“一个也不能少”的软硬件协同验证、后端与物理设计、流片制造、封装测试全流程,Chiplet是一个已经走完了设计、制造、测试流程的成品小裸片,仅需要做一次封装就可以使用起来。通过组合现有KGD与可配置硬件,针对应用提供定制化解决方案,Chiplet可以在保障、提升芯片性能的情况下,满足快速TTM需求(Time to market),帮助企业在竞争中赢得优势。

芯片研发已然成了全球最昂贵的赛道,从芯片架构到工艺制程再到设计模式,每一个潜在变量都会引发最终成本的雪崩。Chiplet的出现,给SoC主导多年却日渐式微的半导体行业开辟了一条新的通道。而这条新路的出现绝非偶然,它是行业巨头们耗费多年精力,在芯片功耗、性能、成本、上市周期几者间找到的绝佳平衡,是为了让行业赖以生存的经济规律持续下去积极为之的变化。从SoC走向Chiplet,不是为放弃,是为了让摩尔定律涅槃重生。

审核编辑:郭婷

-

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构2026-01-29 397

-

Chiplet成大芯片设计主流方式,开启IP复用新模式2024-01-12 3632

-

chiplet和soc有什么区别?2023-08-25 4321

-

从设计到制造,Chiplet何以成为高性能芯片设计的首选2023-08-11 2916

-

Chiplet架构的前世今生2023-05-26 3860

-

芯华章浅谈eda、Chiplet等新型技术趋势2023-05-25 646

-

半导体Chiplet技术及与SOC技术的区别2023-05-16 3030

-

从SoC到NoC:芯片架构的演进与变革2023-05-11 15262

-

芯原助力蓝洋智能部署基于Chiplet架构的芯片产品2023-03-30 1769

-

什么是Chiplet?Chiplet与SOC技术的区别2023-03-29 4097

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1480

-

国产封测厂商竞速Chiplet,能否突破芯片技术封锁?2023-01-16 1762

-

从零移植OpenHarmony轻量系统【3】Board、SOC、架构与代码对应关系2022-02-07 3728

-

chiplet是什么意思?chiplet和SoC区别在哪里?一文读懂chiplet2021-01-04 60947

全部0条评论

快来发表一下你的评论吧 !