使用开源verilog仿真工具进行文件的编译和仿真

描述

一、本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。

Icarus VerilogIcarus Verilog极其小巧,支持全平台Windows+Linux+MacOS,并且源代码开源。通过tb文件可以生成对应的仿真波形数据文件。

通过GTKWave可以查看仿真波形图,支持将Verilog转换为VHDL文件。

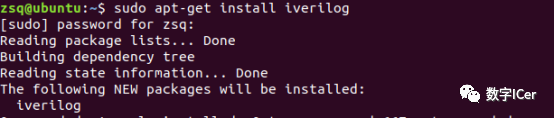

1.安装iverilog:

sudo apt-get install iverilog

安装完成查看版本

iverilog -v

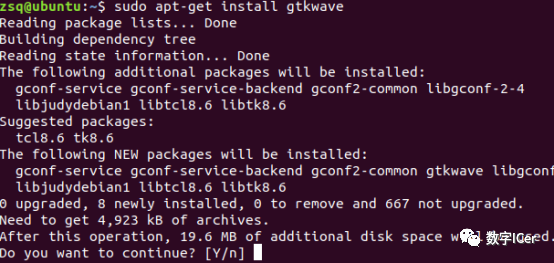

2.安装gtkwave:

sudo apt-get install gtkwave

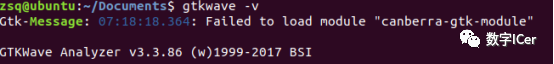

安装完成查看版本

gtkwave -v

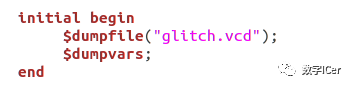

tb中添加:

3.编译:

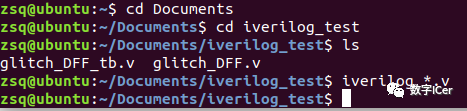

进入文件目录,输入命令:

iverilog *.v

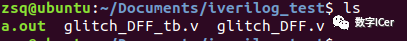

编译完成出现.out文件

生成.vcd文件

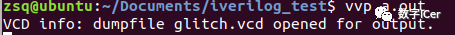

vpp a.out

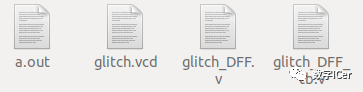

执行后产生的文件如下:

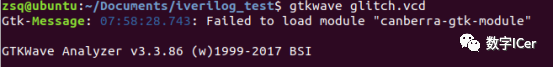

4.用GTKWave打开VCD文件:

gtkwave glitch.vcd

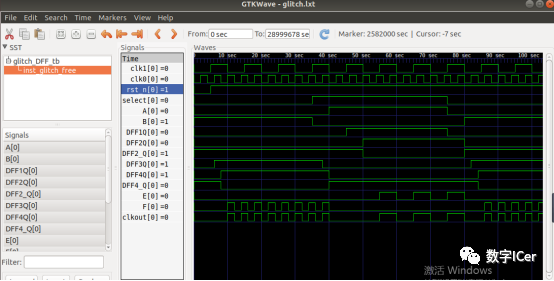

执行完成后,弹出界面

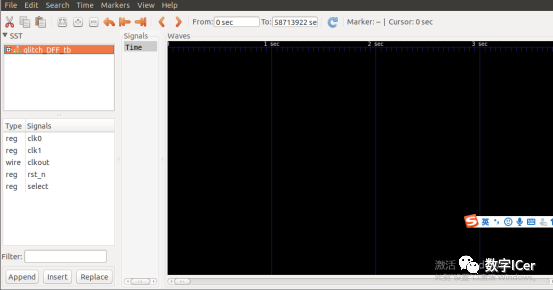

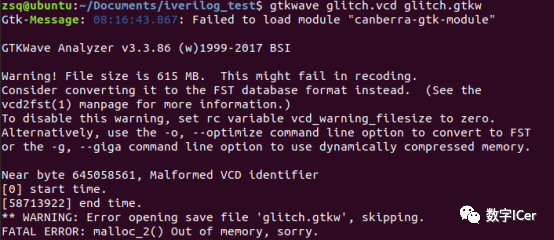

添加波形的时候卡死,可能是glitch.vcd文件太大;

解决:

gtkwave,icarus支持vcd,lxt,lxt2 dump.

vcd通用但vcd dump太大,gtkwave不能很好的查看波形,导致崩溃。

所以最好之前用lxt或将vcd转化为lxt格式。lxt格式是gtkwave的专用格式。

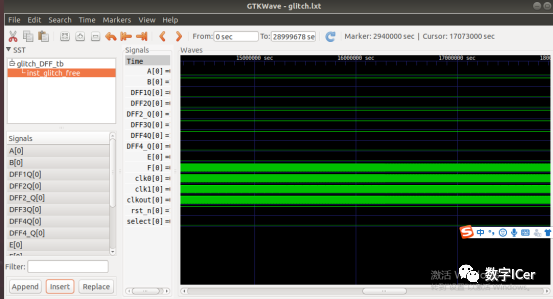

cp glitch.vcd glitch.lxt

添加波形

5.Verilog转换为VHDL

将glitch.v文件转换为VHDL文件glitch.vhd

iverilog -tvhdl -o glitch.vhd glitch.v

审核编辑:郭婷

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

使用NucleiStudio生成tb仿真需要的.verilog文件2025-11-05 243

-

使用 ModelSim 进行设计仿真2011-05-27 1343

-

设计仿真实例的运行文件及C程序2013-03-04 1095

-

基于ModelSim使用modelsim手动时序仿真教程2021-07-23 3346

-

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真2021-07-27 6829

-

VHDL与Verilog硬件描述语言如何用TestBench来进行仿真2021-08-04 5045

-

全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程2022-01-26 989

-

vcs学习笔记(常用选项/仿真流程/代码覆盖率/综合后仿真/图一乐技巧)2022-05-23 16086

-

verilog仿真工具编译2022-08-15 9767

-

利用vcs+verdi仿真工具蜂鸟E200系列处理器仿真分析2022-11-17 4446

-

如何用vcs+verdi仿真Verilog文件2023-05-11 3069

-

Verilog仿真激励举例2023-06-02 2475

-

如何使用 ModelSim 进行设计仿真2024-01-14 480

-

Verilog 电路仿真常见问题 Verilog 在芯片设计中的应用2024-12-17 2004

-

一文详解SystemC仿真库的编译2025-12-12 5083

全部0条评论

快来发表一下你的评论吧 !