基于碳化硅(SiC)的MOSFET可实现更高效率水平

描述

相比基于硅(Si)的MOSFET,基于碳化硅(SiC)的MOSFET器件可实现更高的效率水平,但有时难以轻易决定这项技术是否更好的选择。本文将阐述需要考虑哪些标准因素。

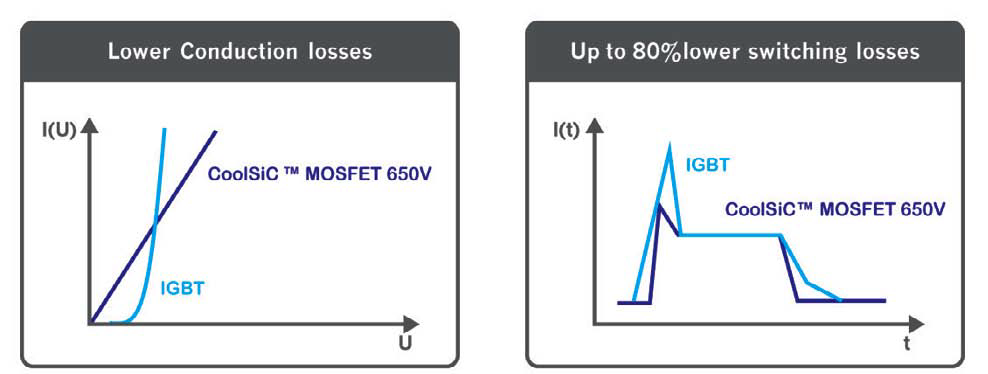

超过 1000 V 电压的应用通常使用IGBT解决方案。但现在的SiC 器件性能卓越,能够实现快速开关的单极组件,可替代双极 IGBT。这些SiC器件可以在较高的电压下实施先前仅仅在较低电压 (<600 V) 下才可行的应用。与双极 IGBT 相比,这些基于 SiC 的 MOSFET 可将功率损耗降低多达 80%。

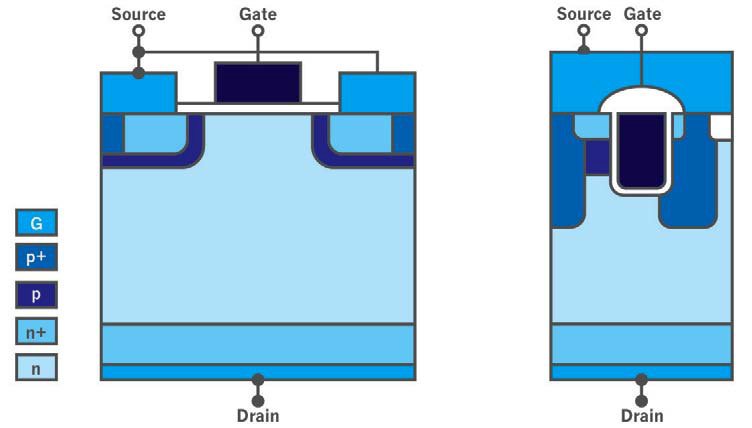

英飞凌进一步优化了 SiC器件的优势特性——通过使用CoolSiC Trench 技术,可以实现具有极高阈值电压 (Vth) 和低米勒电容的 MOSFET器件。相比其他 SiC MOSFET ,它们对于不良的寄生导通效应更具弹性。除了 1200 V 和 1700 V 型号之外,英飞凌还扩展了产品组合,加入了650 V CoolSiC MOSFET,该器件也可用于 230 V 电源应用。这些SiC器件具有更高的系统效率和稳健性,以及更低的系统成本,适用于电信、服务器、电动汽车充电站和电池组等应用。

如果在基于Si的成熟MOSFET技术,和基于 SiC 的较新 MOSFET之间进行选择,需要考虑多种因素。

应用效率和功率密度

与Si器件相比,SiC器件的RDSon在工作温度范围内不易发生波动。使用基于 SiC 的 MOSFET,RDSon 数值在 25°C到100°C温度之间仅仅偏移大约 1.13 倍,而使用典型的基于Si MOSFET(例如英飞凌的 CoolMOSTM C7器件)时,RDSon 则会偏移1.67 倍。这表明针对基于SiC 的 MOSFET器件,工作温度对于功率损耗的影响要小得多,因而可以采用高得多的工作温度。因此,基于 SiC 的 MOSFET 非常适合高温应用,或者可以使用较简单的冷却解决方案来实现相同的效率水平。

图片来源:儒卓力

与 IGBT 相比,基于 SiC 的 MOSFET 具有较低的电导损耗以及可降低多达 80% 的开关损耗。(在使用英飞凌650 V CoolSiC MOSFET的示例中)

驱动器

当从Si转换到SiC时,其中一个问题是选择合适的驱动器。如果基于Si的 MOSFET 驱动器产生的最高栅极导通电压不超过15 V,它们通常可以继续使用。然而,高达 18 V栅极导通电压可以进一步显着降低电阻 RDSon(在 60°C 时可降低多达 18%),因此,值得考虑改用其它驱动器。

另外还建议避免在栅极处出现负电压,因为这会导致 VGS(th)发生偏移,从而使 RDSon 随着工作时间延长而增加。在栅极驱动环路中,源极电感上的电压降导致高 di/dt,这可能引起负VGS(off)电平。很高的 dv/dts 带来了更大的挑战,这是由于半桥配置中第二个开关的栅极漏极电容引起的。可以通过降低 dv/dt 来避免这个问题,但代价是效率的下降。

限制负栅极电压的最佳方法是通过开尔文源极概念使用单独的电源和驱动器电路,并集成二极管钳位。位于开关的栅极和源极之间的二极管钳位限制栅极出现负电压。

反向恢复电荷 Qrr

特别针对使用导通体二极管进行连续硬换向的谐振拓扑或设计,还必须考虑反向恢复电荷 Qrr。当二极管不再导电时,这是必须从集成的体二极管中去除的电荷(存在于所有二极管中)。各组件制造商都做出了巨大的努力,以便尽可能地降低这种电荷。英飞凌的“Fast Diode CoolMOS”系列就是这些努力成果的示例。它们具有更快速的体二极管,与前代产品相比,可以将 Qrr 降低 10 倍。英飞凌的 CoolSiC 系列在这方面取得了进步,与最新的 CoolMOS 组件相比,这些SiC MOSFET 实现了10 倍的性能改进。

Trench 技术极大程度地减少了使用中的功率损耗,并提供了极高的运行可靠性。

采用CoolSiC技术,用户可以开发具有更少组件和磁性元件及散热器的系统,从而简化系统设计,并减低体积和成本。借助Trench 技术,这些组件还保证达到极低的使用损耗和极高的运行可靠性。

功率因数校正 (PFC)

目前行业的重点是提高系统效率。为了实现至少 98% 的效率数值,业界针对功率因数校正 (PFC)付出了很多努力。具备优化 Qrr 的 基于SiC MOSFET 有助于实现这一目标。它们可以实现用于PFC的硬开关半桥/全桥拓扑。针对CoolMOS 技术,英飞凌先前推荐“三角电流模式(Triangular Current Mode)”方法,但使用 SiC 器件可以实现具有连续导通模式的图腾柱 PFC。

输出电容 COSS

在硬开关拓扑中必须消耗存储的能量 EOSS;对于最新的 CoolMOS型款,这种能量通常较大。然而,与图腾柱 PFC 的导通损耗相比,它仍然相对较低,因此可以忽略不计,至少初期如此。较低的电容意味着可以从更快的开关速度中受益,但这也可能引起导通期间的漏极源极电压过冲 (VDS)。

针对基于Si的 MOSFET,可以通过使用外部栅极电阻加以补偿,以降低开关速率,并且在漏源处实现所需的 80% 电压降额。这种解决方案的缺点是增加电流会导致更多开关损耗,尤其是在关断期间。

在50 V漏源电压下,基于 SiC 的 MOSFET 的输出电容要大于可比较的基于 Si 的功率半导体器件,但 COSS/VDS 的关系更加线性。其结果是,相比基于 Si 的MOSFET型款,基于 SiC 的 MOSFET 允许在相同的电路中使用较低的外部电阻,而不会超出最大漏源电压。这在某些电路拓扑中是有利的,例如在 LLC 谐振 DC/DC 转换器中,可以省去额外的栅极电阻器。

结论

尽管SiC技术拥有诸多优势,但基于Si的 MOSFET不一定会过时。部分原因是由于体二极管的阈值电压要高得多,直接使用基于 SiC 的型款来替换基于 Si 的 MOSFET,将会导致体二极管的功率损耗增加四倍,基本上抵消了效率增益。如要真正受益于基于 SiC 的 MOSFET 的更高效率,必须在 MOSFET 通道上使用 PFC 的升压功能,而不是在体二极管上反向使用。还必须优化死区时间性能,以充分利用基于 SiC 的 MOSFET 的优势。

-

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?2025-01-04 2587

-

在开关电源转换器中充分利用碳化硅器件的性能优势2023-03-14 2874

-

碳化硅SiC技术导入应用的最大痛点2023-02-27 1870

-

碳化硅MOSFET是如何制造的?如何驱动碳化硅场效应管?2023-02-24 12563

-

碳化硅如何改进开关电源转换器设计?2023-02-23 11097

-

创能动力推出碳化硅二极管ACD06PS065G2023-02-22 2614

-

降低碳化硅牵引逆变器的功率损耗和散热2022-11-02 9634

-

传统的硅组件、碳化硅(Sic)和氮化镓(GaN)2021-09-23 6157

-

什么是碳化硅(SiC)?它有哪些用途?2021-06-18 9392

-

碳化硅基板——三代半导体的领军者2021-01-12 4420

-

1200V碳化硅MOSFET系列选型2020-09-24 2011

-

浅析SiC-MOSFET2019-09-17 6421

-

如何用碳化硅(SiC)MOSFET设计一个高性能门极驱动电路2018-08-27 11826

-

基于碳化硅MOSFET的20KW高效LLC谐振隔离DC/DC变换器方案研究2016-08-05 8998

全部0条评论

快来发表一下你的评论吧 !