超大尺寸芯片封装内应力仿真模型与改善方案

电子说

描述

作者:侯耀伟,王喆,乔志壮,杜勿默,周扬帆

为改善超大尺寸芯片封装的内应力,研究了使用导电胶粘接的超大尺寸芯片的陶瓷封装结构,建立了简化的结构模型。模型从上到下依次为硅芯片、导电胶和陶瓷基板三层结构。利用有限元分析方法,研究了导电胶的粘接层厚度、弹性模量、热膨胀系数和固化温度对芯片封装内应力的影响。

结果表明,粘接层所受的应力主要集中在导电胶和芯片粘接界面边缘处,且粘接层四个角所受的应力最大,故在贴片工艺中要保证导电胶在芯片四个角的溢出,防止芯片脱落。适当增加导电胶的粘接层厚度,选取低弹性模量和低热膨胀系数的导电胶,以及采较低的固化温度可大幅度降低器件的内应力,提高芯片剪切力。

引言

随着微电子技术的不断创新和发展,大规模集成电路的集成度和工艺水平不断提高,系统级芯片的设计能力和技术也得到了很大的提高。系统级芯片可将微处理器、模拟IP核、数字IP核和存储器集成在一起,大幅提高器件的集成度,但芯片也面临晶粒尺寸过大的挑战,尤其当芯片使用超低k电介质材料时,晶粒变得更脆、更易碎。

由于陶瓷基板、芯片和导电胶之间的线性热膨胀系数的差异,超大尺寸芯片粘接面存在的大应力会使器件在后续使用中存在重大的质量隐患。粘接面应力过大,易使粘接面边缘出现开裂,严重时会使芯片脱落;应力过大会损伤芯片,影响器件电性能。

近年来我国在芯片封装内应力方面进行了深入的研究。连兴峰等人运用COMSOL Multiphysics软件分析了由封装引起的热失配对1mm x 1mm芯片的封装内应力的影响,发现芯片所受应力会随着基板厚度的增加而增加。李明等人利用数字散斑相关方法对COB封装在热载荷下的表面热变形分布进行实验测量,并比较了不同封装结构对内应力的影响,认为陶瓷基板上的封装方案比FR4上的封装方案的热失配小,封装内应力也较小,适用于应力敏感的封装系统。

梁颖等人对微光机电系统芯片粘接层进行了温度循环应力与应变有限元分析,发现无溢出结构的粘接层内的应力与应变大于有溢出结构的粘接层内的,有溢出结构的粘接层在温度循环条件下可以在一定程度上降低粘接层内的最大应力与应变。张淑芳等人对LED小芯片封装中所受内应力与应变进行了模拟仿真与分析,发现芯片封装的内应力集中在导电胶和芯片粘接界面边缘处。

目前国内针对芯片封装内应力方面的研究主要集中在小尺寸芯片上,而对超大尺寸芯片封装,其封装内应力与导电胶的性能参数、粘接层厚度和固化温度的关系研究较少。本文利用有限元分析方法,采用简化的结构模型,分析了这些变量对芯片内应力的影响,从而为超大尺寸芯片的封装设计提供参考依据。

1 超大尺寸芯片封装内应力仿真模型

将使用导电胶粘接的超大尺寸芯片的陶瓷封装结构作为研究对象,封装模型从上到下依次为硅芯片、导电胶粘结层和陶瓷基板三层结构,简化后模型的有限元网格划分如图1所示,模型尺寸参数和模型中材料的性能参数分别如表1和表2所示。为提高计算效率,对分析模型进行简化处理:①芯片与陶瓷基板之间的粘接层无空洞等缺陷;②模型温度发生变化时,模型整体温度分布均匀;③不考虑导电胶溢出情况,导电胶尺寸与芯片尺寸一致。

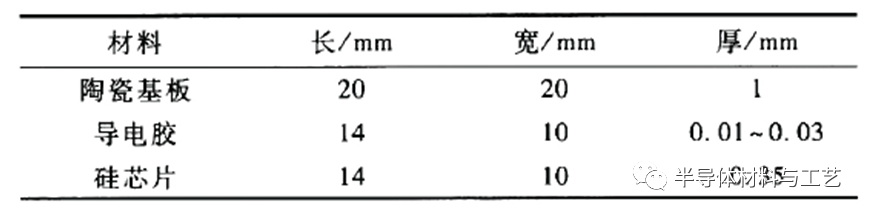

表1 模型尺寸参数

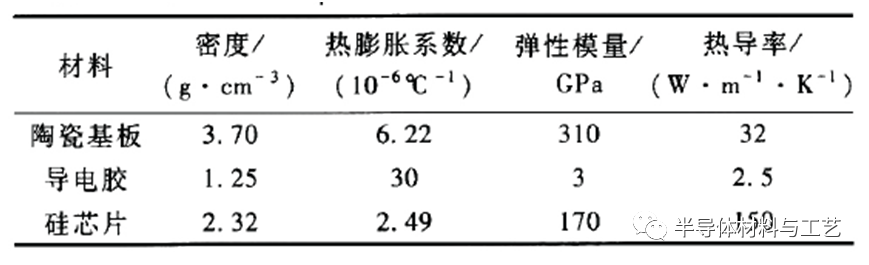

表2 模型中材料性能参数

2 仿真分析及验证

由于不同导电胶的性能参数差异较大,其应用环境也不一样。本文分析了导电胶的粘接层厚度、弹性模量、热膨胀系数和固化温度对超大尺寸芯片粘接内应力的影响并进行了试验验证。

2.1 粘接层厚度对芯片封装内应力的影响

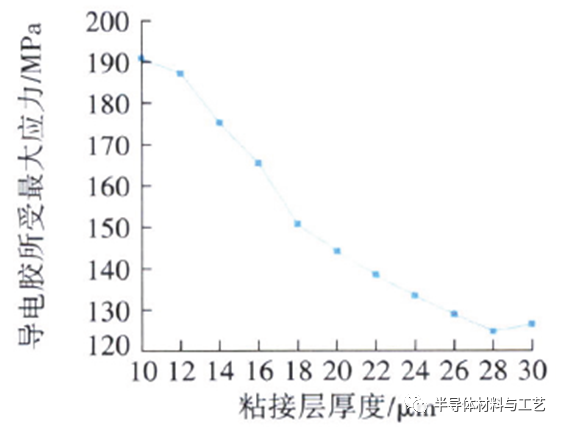

为研究超大尺寸芯片的粘接内应力与粘接层厚度的关系,模型中设定导电胶的热膨胀系数为3x10-5/oC,弹性模量为3 GPa,固化温度为175oC,粘接层厚度为10~30 um。图2为导电胶所受的最大应力随粘接层厚度的变化关系,从图中可以看出随着粘接层厚度增大,导电胶所受的最大应力呈减小趋势;当粘接层厚度较小时,导电胶所受的最大应力随粘接层厚度的增加迅速减小。

图2 粘接层厚度与导电胶所受最大应力的关系

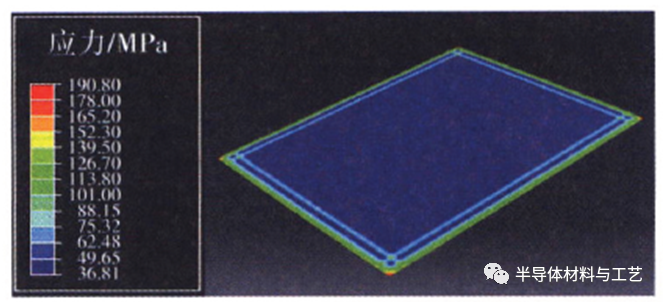

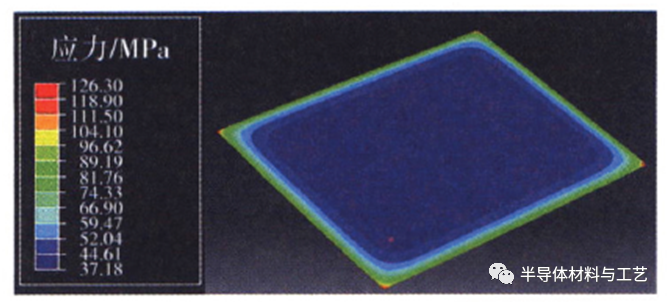

图3为不同粘接层厚度(10 um和30 um)粘接层所受应力情况,从图中可以看出,粘接层所受应力集中在导电胶和芯片粘接界面边缘处,且粘接层四个角所受的应力最大。

(a)粘接层厚度为10 um

(b)粘接层厚度为3 0 um图3 不同厚度粘接层所受应力

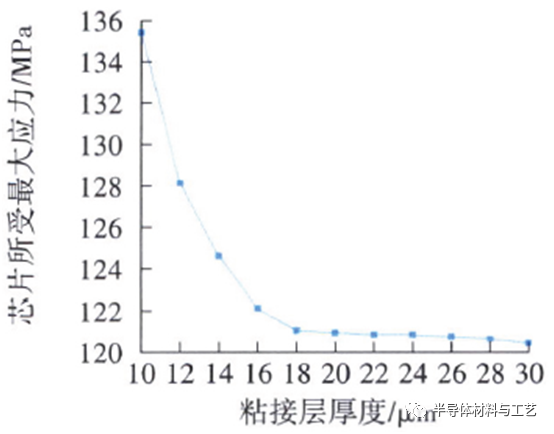

图4为芯片所受最大应力与粘接层厚度的关系,从图中可以看出随着粘接层厚度增大,芯片所受的最大应力快速减小,当粘接层厚度达到18 um后,芯片所受的最大应力基本保持不变。因此,在超大尺寸芯片的贴片工艺中可适当增加粘接层厚度来降低器件的内应力,同时要保证芯片四个角有胶溢出,防止芯片因受应力而发生脱落。

图4 粘接层厚度与芯片所受最大应力的关系

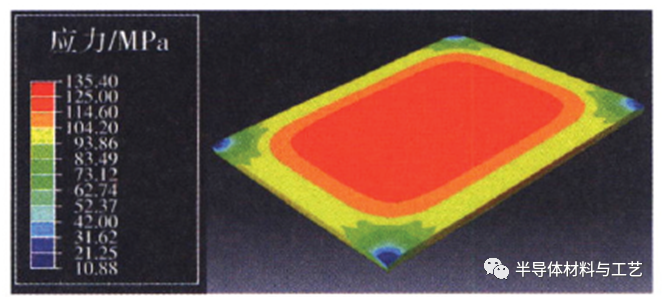

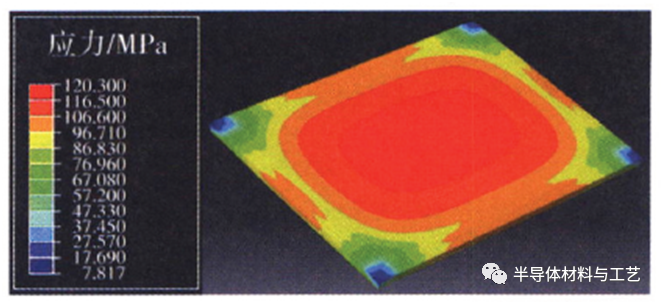

图5为不同粘结层厚度(10 um和30 um)芯片所受应力情况,从图中可以看出,芯片所受应力主要分布在芯片中心区域,芯片中心易受应力过大而产生裂纹。粘结层厚度太厚会导致其热阻增大,阻碍热的传导。综合考虑器件散热和内应力影响,后续在分析导电胶的弹性模量、热膨胀系数及固化温度对超大尺寸芯片内应力的影响时,将导电胶的厚度设定为20 um。

(a)粘接层厚度为10 um

(b)粘接层厚度为3 0 um图5 不同粘接层厚度芯片所受应力

2.2 弹性模量对芯片封装内应力的影响

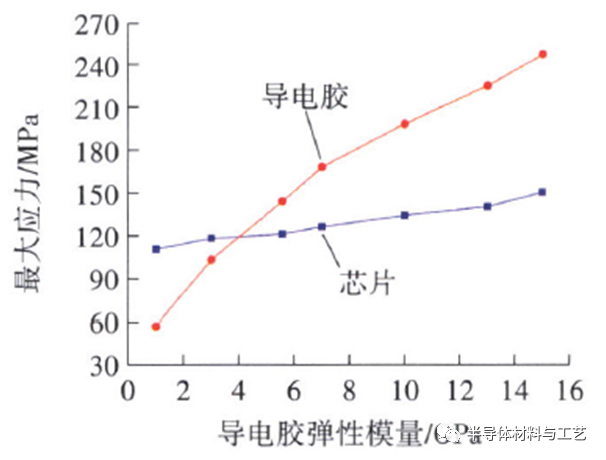

超大尺寸芯片粘结所使用的导电胶一般为环氧树脂导电胶,其在高温固化过程中会使基体树脂在空间中形成三维网状交错结构,为芯片提供良好的支撑和保护,环氧树脂导电胶弹性模量变化范围比较宽,从几GPa到十几GPa。为表征该参数对大尺寸芯片封装内应力的影响,假设导电胶的热膨胀系数为3x10-5/oC,固化温度为175 oC,粘接层厚度为20 um,弹性模量从1~15 GPa递增。图6为弹性模量与导电胶和芯片所受最大应力的关系。

图6 弹性模量与导电胶和芯片所受最大应力的关系

从图6可以看出,随着导电胶弹性模量的增加,导电胶所受最大应力快速增大,芯片所受最大应力缓慢增大。故在超大尺寸芯片的贴片工艺中要选取低弹性模量的导电胶,以防芯片在温度变化时所受应力过大而发生破裂,影响器件的电性能。

2.3 热膨胀系数对芯片封装内应力的影响

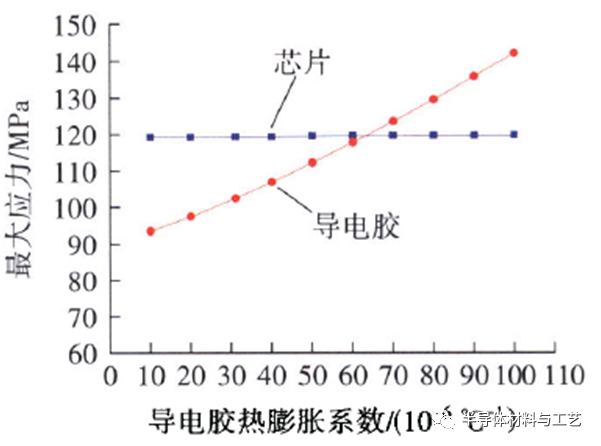

假设导电胶的弹性模量为3 GPa,固化温度为175 oC,粘接层厚度为20 um,导电胶的热膨胀系数为1x10-5/oC~1x10-4/oC,研究热膨胀系数对大尺寸片上系统(SoC)芯片粘接内应力影响。图7为导电胶热膨胀系数与导电胶和芯片所受最大应力的关系。从图7可以看出,随着导电胶热膨胀系数的增加,导电胶所受最大应力逐渐增大,芯片所受最大应力基本保持不变。故在超大尺寸芯片的贴片工艺中,要选取低热膨胀系数的导电胶,以降低器件所受内应力。

图7 热膨胀系数与导电胶和芯片所受最大应力的关系

2.4 固化温度对芯片封装内应力的影响

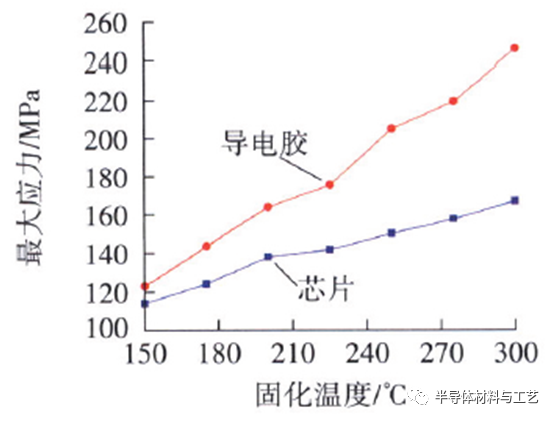

导电胶的产品手册中会给出几种不同的固化温度,为表征该参数对大尺寸芯片粘接内应力影响,假设导电胶的弹性模量为3 GPa,导电胶的热膨胀系数为3x10-5/oC,粘接层厚度为20 um,固化温度为150~300oC。图8为固化温度与导电胶和芯片所受最大应力的关系。从图8可以看出,选取较高的固化温度时,导电胶和芯片所受最大应力比较大。故在超大尺寸芯片的贴片工艺中要选取较低的固化温度,以降低器件所受内应力。

图8 固化温度与导电胶和芯片所受最大应力的关系

2.5 试验验证

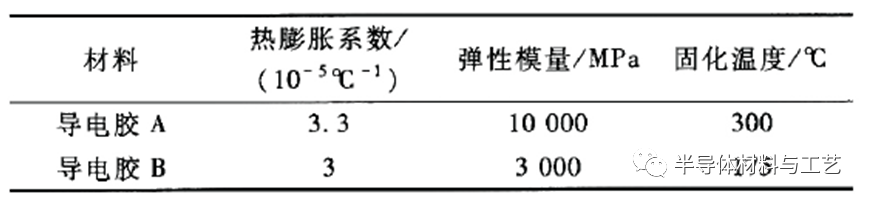

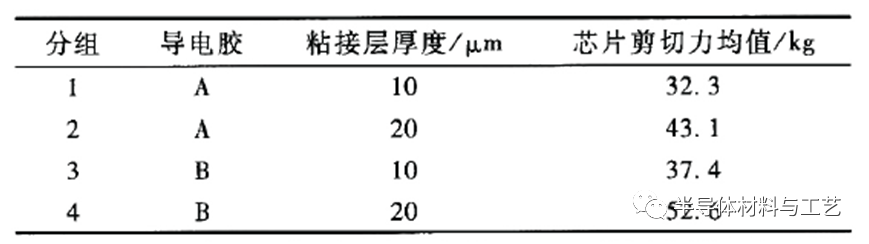

使用导电胶A和导电胶B进行试验,验证仿真结果。导电胶的性能参数如表3所示。分别用导电胶A和B将14mm x 10mm x 0.35mm芯片粘接在陶瓷基板上。试验分四组进行,如表4所示,每个试验组包含20只样品。

表3 导电胶性能参数

表4 试验分组及各分组的芯片剪切力均值

导电胶固化完成后将4组样品按照GJB548B-2005方法1010的要求进行100次温度循环试验,试验条件为-65~150 oC,高低温总转换时间不得超过1 min,停留时间不得少于10 min。试验后对样品进行芯片剪切力试验,芯片剪切力的大小反映了芯片粘接内应力对粘结力的影响,试验接果如表4所示。

经过温度循环试验后,分组1、分组2和分组3的部分样品的粘接面边缘均出现缝隙,且芯片剪切力也较低;分组4样品经过试验后粘接面边缘未出现缝隙,且芯片剪切力也较前3组的大,因此,增加粘接层厚度,采用较低弹性模量的导电胶和较低的固化温度可有效降低产品的内应力。

3 结论

本文利用有限元分析方法,采用简化的结接构模型,研究了导电胶的粘接层厚度、弹性模量、热膨胀系数及固化温度对超大尺寸芯片粘接内应力的影响,主要结论如下。

①超大尺寸芯片的粘接内应力与导电胶粘接厚度关系密切。当粘接层厚度增大时,导电胶所受的最大应力呈减小趋势;随着粘接层厚度增大,芯片所受的最大应力快速减小,当粘接层达到一定厚度后,芯片所受应力基本保持不变。

②在超大尺寸芯片的贴片工艺中可适当增加粘接层厚度来降低器件的内应力;粘接层四个角所受应力最大,故在贴片时要保证胶在芯片四个角的溢出,防止芯片发生脱落。

③当导电胶的弹性模量增加时,导电胶和芯片所受最大应力逐渐增大,在超大尺寸芯片的贴片工艺中要选取低弹性模量的导电胶。

④当导电胶的热膨胀系数增大时,导电胶所受最大应力逐渐增大,芯片所受应力基本保持不变。在超大尺寸芯片的贴片工艺中要选取低热膨胀系数的导电胶。

⑤选取较高的固化温度时,导电胶和芯片所受应力比较大。故在超大尺寸芯片的贴片工艺中要选取较低的固化温度,以降低器件所受内应力。审核编辑:郭婷

-

玻璃容器内应力测试仪 符合《中国药典》 4003 标准2024-10-31 1225

-

利用有限元分析方法的超大尺寸芯片的改善封装设计2022-12-12 2821

-

内应力是如何形成的?影响是什么?2022-12-07 5096

-

奶瓶瓶罐内应力测试仪的详细介绍2021-07-30 1658

-

焊接应力的不利影响_消除焊接应力的有效方法2020-02-04 4130

-

陶瓷封装和塑料封装哪个更好?优缺点对比更明显~2019-12-11 19420

-

关于去除电子产品中塑料材质的内应力的方法2015-07-28 4089

-

芯片为什么会分层2011-07-31 12242

-

芯片分层原因2011-07-26 13351

-

TO-251/2封装造成芯片分层2011-07-24 3722

-

磁记忆检测在无缝钢轨内应力测试中的可行性研究2010-03-20 867

-

铍及不锈钢环形焊件残余应力测试2010-01-26 577

全部0条评论

快来发表一下你的评论吧 !