学会这些System Verilog方法,芯片验证入门没问题

电子说

描述

1. 验证的主流语言为什么是System Verilog语言?

一个掌握Verilog语言的工程师初次看SystemVerilog都会有这样的感受,这就是Verilog啊,很容易啊,So easy啊。没错,确实是这样,System Verilog的产生就是因为芯片设计规模不断增长,功能日趋复杂,单纯的用Verilog和VHDL等硬件语言已经无法满足验证的需求,结合C,C++等软件语言,又显得难度太大,不容易掌握,因此产生了SystemVerilog,当然也产生了其他验证语言,比如Vera和e语言,但因为SystemVerilog结合了来自 Verilog、VHDL、C++的概念,还有验证平台语言(OpenVera和e语言)和断言语言(OVA和PSL),使得SystemVerilog在验证界坐稳了第一的宝座。它将硬件描述语言(HDL)与现代的高层级验证语言(HVL)结合了起来。使其对于进行当今高度复杂的设计验证的验证工程师具有相当大的吸引力。这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。随着不断地发展,System Verilog拥有芯片设计及验证工程师所需的全部结构,它集成了面向对象编程、动态线程和线程间通信等特性,作为一种工业标准语言,SV全面综合了RTL设计、测试平台、断言和覆盖率,为系统级的设计及验证提供强大的支持作用。另一方面,验证方法学(VMM、OVM、AVM和UVM等)的推动也功不可没,System Verilog能够和芯片验证方法学结合在一起,即作为实现方法学的一种语言工具。使用验证方法学可以大大增强模块复用性、提高芯片开发效率,缩短开发周期。

2. 出镜率较高的数据类型

逻辑(logic)类型。

四状态类型:interger,reg,logic,time,wire,tri

双状态数据类型(更好的性能,更低的内存消耗)。

二状态类型:bit,int,byte,shortint,longint

队列,动态和关联数组(自带搜索和分类功能)

队列和数组的操作,常常用在reference model建模或者checker的数据比对过程中。队列的操作包括常用函数:insert,delete,push_back, pop_back, push_front, push_back等;数组的操作(min最小值,max最大值,unique排除重复,find索引相关,sum求和,sort升序,rsort降序,reverse倒序,shuffle乱序等。

关联数组(对于非常大的寻址空间存储建模,我们只需要访问边界值,以及中间个别一些空间进行验证,关联数组提供保存稀疏矩阵的元素)。

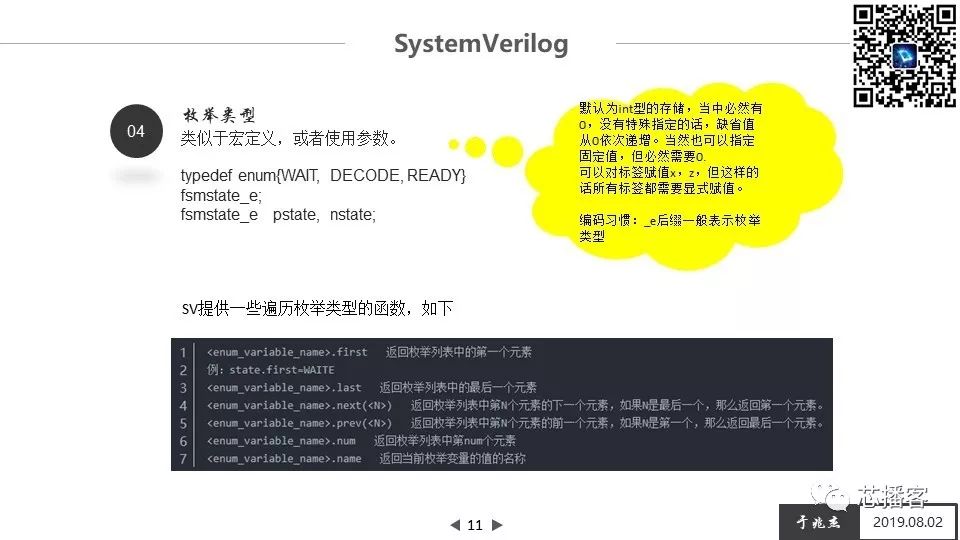

枚举类型

类似于宏定义,或者使用参数。

typedef enum{WAIT, DECODE, READY}fsmstate_e;

fsmstate_e pstate, nstate;

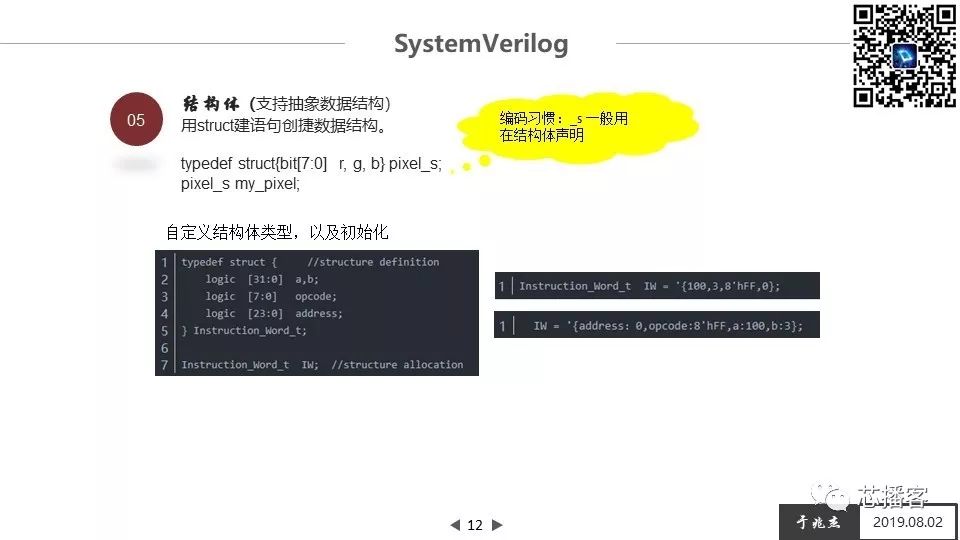

结构体(支持抽象数据结构)用struct建语句创建数据结构。

typedef struct{bit[7:0] r, g, b} pixel_s;

pixel_s my_pixel;

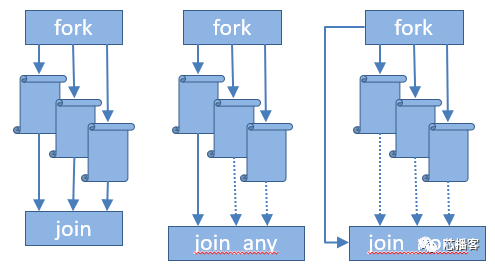

fork...join块可以指定一条或多条语句,每一条语句都应该作为并发进程执行。

| 选项 | 描述 |

| join | 父进程会阻塞直到这个分支产生的所有进程结束。 |

| join_any | 父进程会阻塞直到这个分支产生的任意一个进程结束。 |

| join_none | 父进程会继续与这个分支产生的所有进程并发执行。在父线程执行一条阻塞语句之前,产生的进程不会启动执行。 |

Function和Task

function执行不消耗时间,带时间的操作如#100ns,@,wait等都不能出现在function。所以一般而言,function是不能调用task的,但是在fork……join_none中例外。函数可以有返回值。

消耗时间的操作用task,比如driver里面对信号的驱动过程,一般来讲是在task中完成,但是具体的算法是由function完成的,所以,task中调用function。task没有返回值。

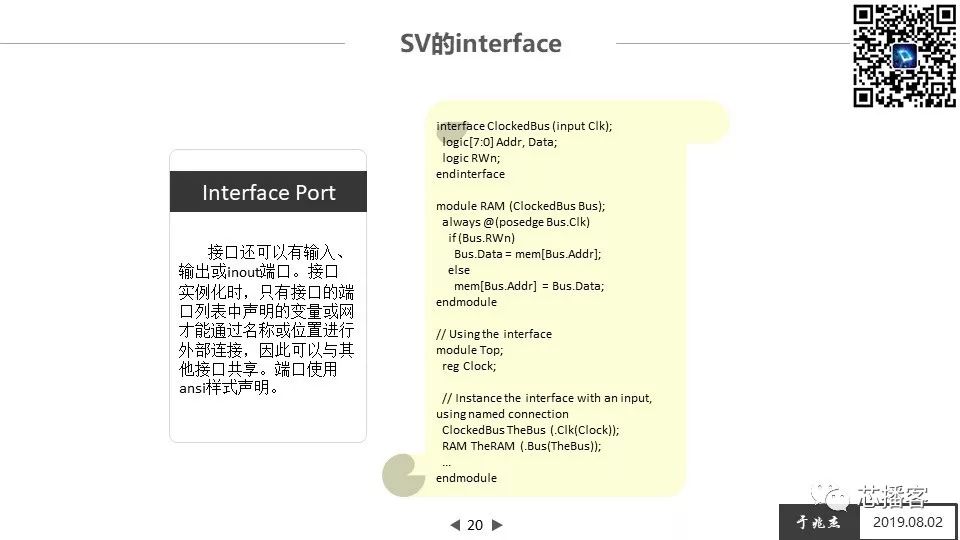

3. System Verilog的Interface

这是一个比较新的概念,Interface封装了连接性:接口可以作为单个项目通过端口传递,从而用单个名称替换一组名称。这减少了建模端口连接所需的代码量,并提高了端口连接的可维护性和可读性。封装功能,与通过接口连接的模块隔离。因此,通信协议的抽象级别和粒度可以完全独立于模块进行细化。

可以包含参数、常量、变量、函数和任务、流程和连续分配,这对于系统级建模和测试应用程序都很有用。

可以帮助构建功能覆盖记录和报告、协议检查和断言等应用程序。

可以用于无端口访问:接口可以作为模块中的静态数据对象直接实例化。因此,可以从设计中的不同点调用用于访问接口内部状态信息的方法来共享信息。

灵活性:接口可以像模块一样参数化。此外,可以使用未指定的接口实例化(称为泛型接口)创建模块头。这个接口可以在稍后实例化模块时指定。

4. System Verilog的面向对象(OOP)

面向对象使用户能够创建复杂的数据类型,并且将它们跟使用这些数据类型的程序紧密的结合在一起。用户可以在更加抽象的平台上建立测试模型,通过调用函数改变信号,而不是直接改变电平信号。

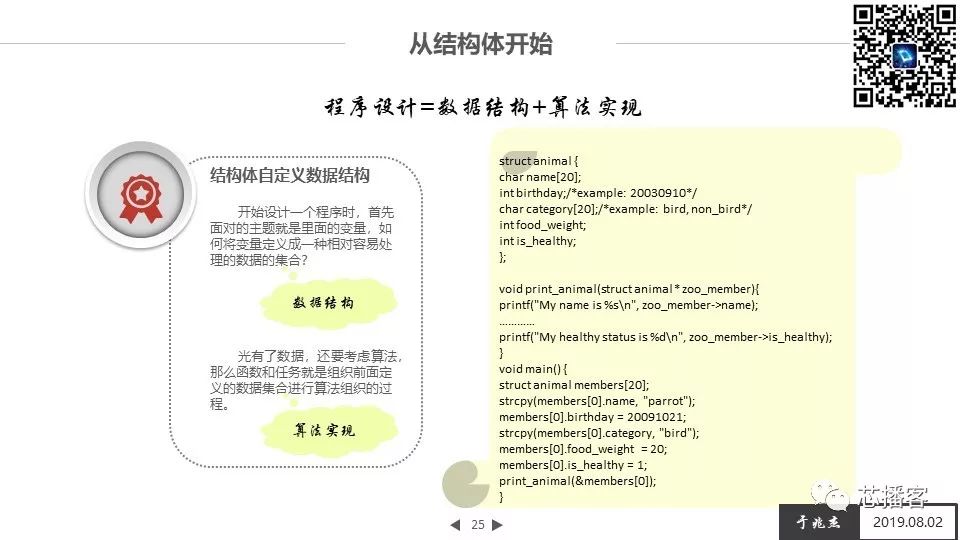

从结构体开始:程序设计=数据结构+算法实现

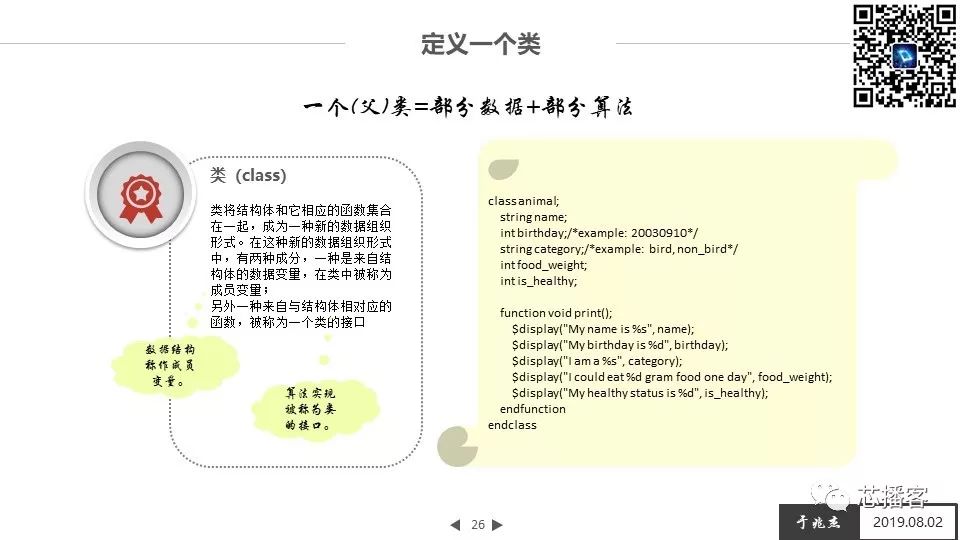

定义一个类

类将结构体和它相应的函数集合在一起,成为一种新的数据组织形式。在这种新的数据组织形式中,有两种成分,一种是来自结构体的数据变量,在类中被称为成员变量;另外一种来自与结构体相对应的函数,被称为一个类的接口。

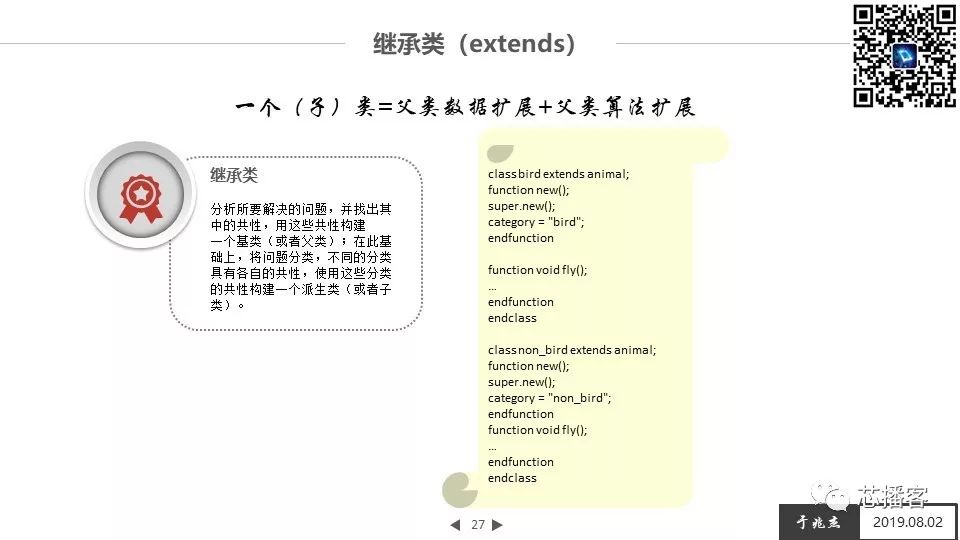

继承一个类

分析所要解决的问题,并找出其中的共性,用这些共性构建一个基类(或者父类);在此基础上,将问题分类,不同的分类具有各自的共性,使用这些分类的共性构建一个派生类(或者子类)。

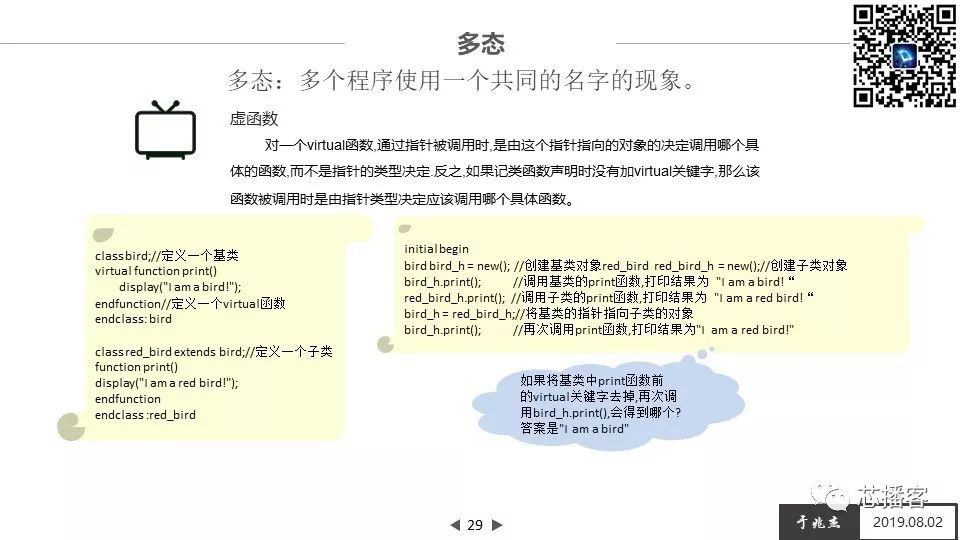

多态:多个程序使用一个共同的名字的现象。

静态变量和方法

一个类的所有实例都共享变量的一个版本,也就是说所有实例都共享同一个copy,该变量对所有实例都是可见并相同的。使用关键字static产生。

类的参数化定义

审核编辑 :李倩

-

Modelsim XE是否支持System Verilog2018-11-27 1957

-

System Verilog问题和语言参考手册规范2020-12-24 3001

-

Verilog HDL华为入门教程2010-02-11 1171

-

Verilog HDL入门教程(华为绝密资料)2010-04-02 6254

-

VHDL,Verilog,System verilog比较2012-01-17 1982

-

Verilog 入门的实例代码2016-05-24 745

-

Verilog HDL 华为入门教程2016-06-03 1364

-

基于System Verilog中的随机化激励2017-10-31 1034

-

基于System Verilog的可重用验证平台设计及验证结果分析2018-01-12 3359

-

System Verilog与verilog的对比2021-09-28 4764

-

System Verilog与verilog的概念有何不同2021-10-19 5477

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2389

-

浅谈System Verilog的DPI机制2023-05-23 3861

-

system verilog语言简介2024-11-01 450

-

Verilog 测试平台设计方法 Verilog FPGA开发指南2024-12-17 1937

全部0条评论

快来发表一下你的评论吧 !