关于Vivado Non-project,我们应知道的一些问题

描述

Vivado支持Project模式也支持Non-Project模式。两者既可以支持图形界面也支持Tcl命令,但用到的Tcl命令是不同的,不能混用。通常,Project模式应用更广,便于初学者学习,同时也便于工程管理。Non-Project模式编译时间会比Project模式短,因为所有数据存储在内存,直接内存读取数据比硬盘读取要快一些。这里我们探讨一下使用Non-Project模式时可能碰到的一些问题。

如何读取SystemVerilog文件?

在Non-Project模式下,可以通过read_*命令将设计用到的文件添加到工程中,例如:read_verilog可读取设计所需的Verilog文件(文件后缀为.v或.vh),当为.vh时,表明该文件为Verilog Header文件,在Non-Project模式下并不需要特别指明。但是如果读取的是SystemVerilog文件(文件后缀为.sv)或者使用了SystemVerilog语法的Verilog文件时,就需要在read_verilog命令后添加选项-sv。

如何读取VHDL-2008文件?

类似地,可以通过read_vhdl读取设计所需的VHDL文件,文件后缀为.vhd。但如果VHDL文件使用了VHDL-2008语法,在使用该命令时就要添加选项-vhdl2008。

如何同时读取多个同类型的设计源文件?

使用Non-Project模式时,通常建议将所有的待综合的HDL文件无论是Verilog/VHDL/SystemVerilog放在同一个文件目录下,例如放置在src/hdl目录下,这样可以方便地对同一类文件进行快速读取。例如,读取所有的VHDL文件可用如下命令,这里使用了Tcl命令glob,这种情况下该命令可返回所有的VHDL文件。如果要读取所有的Verilog文件,就用glob ./src/hdl/*.v即可。 read_vhdl [glob ./src/hdl/*.vhd]

如何处理IP?

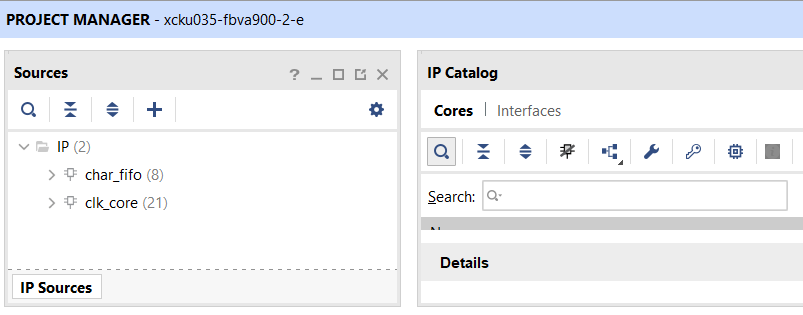

设计中我们不可避免地会用到IP,无论是Project模式还是Non-Project模式,都建议创建IP工程,以单独管理IP,如下图所示,这对于后续维护和升级IP都大有裨益。

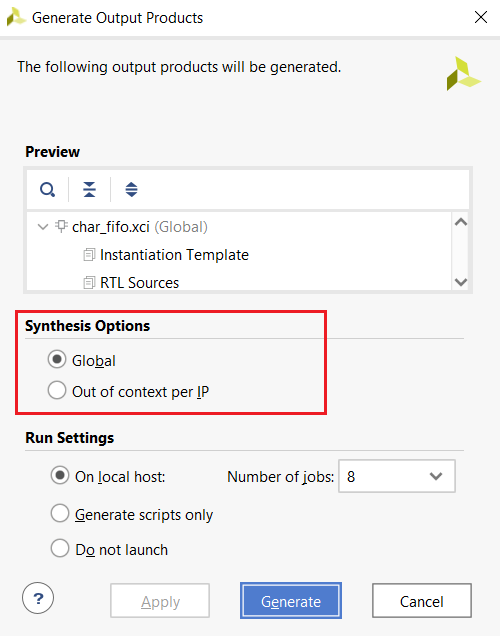

IP即可采用全局综合方式,又可采用OOC综合方式,这在生成IP输出文件时就要确定,也只能在此界面确定而无法通过属性修改,如下图所示。

可以通过命令read_ip读入IP,但该命令只能读入.xci文件,并不会读入预先生成的dcp文件。如果已在IP工程中完成了对IP的OOC综合,那么无需在Non-Project模式下再次对IP进行综合。否则,要先对IP通过命令synth_ip进行OOC综合,此时要用到如下两个命令。get_ips后也可跟随具体的IP名称。执行了synth_ip之后才可以对整个设计执行综合。

generate_target all [get_ips]

synth_ip [get_ips] -force

在Non-Project模式下对IP通过synth_ip执行OOC综合时,要先指定芯片型号,否则工具会按默认的芯片型号进行综合。指定芯片型号要用set_part命令,如下所示:

set_part [get_parts xcku035-fbva900-2-e]

如何处理第三方综合工具提供的网表文件?

审核编辑:汤梓红

-

关于Vivado non-project模式2022-10-17 4880

-

请教一些关于CC2541F256这颗芯片的一些问题2021-08-02 2542

-

Vivado设计流程指导说明2021-03-25 1028

-

VCS独立仿真Vivado IP核的一些方法总结2021-03-22 5604

-

如何用Tcl实现Vivado设计流程介绍2020-10-21 4514

-

LED照明一些问题的解决方案英文资料2018-04-16 1315

-

关于STM32f1和f4编程的一些问题解决方案2018-04-03 1000

-

关于续流二极管的一些问题2016-07-26 794

-

关于红外通信的一些问题知识点2016-05-05 1065

-

cadence画板中遇到的一些问题2016-02-25 924

-

请教关于GAL的一些问题2012-10-31 2786

-

固态继电器及在应用中一些问题的探讨2009-07-27 815

全部0条评论

快来发表一下你的评论吧 !