仿真Xilinx网表

描述

Xilinx-vivado的网表形式有edf和dcp两个方式,两个方式各有不同。对于仿真来说,两者均需转换为verilog的形式进行仿真,只是使用的命令不同。

转换为仿真文件的命令

对于dcp文件可以在tcl中使用open_checkpoint命令或者从gui界面中选择file->open checkpoint打开dcp文件,之后使用wirte_verilg命令就可以生成对应的Verilog文件。

对于edf文件,gui界面中没有对应的选项,只有使用tcl命令。read_edif用于读取edf文件,之后输入link_desing -top xxx(xxx表示顶层名称,不要加后缀),最后再使用write_verilog命令就可以对应生成Verilog文件。

仿真工具的支持情况

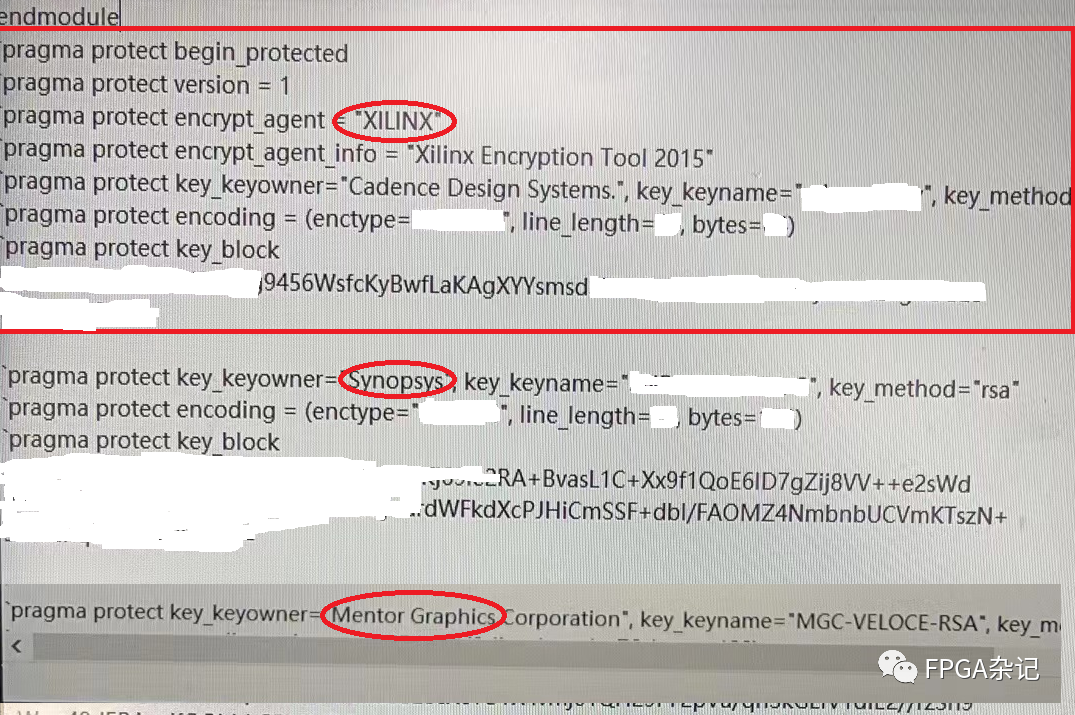

通过该以上两种方式生成的Verilog文件均可以在vivado中进行仿真。但是,dcp生成的verilog文件可以在modelsim中进行仿真,而edf生成的Verilog文件不能在modelsim、VCS等其他厂商的工具中进行仿真。edf生成的Verilog文件不能在modelsim、VCS等厂商仿真的原因在于该Verilog中只包含了xilinx对应的秘钥,而不包含其他厂商的秘钥,具体可以详见每一个生成文件末尾乱码的起始位置。只要有对应厂商的名字,就可以在对应的工具中进行仿真。

dcp生成的Verilog文件能够仿真的原因在于dcp格式只是一种文件打包的形式,转换为Verilog形式之后就相当于恢复了原来的文件源码,而源码文件一般情况下都可以在各个厂商的仿真工具中进行仿真,除非源码本身就包含固定的加密文件。

对于xilinx-ise的ngc格式的网表文件,使用netgen命令就可以生成对应的verilog形式的仿真文件。

PS:edif 和 dcp的区别:封装成 edif 文件时,不能将 Xilinx ip 核封装在文件中,而 dcp 可以;例化时,edif 是网表文件,例化时需要增加同名的 hdl 文件,dcp 文件其实是一个压缩文件,例化时只需使用 dcp 文件即可

审核编辑:汤梓红

-

ADS调用spectre网表仿真异常—薛定谔的NetlistInclude2024-03-07 6673

-

Xilinx快速仿真器:用户指南2023-09-15 792

-

如何将包含XIlinx IP的用户模块封装成网表文件2023-05-18 3749

-

网表仿真与RTL仿真相比有何优势2021-11-04 5541

-

Xilinx:如何使用Zynq仿真平台2019-01-03 5741

-

硬件协同仿真或HDL网表生成遇到错误2018-11-29 3129

-

如何使用Xilinx的仿真平台加速自己的开发2018-11-21 4501

-

基于 FPAG xilinx vivado 仿真模式介绍2018-01-24 5626

-

Xilinx更新以太网MAC控制器设计2017-02-09 344

-

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?2016-09-07 15567

-

MODELSIM仿真(适合xilinx ISE)2015-11-30 912

-

Xilinx Fpga前仿真后仿真2012-08-15 1896

-

Altera和Xilinx Modelsim仿真库2012-08-10 2213

-

Xilinx FPGA的仿真技术设计指南2011-03-16 934

全部0条评论

快来发表一下你的评论吧 !