为了方便仿真这样写个ROM

电子说

1.4w人已加入

描述

FPGA中有专门的ROM IP Core,如果按照规范用Verilog编写的ROM文件可以被工具综合成RAM资源,而ASIC在需要后端去做专门Memory,前端仿真可以自己编写RAM/ROM/FIFO/RegFile IP。为了方便仿真这样写个ROM,方便初始化。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

module single_port_rom(/*autoarg*/

Outputs

q,

Inputs

clk

);

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 8;

input [ADDR_WIDTH-1:0] addr;

input clk;

output reg [DATA_WIDTH-1:0] q;

reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial begins

rom);

rom);

end

always @ (posedge clk)begin

q <= rom[addr];

end

endmodule

系统函数$readmemh和$readmemb分别用来读取十六进制文件和二进制文件。貌似没有读十进制的。txt中的数据每行一个不需要逗号和最后一个数据后面的分号,数据格式对应。更多使用可以查询IEEE的Verilog语法手册。例化方式和rom IP一样可参数化配置任意大小

single_port_rom

#(

.DATA_WIDTH(DATA_WIDTH),

.ADDR_WIDTH(ADDR_WIDTH)

)

u_sin(/*autoinst*/

// Outputs

.q (dout[DATA_WIDTH-1:0]),

// Inputs

.addr (addra[ADDR_WIDTH-1:0]),

.clk (clk));

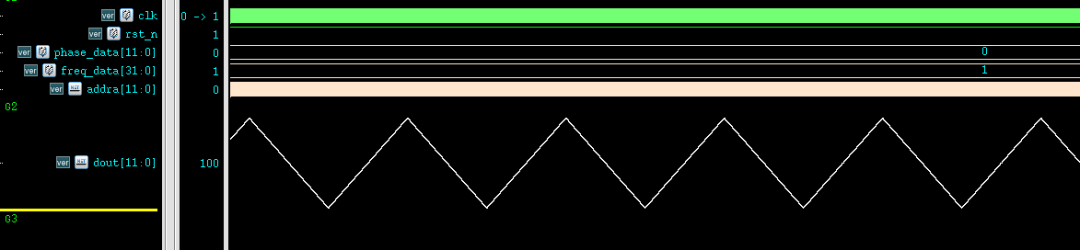

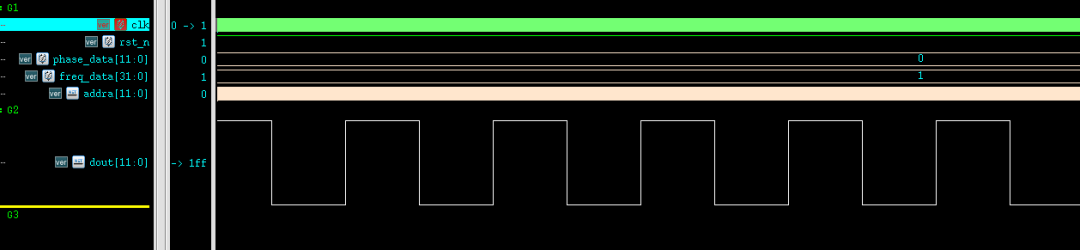

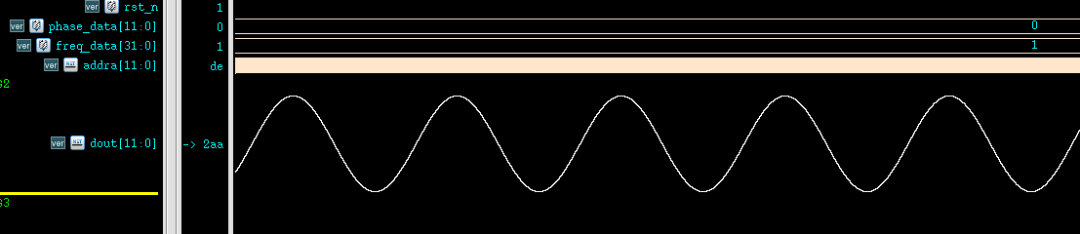

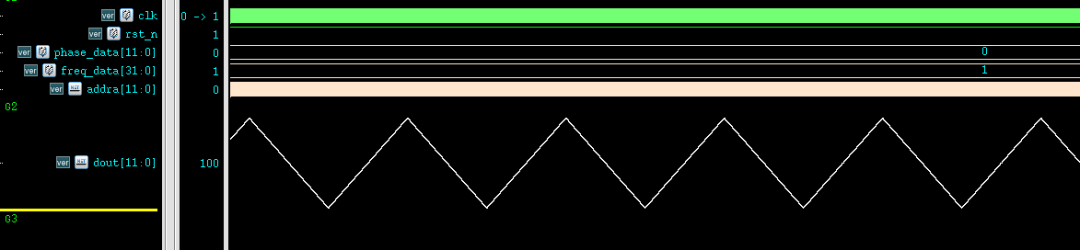

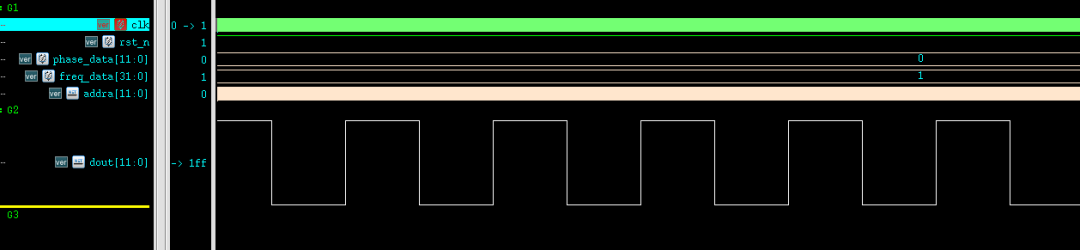

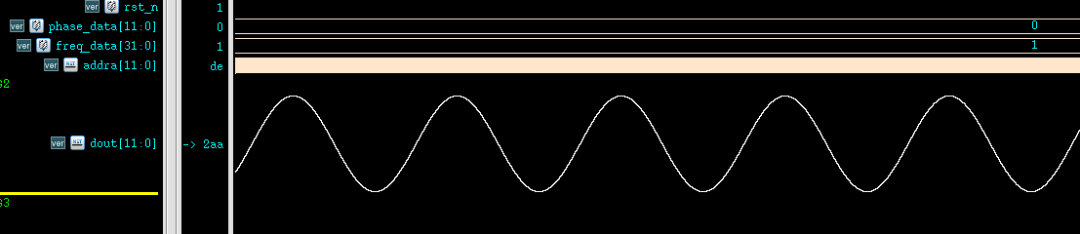

整了三个波形,仿真能跑起来。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

将设计电路参数化可重复使用,构建自己的代码库,搭建起你的数字积木。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Modelsim SE仿真ISE下定制的ROM2012-02-29 2901

-

rom 的modelsim 仿真 问题 和 解决方法2014-03-06 14380

-

关于rom配置后的仿真问题2014-05-13 3922

-

关于用modelsim仿真ROM的问题2014-10-30 10305

-

modelsim 仿真 altera IP核(ROM,RAM实例2015-11-19 6118

-

哪位高手能帮我做一个仿真,写个程序?2016-08-02 3713

-

NIOS II 上rom仿真问题2017-03-21 2830

-

ROM,ROM原理是什么?2010-03-24 6781

-

EWB电路仿真软件(使用方便简单)2012-12-08 1739

-

用TensorFlow写个简单的神经网络2018-03-23 5632

-

FPGA学习:使用matlab和ISE 创建并仿真ROM IP核2018-10-25 4755

-

rom是什么存储器_rom的功能是什么2020-12-07 50523

-

如何操作ECO方式更新RAM/ROM初始值更方便?2021-02-14 3656

-

网站总被攻击?写个自动封禁IP的脚本给你2023-01-29 1684

-

Python-写个可转债分析器2023-02-16 2808

全部0条评论

快来发表一下你的评论吧 !