承受现代IGBT/MOSFET栅极驱动器绝缘能力的最大功率限制

描述

作者:Dr. Bernhard Strzalkowski

本文通过故意破坏IGBT/MOSFET功率开关来研究栅极驱动器的隔离耐受性能。

在电动/混合动力汽车等高可靠性、高性能应用中,隔离式栅极驱动器需要确保隔离栅在任何情况下都保持完整。由于Si-MOSFET/IGBT的不断改进以及GaN和SiC技术的引入,现代功率转换器/逆变器的功率密度正在上升。因此,需要新的、高度集成的、隔离的、可靠的栅极驱动器。这些驱动器的外形尺寸很小,因为电气隔离已经集成在驱动器芯片上。这种电气隔离可以通过集成的高压微变压器或电容器来实现。1, 2, 3一个不可预测的系统故障可能会损坏和爆炸电源开关甚至整个电源逆变器。因此,需要研究高功率密度逆变器的栅极驱动器隔离安全性能。在最坏的情况下,当电源开关损坏时,必须测试和验证隔离可靠性。

介绍

在最坏的情况下,当高功率MOSFET/IGBT发生故障时,逆变器的数千μF组电容将迅速放电。释放的能量会导致 MOSFET/IGBT 损坏、封装爆炸和等离子体退出环境。4一部分能量流入栅极驱动器电路,导致电气过应力。5由于功率密度极高,即使芯片本身发生故障,驱动芯片的构造也应保持电气隔离。

构建现代、高度集成的栅极驱动器

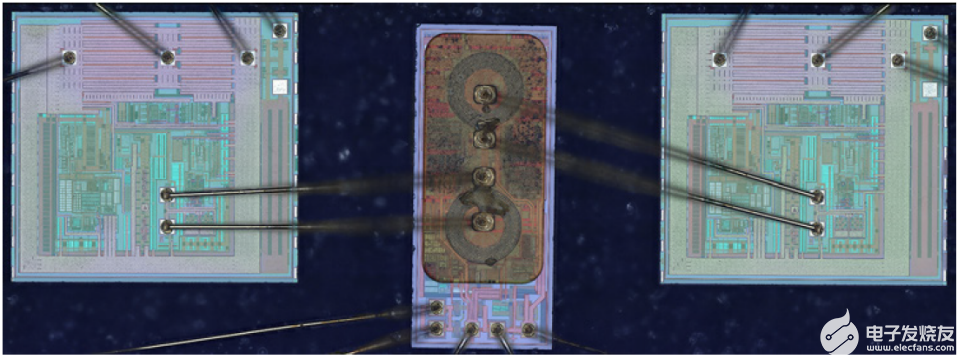

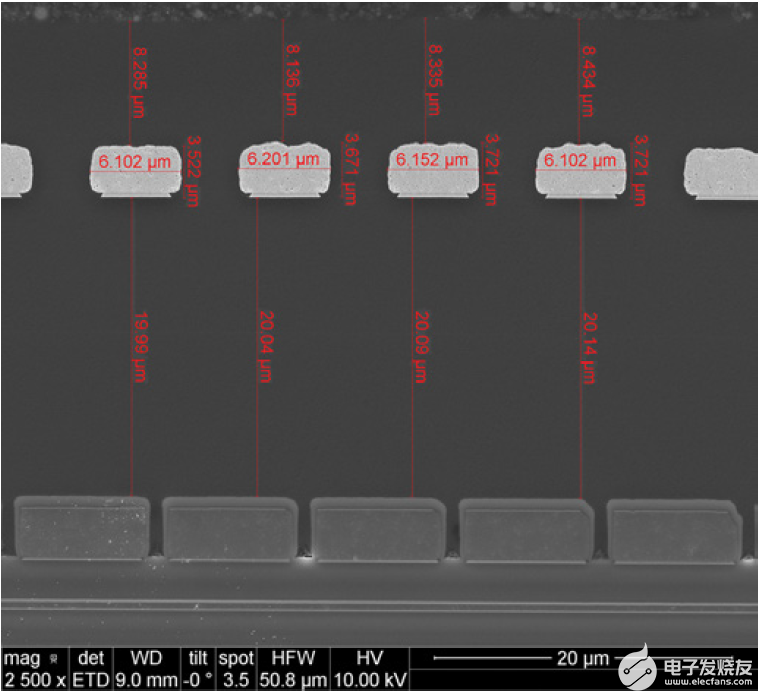

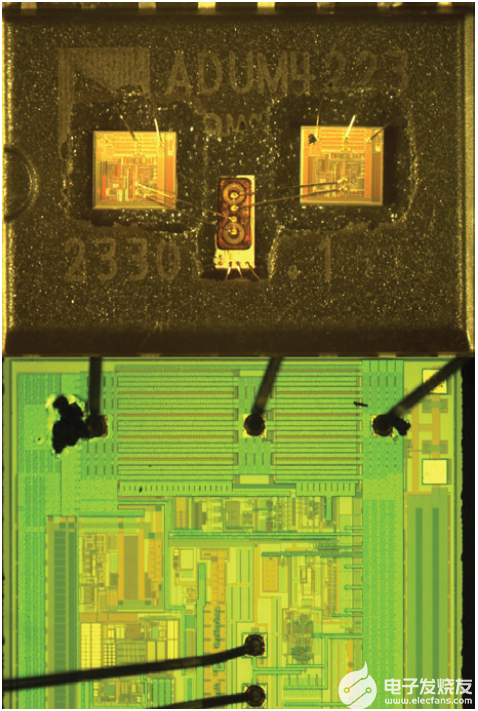

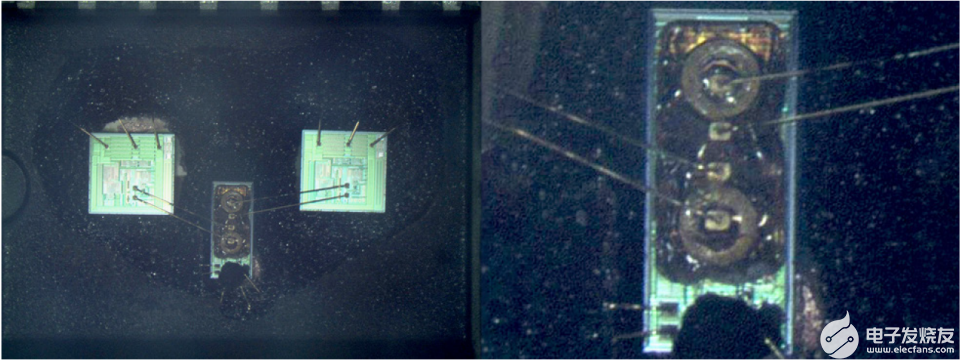

芯片级隔离采用平面微变压器方法,提供电气隔离。它采用晶圆级技术制造,并配置为半导体元件外形。1i耦合器通道由两个集成电路(IC)和芯片级变压器组成(图1)。绝缘层提供隔离栅,以分隔每个变压器的顶部和底部线圈(图 2)。数字隔离器在刨光变压器线圈之间使用至少20 μm厚的聚酰亚胺绝缘层,这是晶圆制造工艺的一部分。这种制造工艺允许隔离元件以低成本、卓越的质量和可靠性与任何代工厂半导体工艺集成。图2中的横截面显示了由厚聚酰亚胺层隔开的顶部和底部线圈的匝数。®

图1.MOSFET半桥驱动器ADuM3223的芯片排列。

图2.ADuM3223:微变压器横截面。

封装内的分离式引脚框架完成了隔离。当栅极驱动器输出芯片因电源开关爆炸而损坏时,内部芯片分区和布置必须确保隔离层保持完整。已实施多项保护措施,以确保栅极驱动器隔离的生存:

正确确定外部电路的尺寸,以限制流入栅极驱动器芯片的能量流

输出晶体管在驱动芯片上的适当放置

微变压器在芯片上的适当放置

封装内部的适当排列控制和驱动器芯片

ADuM3223的内部芯片排列栅极驱动器(图1)展示了一个芯片放置示例,可避免极端电气过应力期间的电气隔离击穿。

模拟最坏逆变器故障情况的破坏性测试

构建了一个具有385 V和750 V两个电压电平的测试电路,以模拟真实的功率逆变器条件。电压电平385 V在需要使用110 V/230 V交流电网进行功率因数校正的系统中非常常见。750 V 的电压电平在使用额定击穿电压为 1200 V 的开关的驱动应用中使用的大功率逆变器中很常见。

在破坏性测试中,一个逆变器支路(由电源开关和适当的驱动器组成)被打开,直到开关失效。记录销毁期间的波形,以确定流入栅极驱动器芯片的能级。研究了几种保护措施,以限制流入栅极驱动器电路的破坏能量。在破坏性测试中使用了几种类型的IGBT和MOSFET。

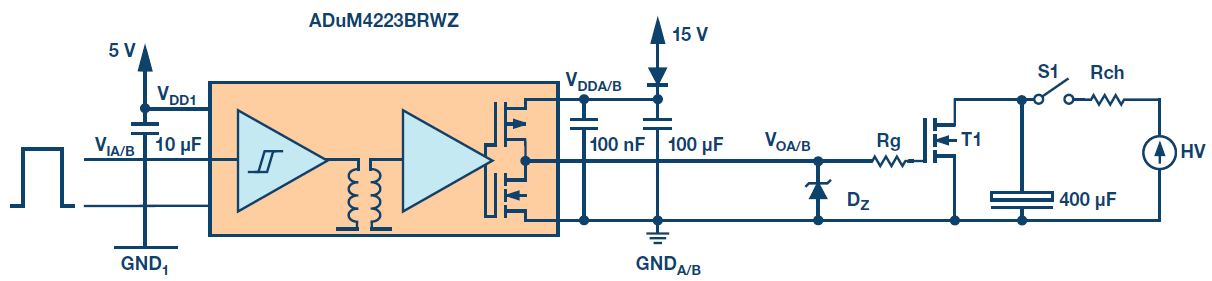

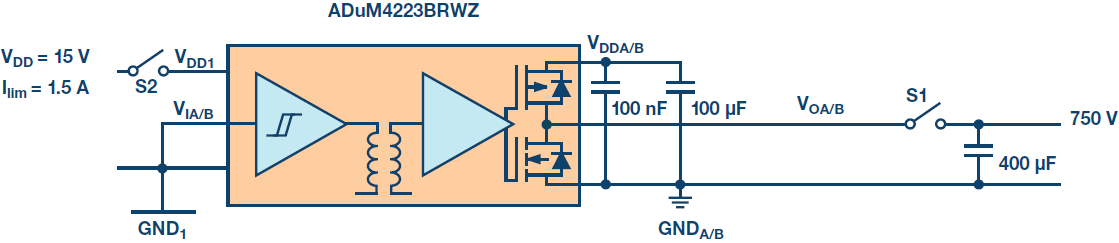

具有受控MOSFET/IGBT损坏的测试电路

对于IGBT/MOSFET驱动器电气过应力测试(EOS测试),设置了一个非常接近真实条件的电路。该电路包括适合功率范围为5 kW至20 kW的逆变器的电容器和电阻器。对于轴向型栅极电阻Rg,使用2 W额定功率金属电阻器。应用一个阻断二极管D1,以避免能量从高压电路反转到外部电源。这也反映了现实条件,因为浮动电源包括至少一个整流器(即自举电路)。高压电源HV通过包括电荷电阻Rch和一个开关S1的电路对块电解质电容充电。

对于EOS测试,施加500 μs的导通信号来控制输入VIA或 V兴业银行.这种通过微隔离传输的导通信号导致功率晶体管T1短路和破坏。在某些情况下,观察到晶体管封装爆炸。

使用两种电压电平的四种电源开关类型来模拟逆变器损坏。针对特定开关类型的第一次测试是在没有功率限制电路的情况下进行的,然后是使用功率限制电路进行的。为了限制在损坏阶段流入驱动器电路的能量,在某些测试中,齐纳二极管Dz(BZ16,1.3 W)直接施加到驱动器输出引脚。还研究了栅极电阻的不同值。

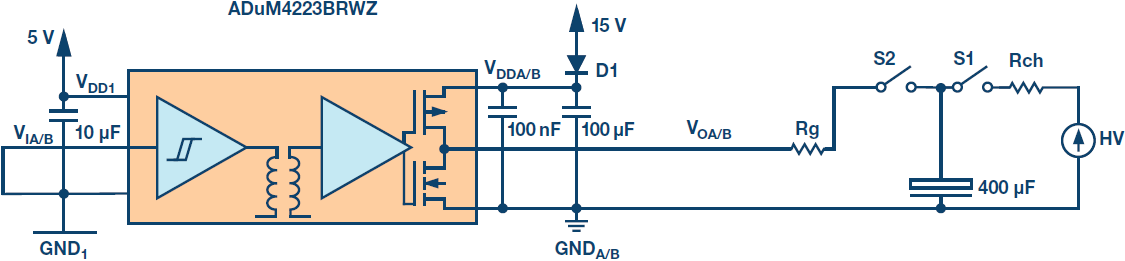

无能量限制的直接栅极驱动器电路损坏测试电路

进行了另一个模拟最坏情况的测试,其中破坏性能量直接施加到栅极驱动器的输入和输出芯片上。在这种破坏性测试中,充满电的大容量电容器直接连接到栅极驱动器的输出引脚(图 4)。该测试表现出最差的过应力,因此检查了隔离耐受能力。能量直接流入驱动器电路,而栅极电阻是唯一的功率限制器件。继电器S2将高压耦合到栅极驱动器输出电路中。

图3.EOS电路ADuM4223的布局,用于测量电源开关损坏对隔离耐受性的影响。

图4.EOS电路ADuM4223的布局,用于确定隔离耐受的能量限值。

图5显示了没有任何器件限制能量流入输入和输出芯片的最差情况测试。通过开关S1将高压750 V直接施加到输出芯片中,代表了最坏的情况,即中间高压750 V在没有能量限制栅极电阻的情况下被引导至驱动器芯片。

图5.EOS电路ADuM4223在最坏情况下,当能量直接施加到输入和输出芯片时。

另一种可能的最坏情况是向驱动器初级侧的控制芯片施加过高的电源电压。建议的最大输入电源电压为5.5 V。如果产生输入电压的DC-DC转换器失去稳压,其输出电压可能会增加。在失去稳压的情况下,对于最先进的DC-DC转换器,转换器的输出电压可能会增加两到三倍。施加到ADuM4223输入芯片的能量有限,并且一如既往,电阻、电源开关和电感器等其他器件也已到位。这些设备阻碍能量流入控制芯片。选择15 V电源电压,电流限制为1.5 A,以真实模拟DC-DC转换器故障。

实验结果

表1显示了使用图3、图4和图5电路进行的过应力测试的结果。为了确定保护电路的影响,对每种MOSFET/IGBT功率开关类型进行了两次测试。对于 9、10 和 11 的最坏情况测试,使用机械开关 S1 和 S2。

| 测试 | ADuM4223 | 博士。# | U/V | Rg | 兹 | 结果 | Ed/mJ | 评论 | 开关 | 电路 |

| 1 | 1 | B | 385 | 4.7 | 不 | 损伤 | 8.5 | FDP5N50 | 图3 | |

| 2 | 1 | 一个 | 385 | 2 × 2.2 | 16 | 无损坏 | 3.5 | FDP5N50 | 图3 | |

| 3 | 2 | 一个 | 385 | 2 × 2.2 | 16 | 损伤 | Rg, DZ ok | 2xFDP5N50 | 图3 | |

| 4 | 2 | B | 385 | 12 | 16 | 无损坏 | 2xFDP5N50 | 图3 | ||

| 5 | 2 | B | 385 | 4.7 | 16 | 无损坏 | 0.5 | spw24N60C3 | 图3 | |

| 6 | 2 | B | 385 | 3.9 | 不 | 无损坏 | spw24N60C3 | 图3 | ||

| 7 | 2 | B | 750 | 4.7 | 16 | 无损坏 | 20 | Rg 伤害,DZ 还可以 | IXGP20N100 | 图3 |

| 8 | 2 | B | 750 | 4.7 | 不 | 损伤 | 25 | Rg 伤害 | IXGP20N100 | 图3 |

| 9 | 1 | 一个 | 150 | 4.7 | 不 | 损伤 | Rg 伤害 | 交换机 S2 | 图4 | |

| 10 | 3 | 一个 | 750 | 0 | 不 | 损伤 | 最坏情况输出芯片 | 交换机 S1 | 图5 | |

| 11 | 4 | 输入 | 15 | 0 | 不 | 损伤 | 最坏情况输入芯片 | 交换机 S2 | 图5 |

通常,齐纳二极管有助于保护驱动器电路,如表所示(将测试1与测试2进行比较时)。但是,当栅极电阻值太小时,尽管有齐纳二极管,驱动器也会被破坏(比较测试3和测试4)。

通过将测试 2 与测试 3 以及测试 3 与测试 4 进行比较,可以估计驾驶员损坏能量。测试5和6给出了一个非常有趣的结论:超结MOSFET似乎比具有相同额定功率的IGBT产生明显低于流入栅极驱动器的能量水平。测试9、10和11(无限能量流入控制和驱动器芯片)的目的是研究最坏情况下的隔离耐受性能。

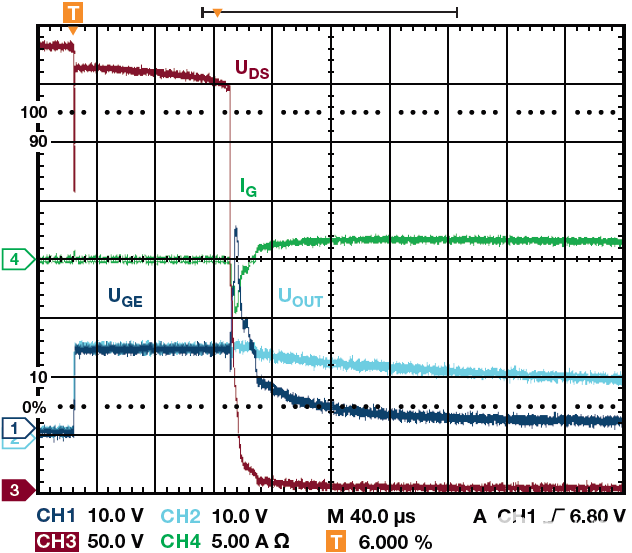

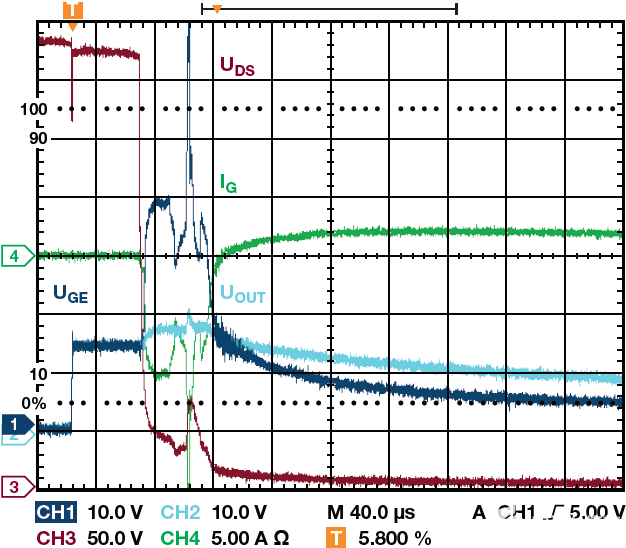

MOSFET 与 IGBT 的不同破坏行为

破坏性测试显示不同的波形受到电源开关损坏。图6显示了超结MOSFET的波形。从导通到芯片破坏之间的时间段约为100 μs。流入驱动器芯片的电流非常有限,可以承受过应力。对于相同的测试条件,标准MOSFET会产生明显更高的栅极电流和过压,从而导致驱动器损坏,如图7所示。

图6.损坏SPW2460C3产生的波形图;没有观察到驱动程序损坏。

图7.通过并行损坏 2xFDP5N50 而产生的波形图;栅极驱动器出现故障。

切屑损坏分析

栅极驱动器的部分封装在不同开关和不同测试条件下显示出类似的芯片损坏。图8显示了测试8中基于P-MOSFET的输出驱动器级的损坏情况(表1)。在 750 V 的大电压下进行的测试引起了 IGBT 爆炸,以及限制装置 Rg 和 DZ 的破坏;但是,只有非常靠近引脚V键合线的小熔融区域DDA是可见的。损伤阶段的栅极过电流通过P-MOSFET的本征二极管流入100 μF电容。由于电流拥挤,靠近键合线的区域熔化了。未观察到驱动器芯片进一步损坏,控制芯片上未观察到隔离损坏。图9显示了测试9期间的熔融区域,其中150 V的高电压直接施加到驱动器芯片上。控制芯片的电气隔离经受住了这种极端的过应力测试。

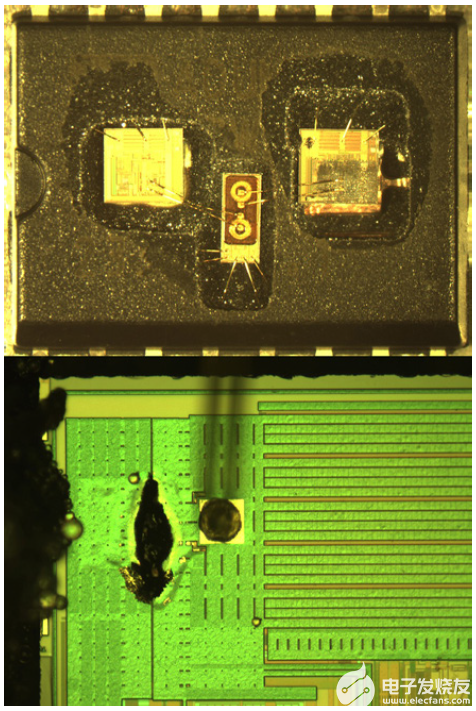

图8.栅极驱动器芯片照片,显示测试8期间的损坏区域(ADuM4223 #1)。仅在输出芯片上出现小熔融区域。未检测到隔离损坏。

图9.栅极驱动器芯片照片显示测试9期间损坏区域(ADuM4223 #2)。极端的电气过应力并没有破坏控制芯片。未检测到隔离损坏。

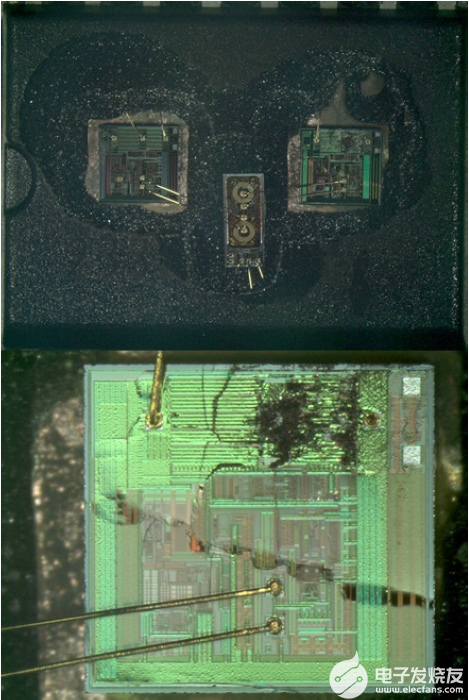

通过开关S1(图5)将750 V直接施加到输出芯片中是最坏的情况,因为驱动器电路中消耗了无限的能量。图10中的芯片照片显示了驱动器电路的明显熔融区域,与图9中的损坏形成鲜明对比,其中超过能量受到栅极电阻的限制。

图 10.栅极驱动器芯片照片,显示测试 10 期间损坏的区域。施加到输出驱动器的无限能量破坏了电路;显著的熔融区域。但是,没有观察到隔离的损坏。

初级侧的最坏情况是向控制芯片施加过高的电源电压。因此,在测试11中,对V施加15 V的电源电压电子数据处理引脚(图 5),明显超过绝对最大额定值 7.0 V。图11中的照片显示了V附近的芯片熔融区域电子数据处理针。

图 11.输入控制芯片照片,显示测试 11 期间损坏的区域。施加到电路上的能量在V周围形成了一个非常有限的熔融区域。电子数据处理针。没有观察到隔离的损坏。

结论

电源开关的破坏性测试不会影响集成栅极驱动器ADuM4223/ADuM3223的隔离耐受性。即使驱动器因流入输出芯片的能量过多而损坏,也只会发生局部和有限的熔融区域。多余的能量通过P-MOS驱动晶体管引导到隔断电容中。因此,熔融区域只发生在P-MOS区域。

ADuM4223/ADuM3223的芯片布置不允许熔融区域扩散到控制芯片(包括电隔离信号变压器)中。为了限制流入驱动器输出的能量,可以使用齐纳二极管。齐纳二极管与适当的栅极电阻相结合,可以在电源开关损坏阶段保护栅极驱动器。可以将栅极电阻设计为在正常工作期间管理功耗,并在电源开关损坏期间将驱动器与电源开关分开。当高电压直接施加到芯片中时,栅极电阻器充当保险丝。电阻器将芯片损坏限制在输出电源开关周围的小熔融区域。

在最坏的情况下,当对输出芯片施加无限能量时,驱动器输出引脚附近的熔融区域有限。该测试不影响隔离耐受性。在初级侧的最坏情况下,当电源电压明显上升到绝对最大额定值以上时,观察到电源电压引脚周围的熔融区域有限。在任何电气过应力测试中,都没有减弱隔离的迹象。随后进行的高压隔离测试证实了电气微隔离的耐受性能。适当的芯片结构以及驱动器封装内的芯片排列避免了破坏性能量扩散到微变压器的高压隔离层中。

审核编辑:郭婷

-

最大功率点追踪的含义 最大功率点跟踪的意义2024-05-01 4768

-

现代IGBT/MOSFET栅极驱动器 提供隔离功能的最大功率限制2023-11-22 750

-

常见的MOSFET以及IGBT绝缘栅极隔离驱动技术解析2019-07-03 5383

-

最大功率传输分析2019-06-23 13366

-

现代IGBT/MOSFET栅极驱动器提供隔离功能的最大功率限制2019-04-16 6797

-

最大功率传输定理证明2018-08-22 20656

-

电路设计--最大功率传输2017-08-07 1678

-

双路智能大功率IGBT驱动器2017-03-04 1312

-

大功率IGBT驱动技术的现状与发展2012-12-08 3735

-

大功率igbt驱动保护电路的分类2012-07-09 2904

-

最大功率跟踪逆变器的设计与实现2011-09-16 9169

-

基于IR2101最大功率跟踪逆变器的设计2010-11-23 2319

-

车载功放的最大功率2010-01-04 4933

全部0条评论

快来发表一下你的评论吧 !