奇异摩尔:Chiplet如何助力高性能计算突破算力瓶颈

描述

12月27日,中国集成电路设计业2022年会暨厦门集成电路产业创新发展高峰论坛(ICCAD 2022)在厦门国际会展中心开幕。奇异摩尔产品及解决方案副总裁祝俊东应邀出席,在IP与IC设计专题论坛上发表了《智能时代,Chiplet 如何助力高性能计算突破算力瓶颈》的主题演讲。祝俊东向现场各位来宾介绍了基于Chiplet 的异构计算体系的优势和挑战,奇异摩尔在Chiplet体系方面的技术优势,以及如何帮助高算力客户高效构建 Chiplet 系统。

算力时代:集成电路面临全面挑战

进入后摩尔时代,传统方式推进芯片性能带来的“经济效益”锐减。在高性能计算、自动驾驶、下一代个人计算中心等苛求芯片算力、功耗比的领域,开始面临着共同算力需求持续提升、性能提升放缓、研发成本持续上升、量产成本持续上升等挑战。目前,单一计算类型和架构的处理器已经无法处理更复杂、更多样的数据。计算机体系架构逐渐向通用异构时代转变,异构计算可以满足通用和专用的架构创新,通过组合海量异构芯片实现数量繁多的专用应用需求,如今已成为行业公认的未来趋势。

Chiplet让大算力芯片设计变得更加简单和易得。通过异构Chiplet将全算力单元Chiplet化,可以帮助芯片性能得到持续提升。Chiplet通过少量通用单元的复用和重组,可以轻松的组成海量异构芯片,并能广泛的应用在数据中心、自动驾驶、智能座舱、平板电脑、手机等领域。

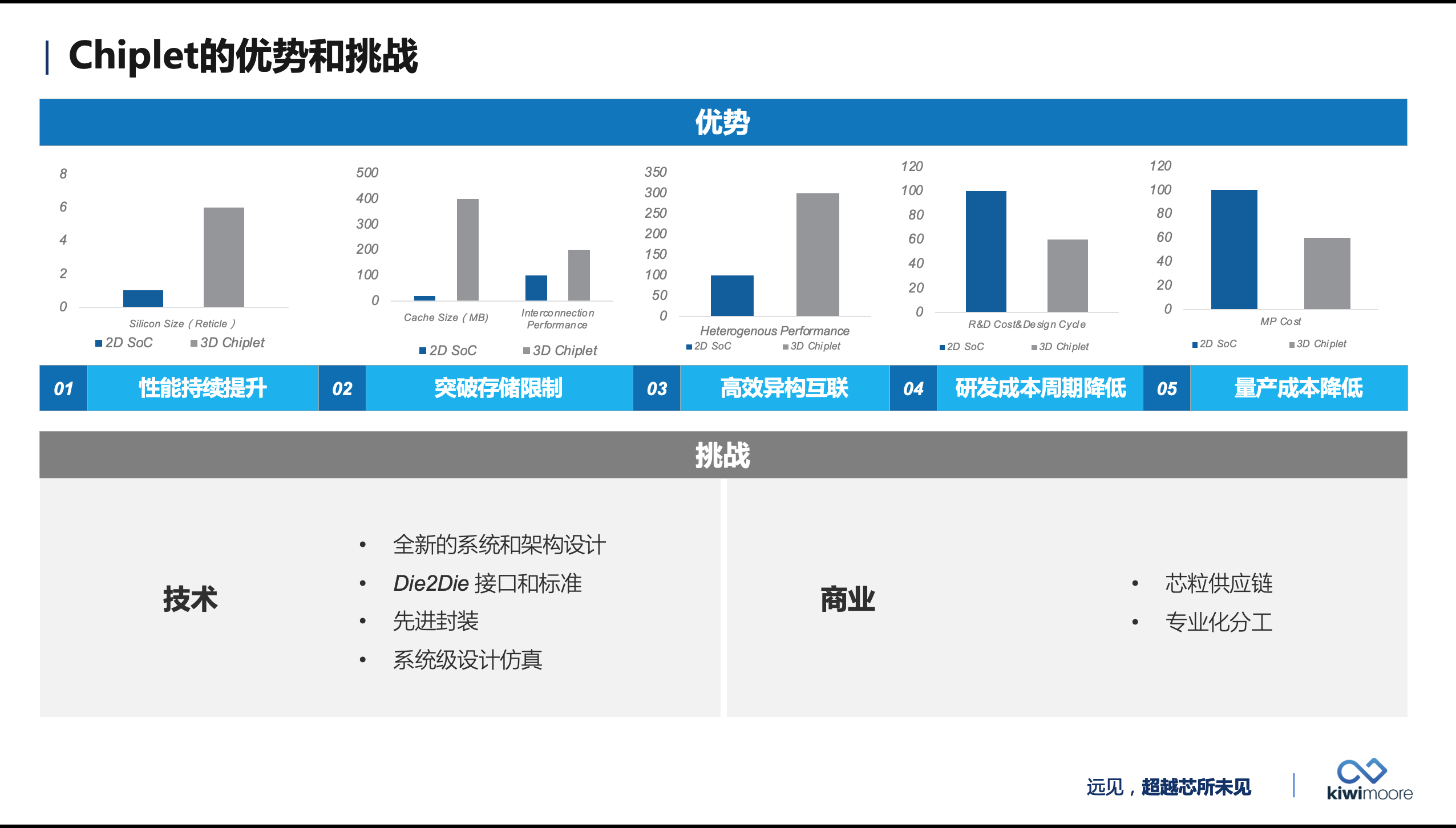

Chiplet作为一种新型架构,能有效帮助客户提升性能,突破存储限制、高效异构互联,并能有效缩短研发成本周期、降低量产成本。当然,Chiplet也面临着许多商业和技术上的挑战,如系统设计、芯粒设计、Die2Die 接口和标准、先进封装、系统级设计仿真等技术挑战,以及芯粒供应链、专业化分工等商业方面的挑战。那么,究竟要如何高效构建 Chiplet 系统?

如何高效构建 Chiplet 系统?

祝俊东表示,Chiplet 系统构建有两大核心要素“性能、成本”。即在产品的预期性能需求(算力、存储、带宽、延时、功耗等)和各方面的成本(如设计成本、晶圆成本、介质成本、封装测试成本)之间寻求平衡。在确定了客户产品目标和目标维度后,即可依照Chiplet架构选择、选择高速互联方式、芯粒拆分及选择、系统及芯粒优化、系统级验证方针的流程进行Chiplet系统的构建。

奇异摩尔始终专注于2.5D及3D Chiplet产品及服务,基于面向下一代计算体系架构,提供全球领先的2.5D及3D Chiplet异构集成通用产品和全链路服务,其中包含高性能通用底座Base die、高速接口芯粒IO Die、高速Die2Die IP、Chiplet软件设计平台等产品,可以全方位满足Chiplet系统的需求,主要应用于下一代数据中心、自动驾驶、下一代个人计算平台等快速增长市场。

祝俊东介绍,在Chiplet的两项关键技术Die2Die 接口和互联架构方面,奇异摩尔拥有两大核心解决方案:动态配置高效 Chiplet 互联架构 Kiwi Fabric,高性能低功耗低延时 Die2Die 接口 Kiwi Link。此外,奇异摩尔还提供一站式Chiplet 系统设计服务,帮助客户进行系统及芯粒优化设计。

随着后摩尔时代的到来,基于Chiplet 的同构/异构系统级芯片已逐渐成为高性能计算的主流,Chiplet方案具备持续提升性能、降低量产成本、降低研发成本、满足产品多样性需求,也同时面临着多种技术和商业上的挑战。

在今天,热度高涨的Chiplet定义繁多,奇异摩尔认为,可以从三个方面定义Chiplet。Chiplet是一种新的系统架构和芯片设计方法,是一种技术路线,也同样是一种商业战略的选择。因此,选择了Chiplet道路,不仅意味着芯片设计形式的转变,同样也影响着一家企业的未来。作为行业公认的半导体未来之路,Chiplet的成熟壮大需要芯粒生态、高速互联、先进封装、Chiplet EDA乃至整个产业链的协同支持。奇异摩尔相信,未来,市场一定会陆续涌现出越来越多的第三方 Chiplet 产品和方案提供商,全链路共同发力,迎来百家争鸣、百花齐放的行业未来。

-

IaaS+on+DPU(IoD)+下一代高性能算力底座技术白皮书2024-07-24 5291

-

名单公布!【书籍评测活动NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架构分析2024-09-02 3716

-

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”2023-02-21 1359

-

GPU如何突破算力供需瓶颈2023-08-22 1846

-

后摩智能与奇异摩尔正式签署战略合作协议2023-09-27 1686

-

Chiplet赛道火热 奇异摩尔完成亿元Pre-A轮融资2023-11-08 2356

-

奇异摩尔祝俊东:Chiplet和网络加速 互联时代两大关键技术2023-11-14 2158

-

奇异摩尔与润欣科技加深战略合作开创Chiplet及互联芯粒未来2023-11-30 6812

-

2023年Chiplet发展进入新阶段,半导体封测、IP企业多次融资2024-01-17 3429

-

奇异摩尔携手SEMiBAY Talk 邀您畅谈互联与计算2024-05-20 1554

-

奇异摩尔上海总部进驻上海浦东科海大楼2024-07-01 4477

-

中科曙光助力浙江精准医疗实验室突破算力瓶颈2025-02-13 968

-

云 GPU 加速计算:突破传统算力瓶颈的利刃2025-02-17 581

-

奇异摩尔受邀出席第三届HiPi Chiplet论坛2025-03-25 1781

-

奇异摩尔邀您相约2025中国AI算力大会2025-06-17 1407

全部0条评论

快来发表一下你的评论吧 !