数字控制可实现具有有源缓冲功能的高可靠性DC-DC电源转换

描述

通常,对于具有高输出电流的隔离式DC-DC电源应用,主要使用同步整流器(特别是MOSFET)。高输出电流还会在整流器上引入高di/dt。为了提高效率,MOSFET的选择主要取决于导通电阻和栅极电荷。然而,寄生体二极管反向恢复电荷(QRR) 和输出电容 (C开放源码软件).这些是影响 MOSFET 漏极上出现电压尖峰和振铃的关键参数。通常,随着 MOSFET 的击穿电压额定值的增加,导通电阻也会增加。本文提出了一种数字控制的有源钳位缓冲器,可以消除同步整流器上的电压尖峰和振铃。它还提供设计指南,以及隔离式DC-DC转换器(如半桥和全桥拓扑)的其他几个优点,同时提高可靠性并降低故障率。

介绍

始终需要具有高故障间隔时间 (MTBF) 的高可靠性电源。为了实现稳健的设计,可以使用开关的更高击穿电压额定值。但是,这会导致效率损失。因此,高效率和高可靠性在其应用中有些对立。作为下一代电源解决方案的一部分,业界对高效隔离式DC-DC转换器的需求一直稳定。这要求在次级侧使用同步整流器。整流器的额定值通常是器件两端电压尖峰的 1.2 至 1.5 倍。电压尖峰是由漏感、寄生走线电感和整流器输出电容(C开放源码软件),其谐振峰值可达整流器稳态反向电压的两倍。被动缓冲器可以以RC的形式使用1或刚果民盟2作为解决方案。虽然这些很受欢迎,但它们也是有损的,并导致效率略有下降。生成无损缓冲器的一些技术使用再生缓冲器,如 LCD3仅关注初级侧开关的缓冲器,或仅在电源开关关闭期间而不是在接通期间使用 RC 缓冲器。其他技术4, 5利用泄漏能量驱动小型高效转换器馈入输出电压端子。但是,这需要更高的组件数。其他技术6已将有源钳位缓冲器应用于全桥相移拓扑,以消除 ZVS 软开关应用中初级侧谐振电感引起的谐振,这在低占空比下具有局限性。

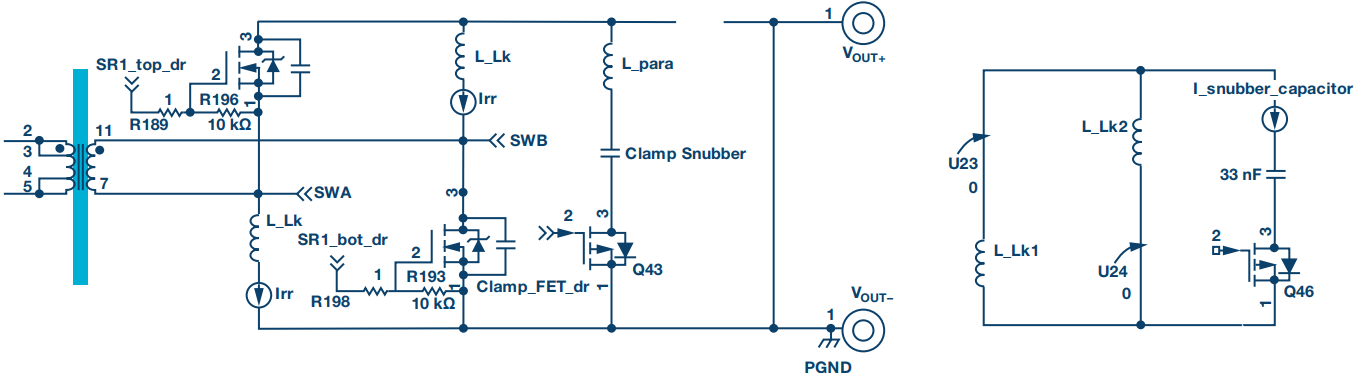

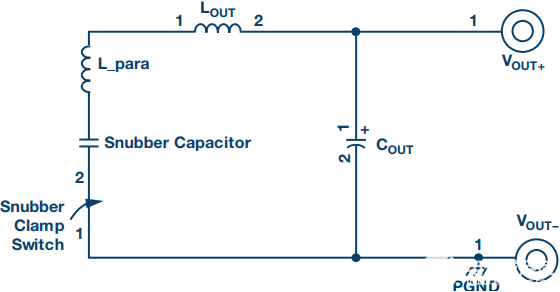

本文将仔细研究有源箝位缓冲电路及其数字实现,它可以防止电压偏移,特别强调消除MOSFET中寄生二极管的反向恢复损耗,这提供了其他一些额外的好处。转换器功率级(仅次级侧)的原理图如图1所示。

图1.功率转换器的次级侧显示有源箝位。

图1所示为隔离式DC-DC转换器的副边。次级侧由连接到变压器的H桥形式的同步整流组成。此外,还有输出滤波电感器(L外)和输出滤波电容(C外).有源箝位开关是P沟道MOSFET,用于电平转换栅极信号的栅极驱动由电容和二极管组成。

高频等效电路

在高频视图中,大电感和大电容器分别被认为是开路和短路的,而电路分析仅使用寄生和谐振电感和电容。这种方法可以简化电路以分析交流电流。这在谐振拓扑和涉及缓冲器的情况下特别有用,因为高频电流会在缓冲期间选择阻抗最小的路径。

电路的交流图如图2所示。输出滤波电感和输出滤波电容分别开路和短路。MOSFET的输出电容和漏感保持电路中不变。重点是转换器的次级侧,因为初级电压源短路,对分析没有贡献。

图2.(左)电源转换器次级侧的交流视图,显示有源箝位。(右)简化的交流视图。

同步FET的有源箝位电路的工作原理

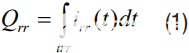

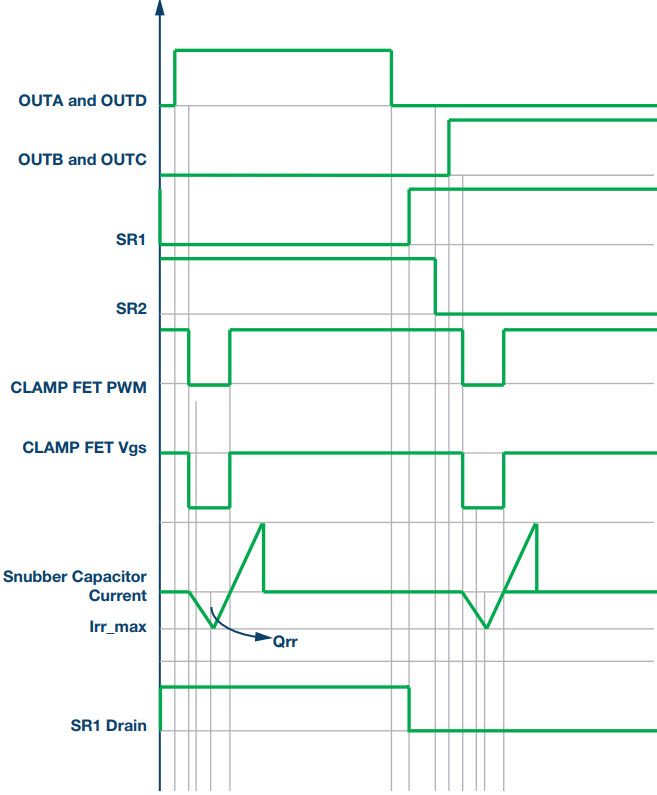

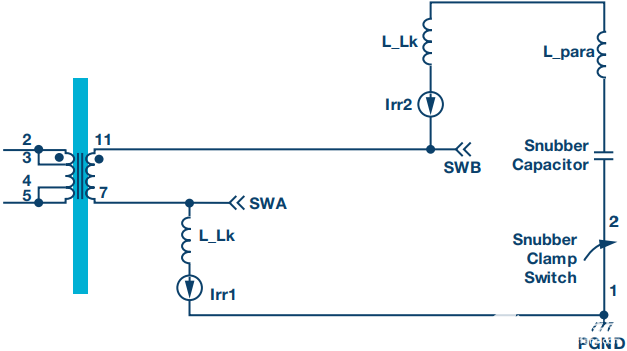

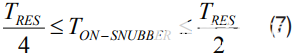

在分析中,假设缓冲电容器足够大,以保持其两端的恒定电压。在续流间隔期间(图 3 中 SR1 和 SR2 均导通),所有四个次级开关 (MOSFET) 均导通。由于上升和下降时间有限,以及栅极驱动信号传播延迟的变化,同步整流器信号之间总是存在很小的死区时间。在此死区时间内,MOSFET 的寄生体二极管导通以实现续流。在此之后是开关周期的下半部分,初级MOSFET的另一支路被点火。这会导致变压器绕组两端的极性发生变化,并关闭同步整流体二极管。但是,只要反向恢复电荷(QRR) 未耗尽。方向如图 2 所示。这个QRR被视为通过变压器反射到初级侧的过大电流,作为前沿尖峰。这也会导致同步 MOSFET 漏极端子上的电压尖峰。反向恢复费用的大小由下式给出:

图3.

图 4a.在TRR间隔期间操作反向恢复能量捕获。

图 4b.负载中释放的能量。

由漏电流和走线电感(极性如图2所示)引起的电压尖峰被有源箝位缓冲器吸收。主动缓冲开关可在 Z 轴时打开与寄生二极管导通后。但是,当有源箝位缓冲器导通时,缓冲器电容器吸收反向恢复电流,并将捕获的能量再循环到次级电桥和负载中。由于通过缓冲电容器的净电流为零,因此只要转换器在稳定状态下工作,它就会保持电荷平衡。

设计指南

1. 漏感的估算

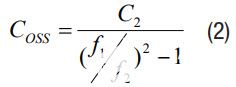

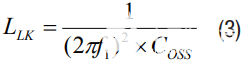

在没有缓冲器的情况下操作转换器并测量谐振频率和周期(f1) 同步 MOSFET 漏极上的振铃电压尖峰。此外,测量初级电流波形上的前沿尖峰(应等于tRR).要估算漏感,请放置电容器的已知值(C2) 至少比 MOSFET 的漏极源极电容大一个数量级。测量振铃频率(f2) 并计算电容 (C开放源码软件)和泄漏(L李克)电感使用以下公式计算:

2. 有源钳位缓冲电容器的选择

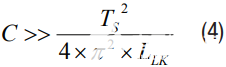

选择至少是同步 MOSFET 输出电容 10 至 100 倍的缓冲电容器。这是因为有源缓冲开关将有一个低阻抗路径。但是,缓冲电容器的选择必须符合:

其中 Ts是切换周期。

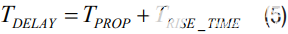

以如下所示的小延迟打开主动钳箍缓冲器:

这两个项是驱动器的传播延迟和初级MOSFET的驱动器信号上升时间。该时序至关重要,因为必须捕获MOSFET体二极管的整个反向恢复。这个时间取决于体二极管的反向恢复特性(QRR, tRR我RR),并可能随器件中的温度、负载电流和反向电压等因素而变化。定时延迟和缓冲导通时间可以针对开关的不同特性进行优化,使用上述精细分辨率设置。

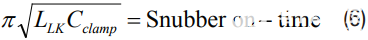

确定箝位电容尺寸的另一种方法是使用以下公式。它基于漏能量倾倒到箝位电容器中的谐振周期。

此值的范围为:

为避免在第 1 点观察到过多的振铃,导通时间应最多为一个或两个共振周期,否则会出现过度和连续的振铃。或者,缓冲器的导通时间可以近似于上述第 1 点中观察到的前缘尖峰的导通时间(例如 tRR).过长的时间只会导致能量再谐振几个周期,这可以从初级电流波形中看出(图8和图9)。

3. 缓冲开关选择

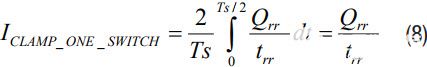

(1)的简化版本是从MOSFET的数据手册中获取最坏情况限值。以下公式提供了对电容器中电流的更多了解:

之所以使用因数 2,是因为只考虑了半个开关周期,对于全桥或半桥拓扑,此过程会发生两次。同样在图1中,由于两个开关关断,反向恢复电荷加倍。因此,总电流由下式给出:

其中 C 为 2 表示全桥配置;C 为 1 表示中心抽头变压器;N 是并联的 MOSFET 数量。这是通过有源缓冲开关的平均电流。

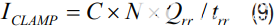

数字化实施

有源钳位缓冲器的数字实现有两个控件:控制1是缓冲器延迟(即缓冲器PWM边沿与触发边沿的可调延迟)。控制 2 是缓冲 PWM 导通时间。触发点是H桥相对支路(例如OUTC和OUTD)的主PWM上升沿的逻辑OR。缓冲 PWM 不需要像主 PWM 分辨率那样高的分辨率(例如 125 ps)。因此,触发所需的时钟速度相对较慢(5 ns分辨率),这也节省了功耗(40×因子)。该概念还可以应用于次级上有一个中心抽头的电源转换拓扑。此外,该概念还可以进一步应用于各个开关,其中分立式有源箝位开关缓冲单元放置在每个功率晶体管上。在这种情况下,有源箝位FET的驱动信号取自同步整流器的下降沿。

图5.缓冲PWM的数字实现。

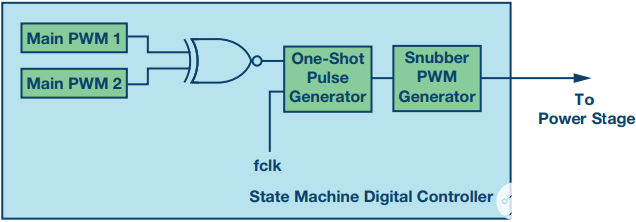

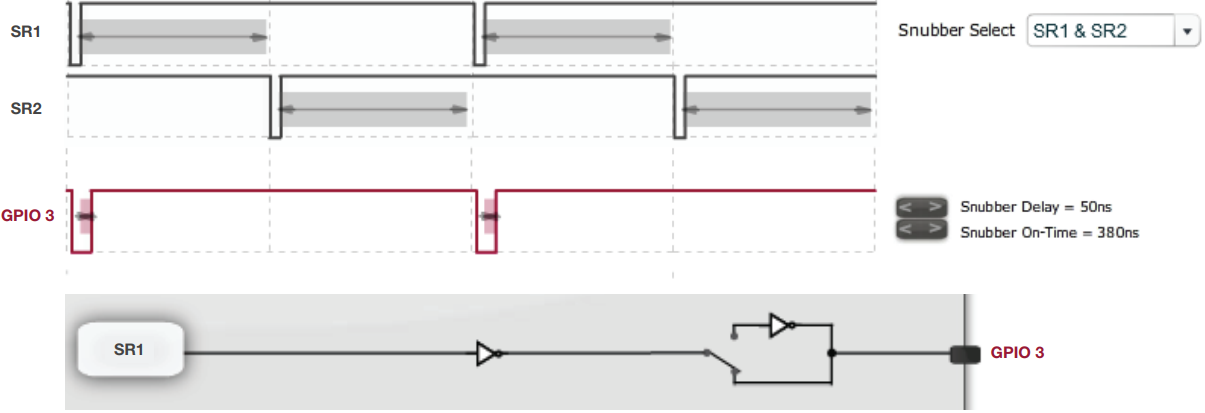

ADP1055数字控制器提供了一套合适的工具来实现这一点。通过直观的GUI,可以在几分钟内完成主动钳位缓冲器的优化。ADP1055提供两种选择,用于使用SR1和SR2或OUTC和OUTD信号的逻辑组合来设置缓冲器PWM。在这两种情况下,缓冲器PWM都可以配置两个选项,如图6和图7所示。在上述所有场景中,可以使用缓冲器延迟(设置死区时间)和缓冲器开启时间特征对优化参数进行微调。两个信号的逻辑组合与极性选择为用户提供了选择正确缓冲器的完全自由。

图6.使用选项 1 — SR1 和 SR2 的缓冲时序。

图7.使用选项 2 - OUTC 和 OUTD 缓冲时序。

全桥拓扑实验结果

为了进行实验验证,选择了一个隔离式DC-DC转换器,标称输入为48 V,额定输出为12 V、20 A,开关频率为125 kHz。拓扑是全桥式的,带有副边,如图1所示。

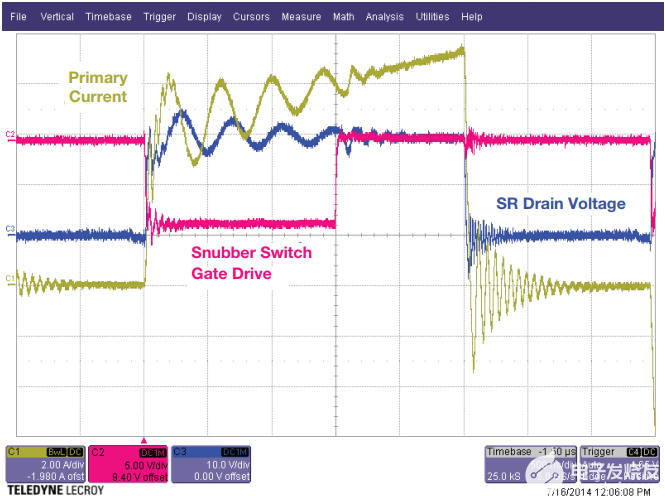

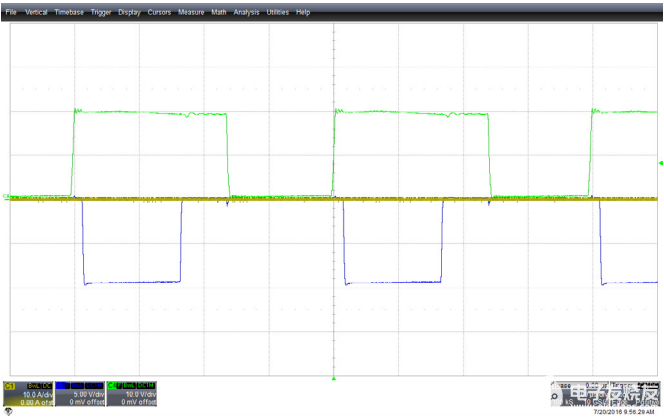

图8显示了不正确的导通时间缓冲器如何产生过多的振铃和同步MOSFET的振荡漏极电压,这也反映在初级电流中。前沿尖峰也很严重,会导致不必要的EMI。

图8.缓冲器的时间过长。

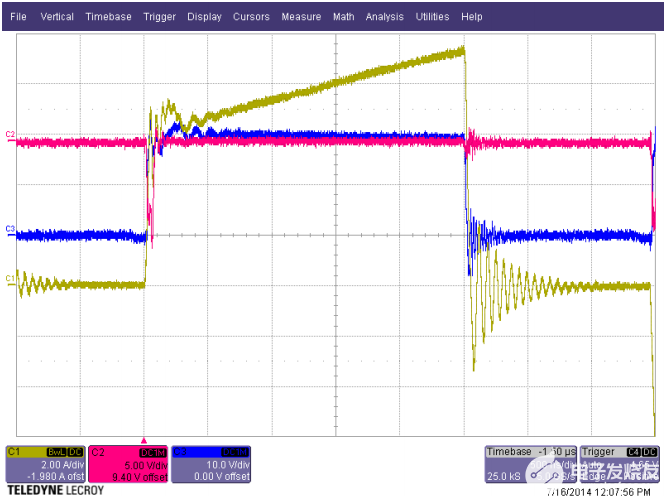

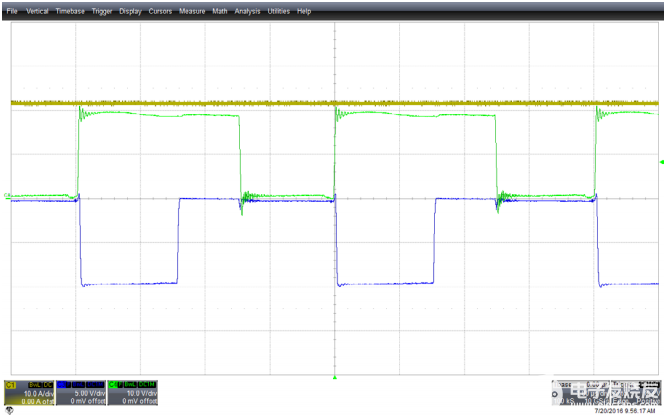

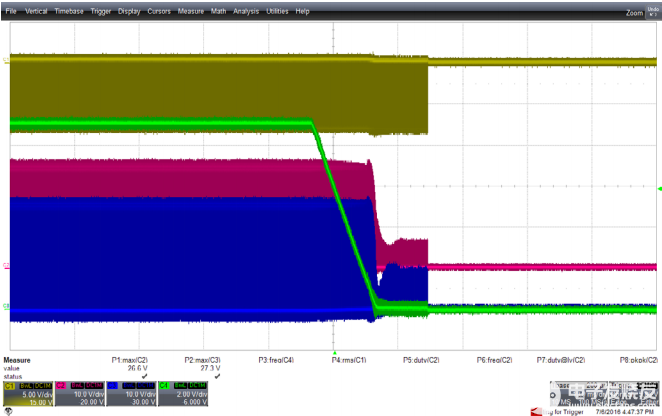

图9显示了一个优化的导通缓冲器,其中同步MOSFET的漏极电压没有振铃。此外,前沿尖峰也几乎被消除。

图9.优化缓冲器的时序。

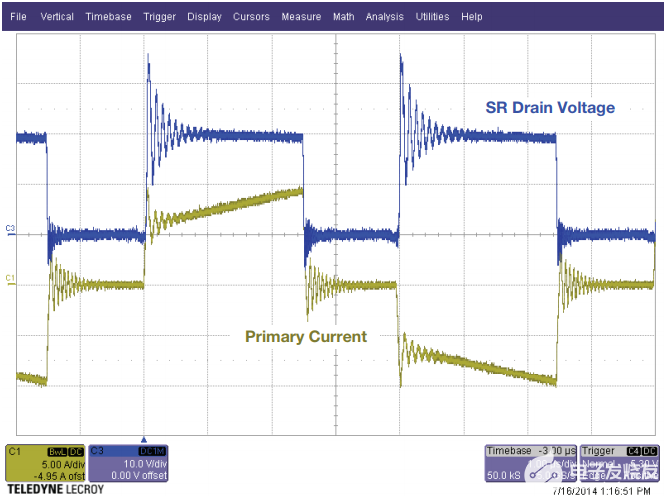

图10显示了没有有源箝位缓冲器的同步MOSFET的漏极电压。电压偏移可能高达稳态电压的 1.5 倍,MOSFET 有可能进入雪崩状态。

图 10.无主动钳式缓冲器。

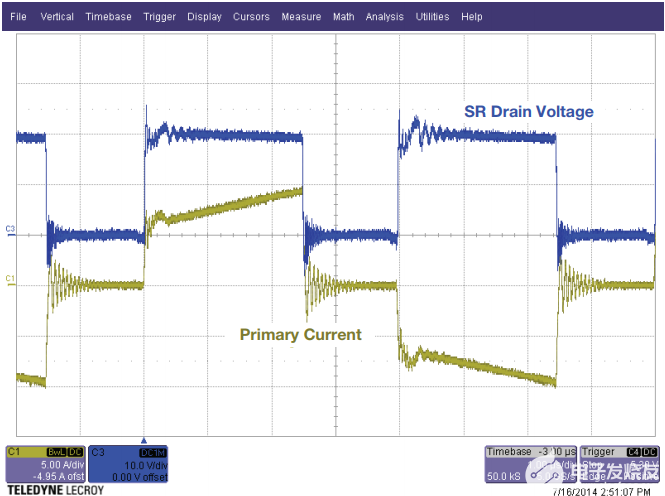

图11显示了有源钳位缓冲器的有效性。前沿尖峰被完全消除,MOSFET的漏极上没有振铃效应。

图 11.带主动夹紧缓冲器。

图 12.0 A 负载时的缓冲效果。

绿色迹线:SR 漏极,10 V/格

蓝色迹线:钳位 FET 栅源电压,5 V/格 黄色迹线:负载电流,10 A/格

图 13.缓冲器在 20 A 负载下的有效性。

绿色迹线:SR 漏极,10 V/格

蓝色迹线:钳位 FET 栅源电压,5 V/格 黄色迹线:负载电流,10 A/格

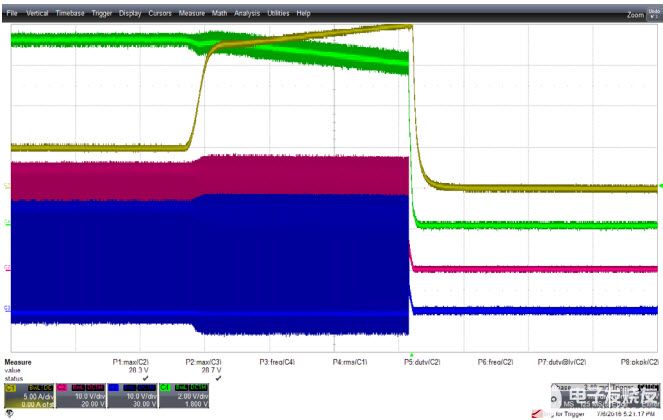

半桥拓扑实验结果

在标称输入为48 V、额定输出为9 V、200 W、开关频率为180 kHz的半桥拓扑上进行了额外的实验验证。

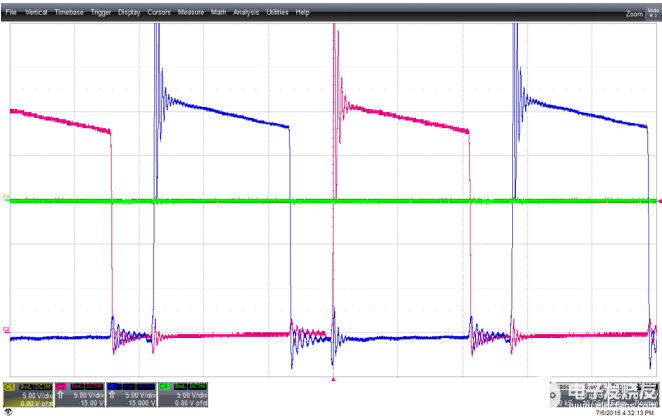

图 14.主动钳位缓冲器禁用。

红色迹线:SR1 漏极,5 V/div

蓝色迹线:SR2 漏极;5 V/div

绿色迹线:缓冲器 PWM,5 V/div

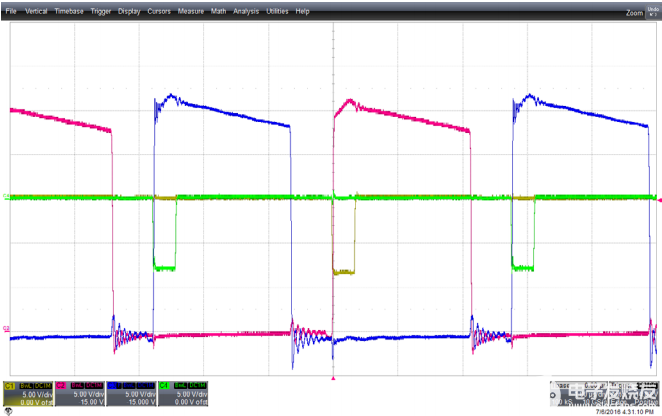

图 15.主动钳位缓冲器已启用。

红色迹线:SR1 漏极,5 V/格

蓝色迹线:SR2 漏极,5 V/格

绿色迹线:缓冲器 PWM,5 V/格

图 16.软启动期间的SR漏极波形,带有源箝位缓冲器。

黄色迹线:缓冲器 FET 栅源电压,5 V/格

红色迹线:SR1 漏极,10 V/格

蓝色迹线:SR2 漏极,10 V/格

绿色迹线:输出电压,2 V/格

图 17.软启动期间的SR漏极波形,带有源箝位缓冲器。

黄色迹线:缓冲器 FET 栅源电压,5 V/格

红色迹线:SR1 漏极,10 V/格

蓝色迹线:SR2 漏极,10 V/格

绿色迹线:输出电压,2 V/格

图 18.短路测试期间的 SR 漏极电压。

黄色迹线:负载电流,5 A/格

红色迹线:SR1 漏极,10 V/格

蓝色迹线:SR2 漏极,10 V/格

绿色迹线:输出电压,2 V/格

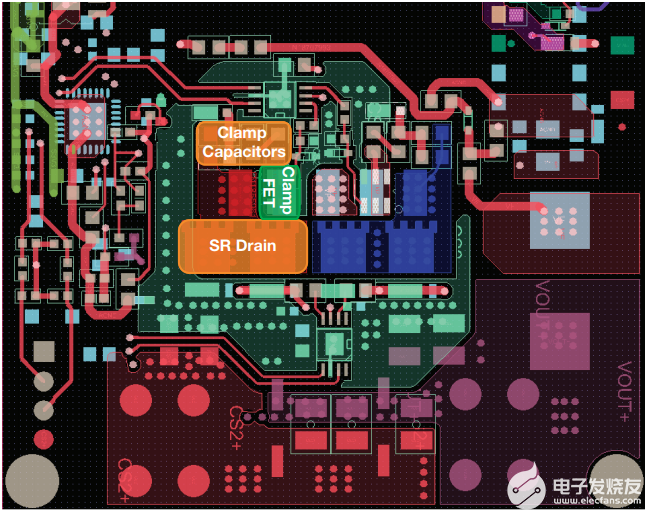

布局注意事项

图8显示了上述半桥拓扑的布局。关键要点是通过将环路缩短或收紧到狭窄区域来降低箝位环路的寄生电感。否则会降低夹具的有效性,导致钳夹期间的高频冲洗。

图 19.主动夹紧缓冲器的布局。

结论

本文展示了有源钳位缓冲电路的数字实现,用于隔离式DC-DC转换器中的高输出电流应用。所提出的有源箝位方案具有多种优点,例如较低的箝位电压导致较低的MOSFET击穿电压额定值,从而提高效率。它还消除了振铃,从而降低了电磁干扰 (EMI)。它是一种低成本和简单的电路,具有简单的驱动方案。与其他涉及额外电感器的有源缓冲器相比,它还节省了 PCB 板的成本.总体而言,电源的可靠性大大提高。此外,消除了前沿尖峰,从而减少了主开关上的应力。此外,更高的效率意味着更低的热量产生,这对于难以散热的受限区域中的模块非常有用。

ADP1055数字控制器提供一套合适的工具,无需使用复杂的编程或编码即可完成上述任务。ADP1055还支持许多其他功能,如黑匣子、软停止、命令屏蔽和非线性增益。

审核编辑:郭婷

-

MGDM-150系列高可靠性DC/DC转换器GAIA2025-07-29 3526

-

MGDM-155系列高可靠性DC-DC电源模块2026-01-28 1463

-

高可靠性与超宽环境温度的混合集成DC-DC变换器的设计2012-08-20 2623

-

dc模块电源的控制方法2018-07-28 3066

-

可实现高可靠性电源的半导体解决方案2018-10-17 2236

-

智能电源:模拟和数字控制回路实现对比2021-09-29 3896

-

如何选择用于电压转换的DC-DC模块电源?2022-06-13 7833

-

GAIA电源DC-DC转换器模块的正常工作温度及工业应用2020-08-11 2416

-

数字控制可实现具有有源缓冲功能的高可靠性DC-DC电源转换2023-04-23 2070

-

茂睿芯高压DCDC:高效率、高可靠性的DC-DC转换器2023-05-06 2932

-

为什么需要DC-DC模块电源?如何选择高可靠性的DC-DC模块电源?2023-08-17 4541

-

如何提升基于DC-DC模块的电源系统的可靠性?2023-11-17 1746

-

数字控制实现带有源缓冲高可靠性DC-DC功率转换2023-11-24 485

-

开关电源DC-DC电源应用设计原理2024-04-23 1528

-

设计基于TMS320F280x的数字控制DC-DC开关电源2024-10-16 573

全部0条评论

快来发表一下你的评论吧 !