低杂感模块封装内部是如何设计的

低杂感模块封装内部是如何设计的

电子说

描述

** 前 言 **

01

大家好,我们都知道无论是功率半导体模块封装设计还是功率变换器的母线设计,工程师们都在力求 杂散电感最小化 ,因为这样可以有效减小器件的 开关振荡及过压风险 ,今天我们结合主流功率半导体厂商的SiC MOSFET模块,聊一下低杂感模块封装内部是如何设计的?

** 杂感基本概念 **

02

首先我们先回顾一下电感的概念:电感是闭合回路的一种属性,是一个物理量。当线圈通过电流后,在线圈中形成磁场感应,感应磁场又会产生感应****电势 来抵制通过线圈中的电流变化,这种电流与线圈的相互作用关系称为电的感抗,也就是电感 ,以美国科学家约瑟夫·亨利命名,单位:H mH uH nH,数量级依次减小10^3倍。

对于常规的电感比较好理解,也比较形象,以空心螺线管为例,线圈通入电流就会在线圈内部产生磁通。如果从能量角度理解: 电感器是能够把电能转化为磁能而存储起来的元件,电感电流不能突变的本质原因是电流产生的磁场能不能突变 。通常情况下,线圈的形状不变后,电感也不再变化,默认为常数,电感与磁场中的磁链关系如下图:

普通电感的感量一般是uH或mH级,而杂散电感是指这个电感不是故意设计出来的,是附加或寄生在导体上产生的,量级一般是nH 级 , 任何一根导线无论它有多短都会存在寄生电感。

对于杂散电感理解虽不及螺线管形象,但电感与磁链的关系 依然满足L= Ѱ /I 。以矩形截面导体为例,杂散电感Lσ主要分为内电感Lin和外电感 Lext 。 其中,内电感Lin由导体内部的磁链Ψin引起,大小随频率的增加而减小,主要是因为高频下由于集肤效应电流都走表面,导体内部没有电流,也就不存在磁链了;外电感Lext由导体外部的磁链Ψext引起,由导体结构决定,与频率无关,高频状态下,电感主要表现为外电感 Lext 。

关于杂散电感与磁场能量的科普,可以参考老耿以前的文章:

** 杂感减小措施 **

03

通过电感与磁链或磁通的关系,不难发现 电感越大,单位电流产生的磁通量也就越多。反过来讲, 如果单位电流产生的磁通量越少,那导体的电感也就与越小( 这里是指不同形状的导体相比,对于一个导体,一旦形状固定,杂感基本就不会再变化了 )。 下面我们结合几种电流回路看一下导体形状和电流走向是如何影响杂感的。

电路1: 宽导体比窄导体杂感小 ,这个不难理解,可以把导体流过的电流想象成无数个并联的电流线,这样导体越宽,电流产生的磁通抵消也就越多,因此杂感也就越小。

电路2: 电流方向相反的两个叠层导体比平行导体杂感小 ,这个也很好理解,电流方向相反,上下电流产生的磁通就会抵消,因此杂感也就越小。

电路3: 换流回路中的电流方向相反的数量越多,能够抵消的磁通越多,杂感也就越小 。在这里可以把换流回路分段理解,电流相反的段数越多杂感也就越小。

电路4: 导体互连并联点越多杂感也就越小 ,这里的互连点可以是 电容并联 ,可以是 功率器件并联 ,也可以是 模块内部的芯片并联 。

电路5: 方向相反的电流距离越近,杂感也就越小。

通过上面分析可以看出,要想减小换流回路中的杂感, 核心思路要么是把导线做宽,要么就是导线叠层,且距离越近越好,但本质思想是一样的都是磁场抵消 。

下面让我们来看看两大主流的SiC MOS厂商Cree和Rohm模块内部是如何连接的。

** Cree 模块封装 **

04

**Cree公司的大功率****SiC MOS **模块主要有三种封装,分别如下:

示例1: 62 mm封装

下图为Cree 早期的62mm封装模块,这种封装目前在IGBT上还有大量应用。62mm模块的电压等级覆盖1200 V和1700V,1200V电压的模块电流从120A至530A,1700V模块只有225A一款, 该模块封装内部的杂感为11.1nH 。模块的内部结构如下图所示, 正负连接铜排在模块内部采用叠层方式 ,因此在一定程度上减小了模块杂感。

采用类似思想的模块非常多,例如primepack封装,详情可以参考这篇文章:

示例2 : **XM3 **封装

XM3 封装电压等级为1200 V,电流等级覆盖 400A-450A, 模块内部杂感为6.7nH 。

模块的内部结构如下图,可以看出 正负母线导体没有底层,但导体相对较宽 ,而且内部芯片并联, 电流的方向都是平行并联的,非常顺 ,这样杂感也能降下来。

示例3: HM High Performance 62 mm封装

HM 62mm 封装的电压等级覆盖1200 V和1700V,1200V电压模块电流从480A至760A,1700V电压模块电流从380A至650A,模块内部的杂感在4.9nH。

模块的内部结构如下图,正负母线在两侧,且没有叠层,但 正负母线比XM3封装更宽 ,这样可以进一步减小一部分杂感。

** Rohm 模块封装 **

05

Rohm sic模块电压等级覆盖1200V-1700V,模块封装主要有三种分别为: **C type、E ype和 G type** ,模块外形尺寸如下图:

其中C type****内部杂感为25n H , E type****内部杂感为13n H , G type****内部杂感为10n H 。E type和G type模块外部尺寸一样,但G type封装模块的电流更大。C type模块的内部结构如下图:

可以看出C type电流换流路径较长,而且上下桥MOS在两块独立的DCB上,因此杂感相对较大。E type模块的内部结构如下图:

可以看出E type封装比C type电流路径平行的段数变多了,因此杂感相比C type能够减小不少。G type封装老耿没有找到内部图片,猜测可能和E type差不多,只是内部并联的芯片数量会更多一些,因此电感相比E type会小一些。

-

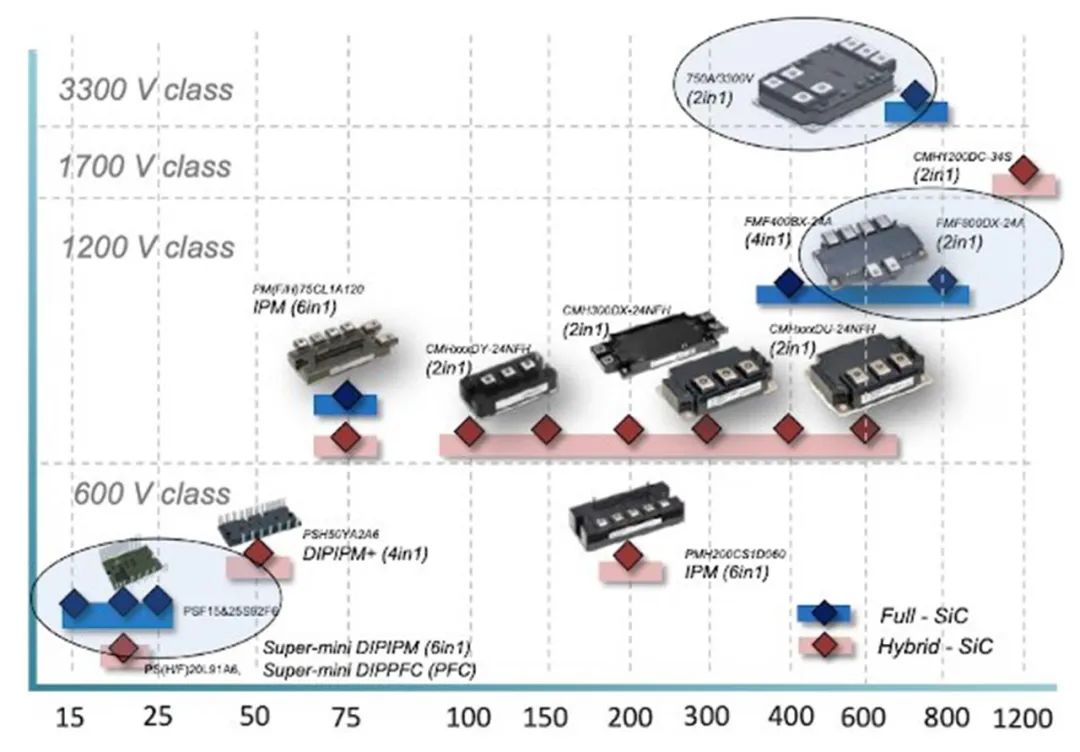

三菱电机高压SiC模块封装技术解析2025-02-12 1621

-

基于NX封装的低杂感SiC MOSFET模块设计2024-05-08 2173

-

IGBT模块封装工艺流程 IGBT封装技术的升级方向2023-12-29 3297

-

探究芯片封装:如何安全地拆开封装查看内部2023-09-15 3917

-

光模块内部的组成和工作原理2023-09-12 13635

-

SSD内部封装解密#工作原理大揭秘jf_24750660 2022-10-19

-

变频电源内部IGBT模块的作用是什么样的2022-01-06 2292

-

变频电源内部IGBT模块的作用是什么2021-12-28 6557

-

创新的IGBT内部封装技术2010-05-11 3326

-

五年单片机学习之旅杂感2010-03-31 543

-

设计模块的低有效接口电路2009-11-21 803

-

安森美推出低厚度SOD-123FL封装2008-09-01 4871

-

芯片封装内部结构2008-06-11 92280

全部0条评论

快来发表一下你的评论吧 !