SystemVerilog中至关重要的结构体和自定义类型

电子说

描述

在上一篇文章《SystemVerilog中至关重要的的数据类型》中,介绍了枚举类型的本质和使用语法。本文接着介绍SV中同样不可忽略的结构体(structure)和自定义类型(typedef),最后也会给出一小段涵盖绝大部分语法点的例程。个人觉得编程语言的熟练掌握更多在平时练习和思考,语法忘掉了随时可以查阅。

认识结构体

结构体(structure)是一种可以包含不同数据类型元素的集合类型。这一点跟数组、队列等集合类型是不一样的,数组和队列只能包含相同数据类型的元素。结构体在引用的时候,可以对这些元素进行整体引用,也可以通过元素名称来对元素进行单独引用。

基于这个特性,结构体通常可以用来表征一个包含了诸多不同类型属性的对象。比如,当我们想要表征一个人的所有属性的时候,名字元素可以用string类型,年龄元素可以用int类型,存款元素可以用real类型等等,最后可以通过对整体引用来获得一个人的所有属性,也可以通过元素名称来获得单个属性。

另一个栗子,可以使用结构体来定义某个寄存器的结构。在结构体类型定义的时候,我们可以在内部使用logic [n:m]等基本数据类型来定义寄存器的不同域段。这样一来,我们不但可以对寄存器进行整体引用,又可以使用元素名来很方便地读写寄存器的各个域段。

讲完结构体的逻辑结构,下面来看看结构体的物理结构。

在内存存储一个结构体的时候,SV提供了packed关键字用来区分合并(packed)和非合并(unpacked)存储方式。“合并”这个概念在另一篇文章中也有涉及。合并的结构体,其元素会被无间隙的存放到一块连续的内存空间上。而非合并的结构体,其物理结构一般依赖于C编译器。SV默认是非合并的,这是为了提高内存空间的利用率,如果用户想要用合并的,需要在struct关键字后面加上packed。

合并的结构体是有不少用处的。第一,合并结构体的整体可以被当成一个向量来看待,这样一来,合并结构体的赋值、读取和数值计算上多了灵活性;第二,合并结构体可以通过在packed关键字后面加signed/unsigned来指定为有无符号类型,排在第一个位置的元素最高位为符号位,相比之下,非合并的结构体是不能被指定为有符号类型的。

结构体的使用

SV结构体的特性跟C语言基本一致,但在语法上有差别。比如在C语言中,定义一个结构体类型,是在struct关键字后面加上structure tag名来作为类型名称;而在SV中,统一使用typedef来定义结构体类型名称。

这里穿插介绍一下typedef。typedef是SV中提供用来重定义类型名的关键字,一般也叫做用户自定义类型。其最大的好处就是可以将一些“又臭又长”的类型定义成简短的类型名,特别是在一些复杂的testbench中会经常遇到。使用typedef可以提高编程效率,也可以通过新的类型名来提高代码的可读性。

看看代码吧

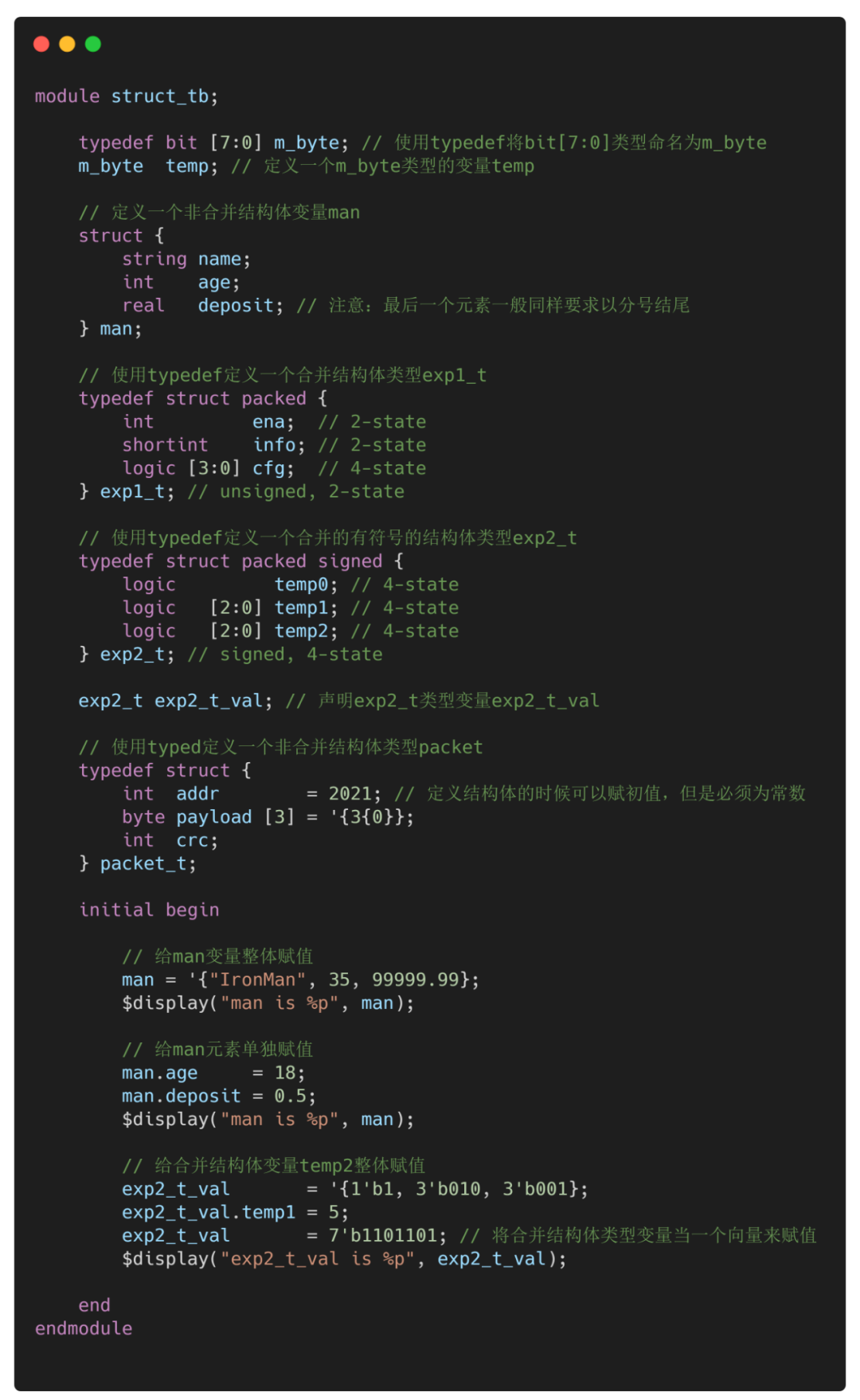

下面代码和注释总结了结构体的使用方法,个人觉得掌握例程中的内容对工作来说已经完全足够啦,但例程同样没有经过编译哈。

参考文献

[1] IEEE Standard Association. "IEEE Standard for SystemVerilog-Unified Hardware Design, Specification, and Verification Language." (2013).

-

自定义视图组件教程案例2022-04-08 996

-

LabVIEW自定义控件2015-01-07 28404

-

LabVIEW自定义数据类型2017-03-24 9018

-

用户自定义结构数据怎么存储成VARIANT类型2019-08-02 1851

-

请问自定义结构体中u16 RESERVEDi起什么作用?2020-08-24 2233

-

嵌入式ARM开发之自定义数据类型相关资料推荐2021-12-14 884

-

SOPC中自定义外设和自定义指令性能分析2009-03-29 1916

-

1602自定义字符2016-01-20 973

-

C++程序设计教程之自定义数据类型的详细资料说明2019-03-14 1264

-

浅析Zephyr应用的代码结构中的自定义驱动2021-08-18 6933

-

SystemVerilog中至关重要的的数据类型2023-01-21 1515

-

用户自定义类型2023-02-09 1977

-

博途PLC1200/1500PLC用户自定义数据类型(UDT)2023-04-20 1227

-

labview超快自定义控件制作和普通自定义控件制作2023-08-21 1055

-

如何在Matlab中自定义Message2023-11-15 2778

全部0条评论

快来发表一下你的评论吧 !