PCB板如何赢在层叠设计呢?

PCB设计

描述

我们先来看看这几个问题:

1,你有没有过通过选择不同的板材满足不同产品的性能要求?

2,你有没有通过调整层叠pp和core的厚度来实现电源地平面的紧耦合或者说加大相邻层(信号相邻层或者电源相邻层)的间距?

3,你有没有过隔层参考来控制射频走线的阻抗

4,你有没有过通过改变层叠来调整线宽线距从而更好的控制串扰和损耗问题

5,你有没有过通过层叠规划和高速信号布线层规划来实现信号stub最短?

6,在原理图设计完成时,你有没有做过层叠设计并且和制板厂商进行有效沟通和确认?

7,你有没有通过层叠来试图减少设计中的SI,PI,EMC问题?

接着我们来看看如下表:

机械参数会对中间一栏的电气参数产生影响或者互相影响,从而导致右边一系列信号完整性、电源分布和EMC问题,而机械参数中很多都和层叠设计相关。从以上我们就知道:层叠设计非常重要!!! 那如何赢在层叠设计,我们要从哪些方面入手?

- 第一点:层叠的构造——材料 首先我们来看看PCB板材的基本组成部分。

这里说的材料就是我们常说的PCB板材,要想赢在层叠设计,首先你要知道层叠是怎么组成的,由哪些材料组成,材料的常见品牌,常见型号,常见厚度有哪些?主要与设计相关的参数有哪些等,知道了这些,才能进行层叠的堆叠和设计。

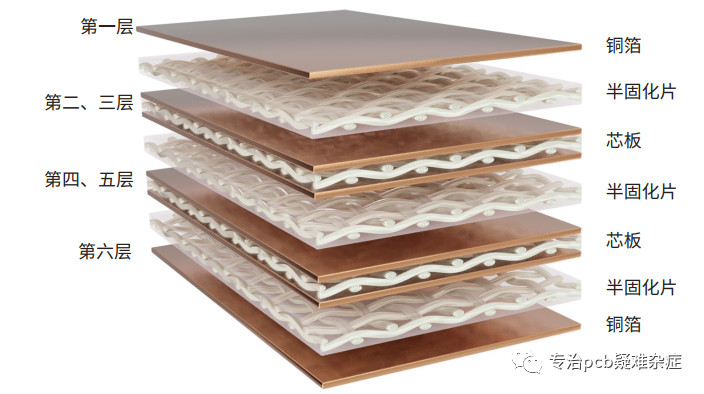

多层PCB层叠主要组成部分是铜箔、芯板和半固化片。芯板,有时也被称为层压板或覆铜层压板(CCL),通常由固化树脂制成, 结合玻璃纤维材料,并在两面都覆盖有铜箔。叠层中芯板与半固化片交替出现,半固化片充当胶水,在层压后将叠层固定在一起。“半固化片”是“树脂半固化片”的简写。在层压过程中,热量和压力会使树脂半固化片流入相邻铜箔之间的间隙,从而导致由其固定的铜层之间的半固化片厚度减小。

PCB 中半固化片和芯板不导电介电层中包含树脂和玻璃纤维两种材料的组合。树脂提供介电功能的同时还充当粘合剂的角色以粘附到铜箔上,而玻璃纤维负责增强结构强度, 就像混凝土中的钢筋。单独的树脂很坚硬, 但没有弹性。添加玻璃纤维能够加强结构并为树脂提供了弹性的可供粘附的表面。

接着我们来看看材料的特性。主要从三个方面:热参数,电气参数,机械参数

热参数我们主要关注的还是:TG值 TD值以及CTE

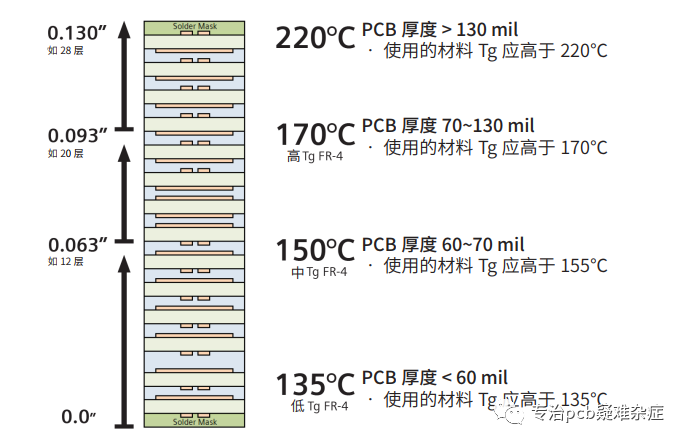

我们知道PCB 在组装和返工期间会被加热数次,较厚的设计对焊接温度更敏感,因为Z 向应力会不断叠加,并且可能失效的点更多。我们知道选择板材时会突出一个参数,就是TG值,较厚的电路板需要较高的 Tg 值。原因是层压板(和叠层) 的 z 轴热膨胀在高于玻璃化转变温度时急剧上升。根据Tg 选择材料的一般经验法还应考虑其他热特性, 包括从 50℃ 到 260℃ 的 z 轴膨胀和分解温度(Td)。

我们知道随着层数和电路板厚度的增加,热应力会累积,导通孔孔壁镀层所承受的应力越大,并且会提高在树脂和铜边界处分层的风险。这里我们一般是建议8层或8层以上选择高TG板材,4-6层选择中TG板材,常规简单的2-4层可以选择低TG板材。也可以从厚度上进行对板材的TG值进行选择,当然这只是一个建议 并非规范。

另一个常用参数是分解温度(Td), 这个参数需要通过热重分(TGA) 来测量重量损耗 5% 时的温度。事实上,一切层压板的分解都是不可逆的, 并可能导致多种失效模式,包括常被称为“分层”的情况。当超过 Td 时,化学键的断裂会导致材料的不可逆分解和损坏,从而导致严重的分层风险。而热膨胀系数CTE指的是材料随着温度的升高而膨胀的程度CTE 在高温和电路板温度在高低值之间反复循环时都很重要。

在循环过程中,电路板会膨胀和收缩,从而对铜元件施加压力,并且当基板和铜 CTE 值之间的失配较大时,该应力会更大。导体和基板材料的 CTE 值应尽可能匹配。

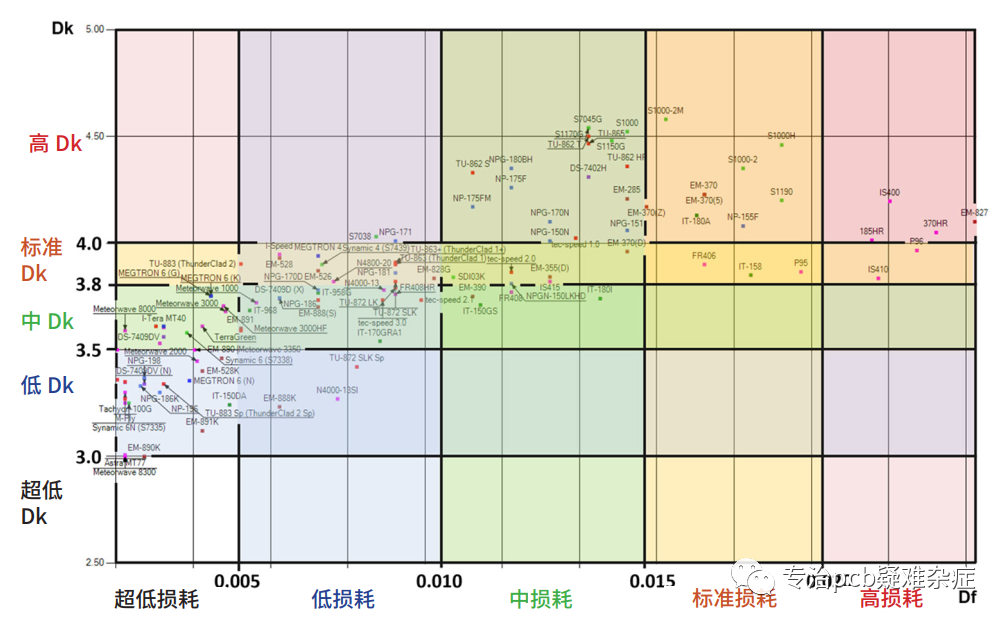

电气参数我们关注的是:介电常数 Dk、介电损耗 Df

Dk 表示材料相对于真空的电容值,是阻抗关系中的分母。典型玻纤布环氧树脂体系的Dk 值范围为 2.9 至 4.5。Dk 随频率和树脂含量的提高而降低。Df 参数表示高速信号加热周围电介质而损耗的相对能量。Df 值的范围从超低损耗层压板的0.001 到高损耗层压板的大于 0.020 都有。一般来说,介电常数和介电损耗越低越好,同时也会更昂贵。

下图是180种材料对应的图

机械参数材料多少一般因制造商而异。这一点体现在材料规格书上。有些制造商提供的机械参数包括剥离强度、弯曲强度、吸湿性、导热性、杨氏模量和泊松比。决定哪些值对您的设计很重要的因素将取决于场景。弯曲强度、杨氏模量和剥离强度是材料在各种测试条件下的强度测量值。大多数材料规格书至少会包括剥离强度和吸水率。

- 第二点:层叠的重点——阻抗

随着信号传输速度的迅猛提高以及高频电路的广泛应用,对印刷电路板也提出了更高的要求。要得到完整、可靠、精确、无干扰、无噪音的传输信号。就必须保证印刷电路板提供的电路性能保证信号在传输过程中不发生反射现象,信号完整,传输损耗低,起到匹配阻抗的作用。为了使信号,低失真、低干扰、低串音及消除电磁干扰 EMI。阻抗设计在 PCB 设计中显得越来越重要。

那阻抗跟什么有关?我们可以先看下如下图

我们的层叠设计绝大部分是需要满足阻抗要求的。关于层叠的重点——阻抗设计和计算,杨老师会在后面的内容中讲到。

- 第三点:层叠的难点——设计

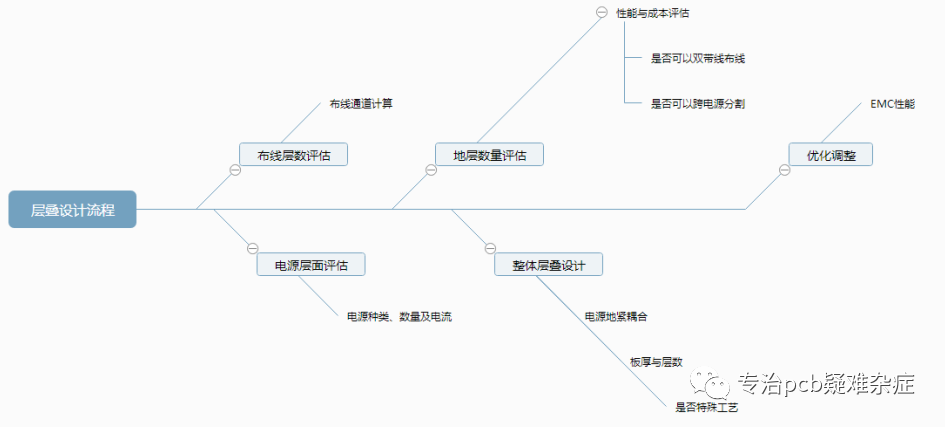

我们先来看看设计流程

层叠设计是一个复杂的过程,不仅仅只是一篇文章就能说清晰。关于层叠设计,这里有几个重点:

1,叠层设计会影响PCB 上的每个信号。

2,制造的物理世界与您的设计中的电气完整性不断在发生冲突。 所以和工厂要保持不断地联系和有效沟通。

3,如果您的设计遇到信号完整性问题,它几乎总是与您输入到信号完整性仿真中的叠层或叠层参数有关。

4,研发人员需要将详细的叠层和材料决策左移到设计过程的早期阶段。

审核编辑:刘清

-

PCB 设计规则、层叠结构的导入/导出2024-12-17 4226

-

PCB层叠设计是什么?又有什么样的作用?2023-12-21 1854

-

PCB板层叠结构介绍2023-02-18 5648

-

PCB层叠设计需考虑的因素和规则2020-11-03 3550

-

PCB层叠设计的六大要点2020-07-19 2681

-

PCB层叠设计需考虑的因素_PCB层叠设计的一般规则2020-03-21 3864

-

PCB层叠的认识2020-03-16 4367

-

PCB层叠设计解读2020-03-13 7827

-

多层PCB板的层叠的设计步骤解析2020-01-02 6114

-

多层PCB板的层叠结构以及叠加原则解析2019-10-04 9694

-

层PCB板的层叠结构2015-02-11 8026

-

平衡PCB层叠设计的方法2012-08-09 4265

-

平衡PCB层叠设计方法2009-09-08 537

全部0条评论

快来发表一下你的评论吧 !