分频电路设计和仿真

描述

1、偶数分频

- 方法

直接使用计数器实现,在计数一半时将时钟翻转即可;

- 4 分频示例

1module clk_div_even

2#(

3 parameter DIV = 4

4)

5(

6 input clk,

7 input rstn,

8 output reg clko

9);

10

11reg [DIV/2-1:0] cnt;

12

13always @(posedge clk or negedge rstn)

14begin

15 if(!rstn) begin

16 cnt <= 0;

17 clko <= 0;

18 end else begin

19 if(cnt == (DIV/2 - 1)) begin

20 clko <= ~clko;

21 cnt <= 0;

22 end else begin

23 cnt <= cnt + 1;

24 end

25 end

26end

27

28endmodule

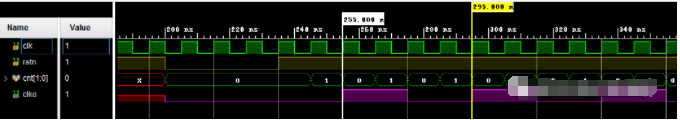

- 仿真波形:

2、奇数分频

- 非 50% 占空比

使用计数器,当计数到一半时候进行翻转时钟,当计数到分频值时候再次翻转;

1module clk_div_odd1

2#(

3 parameter DIV = 5

4)

5(

6 input clk,

7 input rstn,

8 output reg clko

9);

10

11reg [DIV-1:0] cnt;

12

13always @(posedge clk or negedge rstn)

14begin

15 if(!rstn) begin

16 cnt <= 0;

17 end else begin

18 if(cnt == (DIV-1)) begin

19 cnt <= 0;

20 end

21 else begin

22 cnt <= cnt + 1;

23 end

24 end

25end

26

27always @(posedge clk or negedge rstn)

28begin

29 if(!rstn) begin

30 clko <= 1'b0;

31 end else begin

32 if(cnt == (DIV-1)/2) begin

33 clko <= ~clko;

34 end

35 else if(cnt == (DIV -1)) begin

36 clko <= ~clko;

37 end

38 else begin

39 clko <= clko;

40 end

41 end

42end

43

44endmodule

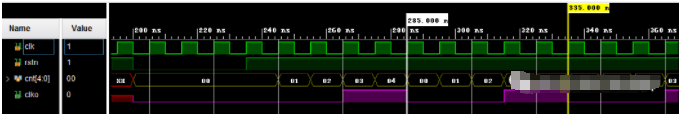

仿真波形:

- 50% 占空比

上升沿和下降沿分别做分频,将结果进行或操作即可;

1module clk_div_odd2

2#(

3 parameter DIV = 5

4)

5(

6 input clk,

7 input rstn,

8 output clko

9);

10

11//posedge clk

12reg [DIV-1:0] pos_cnt;

13reg pos_clk;

14

15always @(posedge clk or negedge rstn)

16begin

17 if(!rstn) begin

18 pos_cnt <= 0;

19 end else begin

20 if(pos_cnt == (DIV-1)) begin

21 pos_cnt <= 0;

22 end else begin

23 pos_cnt <= pos_cnt + 1;

24 end

25 end

26end

27

28always @(posedge clk or negedge rstn)

29begin

30 if(!rstn) begin

31 pos_clk <= 0;

32 end else begin

33 if(pos_cnt == (DIV-1)/2) begin

34 pos_clk <= ~pos_clk;

35 end

36 else if(pos_cnt == (DIV-1)) begin

37 pos_clk <= ~pos_clk;

38 end

39 else begin

40 pos_clk <= pos_clk;

41 end

42 end

43end

44

45//negedge clk

46reg [DIV-1:0] neg_cnt;

47reg neg_clk;

48

49always @(negedge clk or negedge rstn)

50begin

51 if(!rstn) begin

52 neg_cnt <= 0;

53 end else begin

54 if(neg_cnt == (DIV-1)) begin

55 neg_cnt <= 0;

56 end else begin

57 neg_cnt <= neg_cnt + 1;

58 end

59 end

60end

61

62always @(negedge clk or negedge rstn)

63begin

64 if(!rstn) begin

65 neg_clk <= 0;

66 end else begin

67 if(neg_cnt == (DIV-1)/2) begin

68 neg_clk <= ~neg_clk;

69 end

70 else if(neg_cnt == (DIV-1)) begin

71 neg_clk <= ~neg_clk;

72 end

73 else begin

74 neg_clk <= neg_clk;

75 end

76 end

77end

78

79//clk output

80assign clko = pos_clk | neg_clk;

81

82endmodule

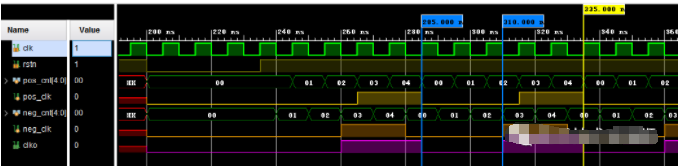

仿真波形:

3、小数分频

以设计2.6分频为例;

- 方法:

(1)将小数取分数形式,即 2.6 = 13/5;

(2)因为2.6在2~3之间,因此可以使用2分频和3分频组合实现;

(3)由如下方程进行设计:

1x + y = 5

22x + 3y = 13

求得 x = 2, y = 3 , 即使用2个2分频和3个3分频时钟实现2.6分频;

(4)设计总计数器,范围为 013 计数,那么在 04范围内进行2分频的计数,在5~13范围内进行3分频的计数,然后根据计数生成需要的时钟;

(5)

- Verilog实现:

1//clk divider: 2.5 , M/N = 13/5

2module clk_div_mn

3#(

4 parameter M = 13,

5 parameter N = 5

6)

7(

8 input clk,

9 input rstn,

10 output reg clko

11);

12

13parameter DIV_M = 2;

14parameter DIV_N = 3;

15

16reg [3:0] cnt;

17always @(posedge clk or negedge rstn)

18begin

19 if(!rstn) begin

20 cnt <= 0;

21 end else begin

22 if(cnt == (M-1)) begin

23 cnt <= 0;

24 end else begin

25 cnt <= cnt + 1;

26 end

27 end

28end

29

30reg [3:0] cnt2;

31reg [3:0] cnt3;

32

33parameter CHANGE = 4;

34

35always @(posedge clk or negedge rstn)

36begin

37 if(!rstn) begin

38 cnt2 <= 0;

39 cnt3 <= 0;

40 end else begin

41 if(cnt <= (CHANGE-1)) begin

42 cnt3 <= 0;

43 if(cnt2 == (DIV_M-1)) begin

44 cnt2 <= 0;

45 end else begin

46 cnt2 <= cnt2 + 1;

47 end

48 end

49 else if(cnt > (CHANGE -1)) begin

50 cnt2 <= 0;

51 if(cnt3 == (DIV_N -1)) begin

52 cnt3 <= 0;

53 end else begin

54 cnt3 <= cnt3 + 1;

55 end

56 end

57 end

58end

59

60always @(posedge clk or negedge rstn)

61begin

62 if(!rstn) begin

63 clko <= 0;

64 end else begin

65 if(cnt < CHANGE) begin

66 if(cnt2 == 0 || cnt2 == DIV_M/2) begin

67 clko <= ~clko;

68 end

69 else begin

70 clko <= clko;

71 end

72 end

73 else begin

74 if(cnt3 == 0 || cnt3 == (DIV_N-1)/2) begin

75 clko <= ~clko;

76 end

77 else begin

78 clko <= clko;

79 end

80 end

81 end

82end

83

84endmodule

- 仿真波形:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

源三分频电路设计2009-06-22 9838

-

CPLD epm7128时钟电路,分频电路设计2013-03-11 2802

-

下载:《ADS应用详解-射频电路设计与仿真》2017-10-17 34182

-

基于LabVIEW的数字电路设计和仿真2010-03-30 1133

-

FPGA实现小数分频器2011-11-29 817

-

ADS2008射频电路设计与仿真实例2013-09-13 4447

-

电路设计与仿真技术2016-04-29 791

-

Multisim电路设计与仿真2016-05-13 1692

-

Protel99SE电路设计与仿真2017-01-12 1286

-

数字家庭网关射频滤波电路设计与仿真2017-01-24 1127

-

乘法器电路设计方案汇总(五款模拟电路设计原理及仿真程序分享)2018-01-17 63466

-

电子分频器电路图大全(六款电子分频器电路设计原理图详解)2018-03-02 146172

-

浅谈FPGA设计中分频电路设计2020-07-10 2905

-

基于PSpice的光电放大电路设计和仿真2021-05-27 1276

-

射频PCB电路设计与仿真案例2023-08-09 4681

全部0条评论

快来发表一下你的评论吧 !