铁电存储器的优势和发展趋势分析

存储技术

描述

在前面一篇文章《为什么FeFET变得如此有趣?》中考虑了使用铁电体来改善逻辑晶体管的亚阈值摆动行为。铁电体在逻辑应用中的前景不明朗,但铁电体存储器具有明显的优势。

两种最常见的商业存储器位于频谱的两端。DRAM 速度很快,但需要持续供电来维持其信息。闪存是非易失性的,对于长期大容量存储来说足够稳定,但速度不是特别快。铁电存储器介于两者之间,并可能提供必要的中间步骤。

改变铁电畴的极化速度非常快,即使没有几十年,极化在没有电源的情况下也能保持稳定。随着系统设计人员寻求操纵越来越大的数据集,同时降低功耗,铁电存储器可能成为解决方案的一部分。

但具体是哪种铁电存储器尚不清楚。该术语实际上包含至少三种不同的技术。它们都取决于铁电材料的极化行为,但它们以不同的方式利用这些材料。虽然它们在结构上相似,但它们依赖于不同的物理学并且具有不同的材料要求。适用于一种设计的铁电体可能完全不适用于其他设计。

FeRAM

最简单的铁电存储器设计,FeRAM,将金属/铁电/金属电容器集成到 BEOL 工艺中,在每个单元下方放置一个传统的 MOSFET。为了存储数据,电场在 P- 和 P+ 极化状态之间切换电容器。不幸的是,读取极化值是一种破坏性操作,之后必须重写单元,正如罗彻斯特理工学院的 Shan Deng 及其同事在 2021 年 GLSVLSI 会议上介绍的工作中所解释的那样。因此,商业 FeRAM 应用需要异常高的耐久性,高于 10 4周期。

基于掺锆 HfO 2电容器的存储器很有吸引力,因为它们与现有的 CMOS 制造工艺兼容,但设计集成仍然具有挑战性。为了逻辑兼容性,设计人员希望将写入电压降低到 1.5V 以下。然而,可靠的写入操作需要比改变铁电极化所需的矫顽磁场 (Ec)大两倍或三倍的电场。

Deng 解释说,理想的 FeRAM 材料的 Ec约为0.5 MV/cm。氧化铪具有 1 至 1.5 MV/cm 之间的矫顽场,因此需要更高的写入电压。同时,FeRAM 检测余量与材料中的剩余极化成正比。目前还没有具有高剩余极化和低 E c的材料。

铁电开关所需的高场也会影响设备的长期可靠性。在沉积过程中,界面层——据信是金属氧化物——在铁电体和金属电容器板之间形成。它似乎可以钝化两种材料并促进界面处的粘合。根据 TU Dresden 的 Ruben Alcala 及其同事在 12 月的 IEEE 电子设备会议上发表的工作,开关场和铁电偶极子本身都会使该界面层退化,从而影响极化保持和循环耐久性。随着残余极化随着重复循环而减少,感测裕度恶化。随着时间的推移,带电的氧空位会在铁电材料中建立内部电场。该场“印记”记忆,因此首选一种偏振状态。为了克服印记,成功切换所需的峰值场增加。

铁电隧道结

第二种类型的铁电存储器,铁电隧道结,使用极化来调制结的隧道势垒,从而调制它的电阻。据邓说,减少铁电层的厚度会增加隧道概率,但也会降低开/关电流比。增加极化电荷有助于增加导通电流并提高开/关比。

在 FeRAM 中,去极化场的存在是不可取的,会缩短保留时间。然而,在 FTJ 中,需要去极化场以确保“开”和“关”状态具有不同的势垒高度。

FeFET 存储器

铁电存储器的第三种方法是基于铁电晶体管(FeFET)。FeFET 将铁电体与传统电介质串联放置,中间有或没有金属层。阈值电压取决于铁电体的极化状态。内存窗口是 V tlo和 V thi值之间的差异。

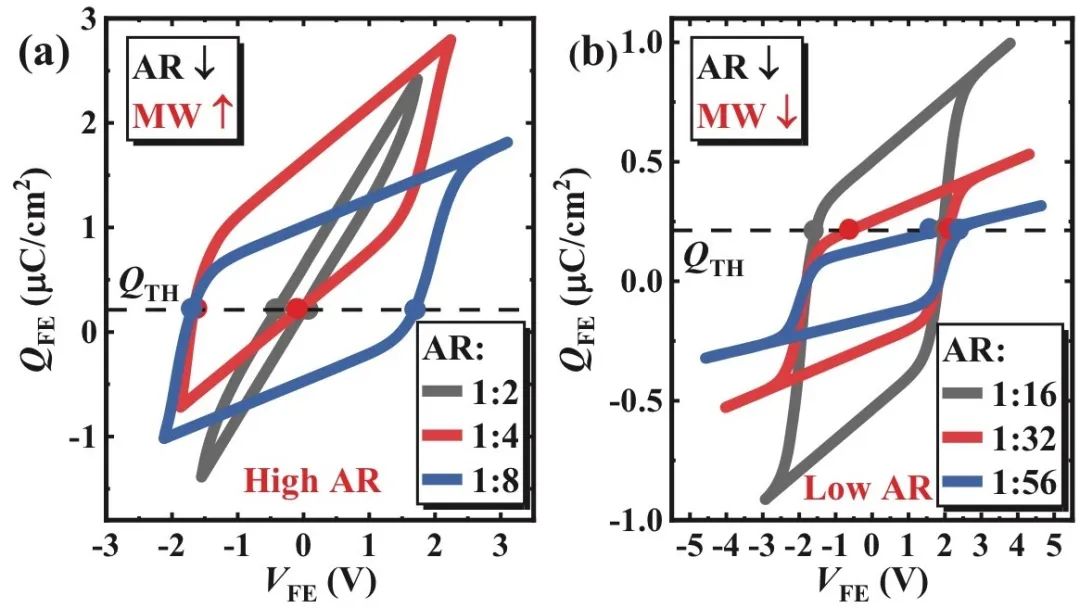

研究人员展示了两种可能的器件结构——金属/铁电/金属/绝缘体/半导体 (MFMIS) 和金属/铁电/绝缘体/半导体 (MFIS)。根据新加坡大学 Xiaolin Wang 及其同事在 IEDM上的报告,在这两种情况下,面积比 A FE / A MOS都是一个关键参数。随着这个比率的下降——例如,如果铁电面积减少而 MOS 面积保持不变——存储窗口会增加。

图1:FeFET 存储器中的存储器窗口与面积比。

资料来源:新加坡大学/IEDM

在结构上,FeFET 存储器类似于铁电逻辑晶体管。在这两种应用中,铁电体极化状态之间的切换会导致传递到底层 MOSFET 的电压突然出现尖峰。FeFET 逻辑器件依靠这种“负电容”瞬变来实现陡峭的亚阈值摆幅,因此通常被描述为 NCFET。

不幸的是,与铁电开关相关的电压尖峰也会引起缺陷和电荷俘获。如上所述,在 FeRAM 中,高剩余极化是可取的,因为它增加了感测裕度。然而,在 FeFET 存储器中,不完全切换会导致器件阈值电压发生变化,需要更大的脉冲才能确保写入成功。据邓说,减少 FeFET 存储器中的残余极化可以降低压力。

随着商业 FeFET 存储器潜在市场的出现,研究人员需要更详细地分析陷阱、缺陷生成和器件可靠性。根据北京大学 Puyang Cai 及其同事的说法,两种主要的降解机制似乎与Vtlo的增加有关。一方面,增加 V tlo会减小 V tlo和 V thi之间的差异,从而减小内存窗口。增加Vtlo还会引入“写入后读取”延迟——定义为成功写入后到可以读取内存值之前的延迟——因为导通电阻增加。

Puyang Cai 的团队确定了两种不同的潜在诱捕机制。A型陷阱出现在通道附近的界面层,先增加然后稳定。他们似乎负责写入延迟后读取。HZO 层内的 B 型陷阱似乎不断增加,并且与内存窗口退化有关。北京大学的第二个小组在周悦佳及其同事报告的工作中表明,金属/铁电夹层中的电场密度在缺陷产生中起着关键作用。高层间场似乎会在铁电体中产生陷阱。TSMC 的研究人员特别指出铁电体中的氧空位会导致泄漏和铁电体击穿。在他们的工作中,优化铁电沉积条件可降低粗糙度并使层间成分更加一致。为了减少层间电场,Yuejia Zhou 的团队提出了铝掺杂,而不是锆掺杂。HAO 似乎具有比 HZO 更低的极化势垒,因此具有更低的矫顽场。

总的来说,铁电存储器的前景一片光明。尽管耐用性和可靠性需要提高,但问题似乎与工艺和设计优化有关,而不是材料的基本物理特性。

本系列的最后一部分将进一步展望未来,探讨将铁电体与 2D 半导体联系起来的应用。

编辑:黄飞

-

铁电存储器有哪些优缺点2024-09-29 4045

-

集成铁电存储器的MCU有何作用2021-11-10 1547

-

信号分析仪的发展趋势是怎样的?它具有哪些优势?2021-04-14 2244

-

单片机的发展趋势2021-01-29 4825

-

铁电存储器FRAM的结构及特长2020-05-07 3808

-

半导体存储器技术及发展趋势详解2019-01-01 14365

-

铁电存储器的三个典型应用2014-04-25 6092

-

铁电存储器的技术原理2011-11-19 3158

-

铁电存储器的高精度实时时钟优势分析2010-12-11 892

-

铁电存储器工作原理和器件结构2009-10-25 13202

-

铁电存储器原理及应用比较2009-04-15 831

-

铁电存储器FRAM详解2008-01-30 5233

全部0条评论

快来发表一下你的评论吧 !