下一代3D封装竞赛正式拉响!

描述

前言:

IC封装本身就是一个复杂的市场。据最新统计,半导体行业已经开发了大约一千种封装类型。

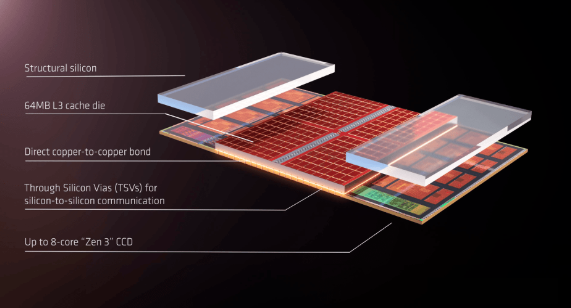

目前,第一波芯片正在使用一种称为混合键合的技术冲击市场,为基于3D的芯片产品和先进封装的新竞争时代奠定了基础。

混合键合常出现在图像传感器设计中

铜混合键合最早出现在2016年,当时索尼将这项技术用于CMOS图像传感器, 索尼从现在属于Xperi的Ziptronix获得了该技术的许可。

多年来,CMOS 图像传感器供应商一直在使用它。为了制造图像传感器,供应商在工厂中处理两个不同的晶圆:第一个晶圆由许多芯片组成,每个芯片由一个像素阵列组成;第二个晶圆由信号处理器芯片组成。

然后,使用混合键合,将晶圆与μm级的铜对铜互连键合在一起。晶圆上的die随后被切割,形成图像传感器。

这个过程与封装几乎无异。但其实大多数芯片不需要混合键合,对于封装而言,混合键合主要用于高端设计,因为它是一项涉及多项制造挑战的昂贵技术。

在当今先进封装案例中,供应商可以在封装中集成多裸片的DRAM堆栈,并使用现有的互连方案连接裸片。

通过混合键合,DRAM裸片可以使用铜互连的方法提供更高的带宽,这种方法也可以用在内存堆栈和其他高级组合的逻辑中。

为芯片制造商提供了一些新的选择,为下一代3D设计、存储立方体或3D DRAM以及更先进的封装铺平了道路。

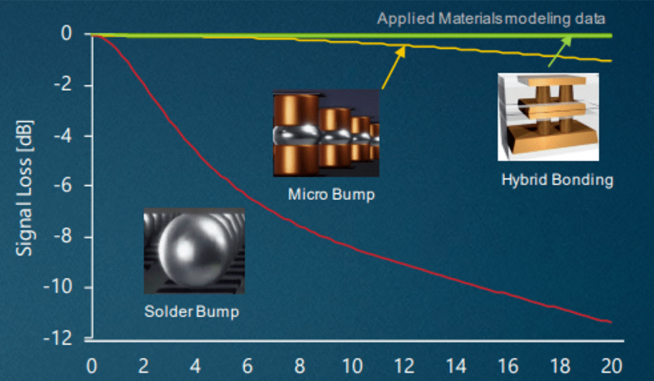

混合键合几乎消除了信号丢失

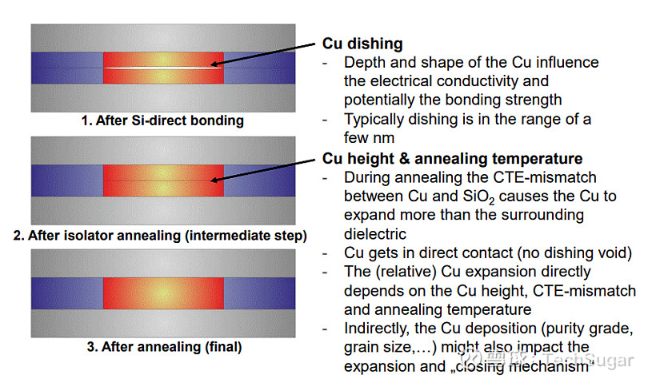

混合键合技术与传统的凸点焊接技术不同,混合键合技术没有突出的凸点,特别制造的电介质表面非常光滑,实际上还会有一个略微的凹陷。

在室温将两个芯片附着在一起,再升高温度并对它们进行退火,铜这时会膨胀,并牢固地键合在一起,从而形成电气连接。

混合键合技术可以将互联间距缩小到10 微米以下,可获得更高的载流能力,更紧密的铜互联密度,并获得比底部填充胶更好的热性能。

混合键合技术铜焊点的连接方式,让这些铜焊点承载着功率、信号以及周围的电介质,提供比铜微凸点多1000倍的连接性能。

它可以将信号延迟降低到可忽略不计的水平,同时将凸点密度提高比2.5D积分方案还高三个数量级。

混合键合的关键工艺

在传统的先进封装中组装复杂的芯片可以扩展节点,使用混合键合的先进封装则是另一种选择。

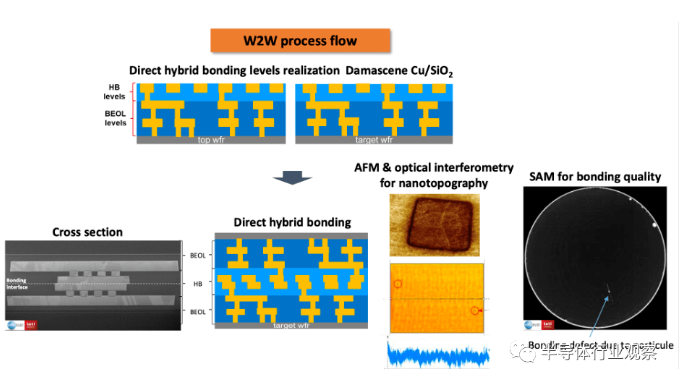

工艺步骤包括电镀(电化学沉积、ECD)、CMP、等离子体活化、对准、键合、分离和退火。

虽然这些工具已经成熟,例如,用于制造双焊点铜互连和倒装芯片键合,但这些工艺需要进一步完善以满足混合键合的需求。

其中包括小于100nm对准精度,芯片到晶圆键合和分离工具的清洁度达到新水平,具有0.5nm RMS粗糙度的出色CMP平面度以及用于最佳键合的电镀。

GlobalFoundry、英特尔、三星、台积电和联电都在致力于铜混合键合封装技术,Imec和Leti也是如此。此外,Xperi正在开发一种混合键合技术,并将该技术许可给其他公司。

产业生态系统的重要性

许多合资企业正在通过签订许可协议、合作开发新工艺和新技术,来推进混合键合产业生态的构建:

Adeia与美光、全视、天行者、SK海力士、索尼、UMC、YMTC等公司签订了许可协议;

应用材料公司的介电位、蚀刻、CMP、等离子体活化与应用材料公司新加坡先进技术开发中心的 Besi 芯片键合机相结合;

EVG的融合和混合键合以及集体组装/计量与奥地利EVG异构能力中心的ASM Pacific的0.2μm芯片键合机相结合;

英特尔和Leti开发了一种自组装工艺,用于使用水蒸发进行芯片到晶圆的键合;

Suss Microtec将其表面处理覆盖层测量工具与SET的芯片到晶圆键合机相结合;

TEL与IBM共同开发了300mm模块,采用硅载体晶圆和激光释放薄型产品晶圆。

结尾:混合键合代表一个转折点

在最需要提高性能和功率的时候,混合键合为晶体管节点缩放提供了一种可行的替代方案。

在不同工艺间的竞争愈加激烈,混合键合很快将会应用到3D DRAM、RF调制解调器和microLED的GaN/Si键合等领域。

可以毫不夸张地说,混合键合代表了整个行业的一个转折点,因为它改变了芯片制造的方式。

审核编辑 :李倩

-

三星电子在硅谷设立下一代3D DRAM研发实验室2024-01-31 1282

-

下一代 HMI 的 3 个关键考虑因素2022-10-28 571

-

研发的铜混合键合工艺正推动下一代2.5D和3D封装技术2020-10-10 7953

-

新型2.5D和3D封装技术的挑战2020-06-16 8482

-

赢创与维捷将联手开发下一代新3D打印技术2020-05-18 3279

-

利用陶瓷3D打印技术辅助研发下一代X光成像2020-04-30 2580

-

陶瓷3D打印技术,辅助研发下一代X射线成像2020-03-30 2862

-

单片光学实现下一代设计2019-09-20 3476

-

下一代SONET SDH设备2019-09-05 2497

-

随着科技的发展 3D人脸识别技术将会成为下一代身份的证明2019-01-04 2086

-

3D NAND供应商正准备迎接新的战斗,相互竞争下一代技术2018-08-23 12624

-

2016CES:Atmel下一代触摸传感技术亮相2016-01-13 3118

-

【转载】黑莓CEO:不会推下一代BB10平板电脑 专注智能手机2013-07-01 2093

-

高通下一代手机处理器3D与视频性能展示2010-03-04 810

全部0条评论

快来发表一下你的评论吧 !