分享下SpinalHDL中SpinalConfig中的三项参数

描述

》nameWhenByFile

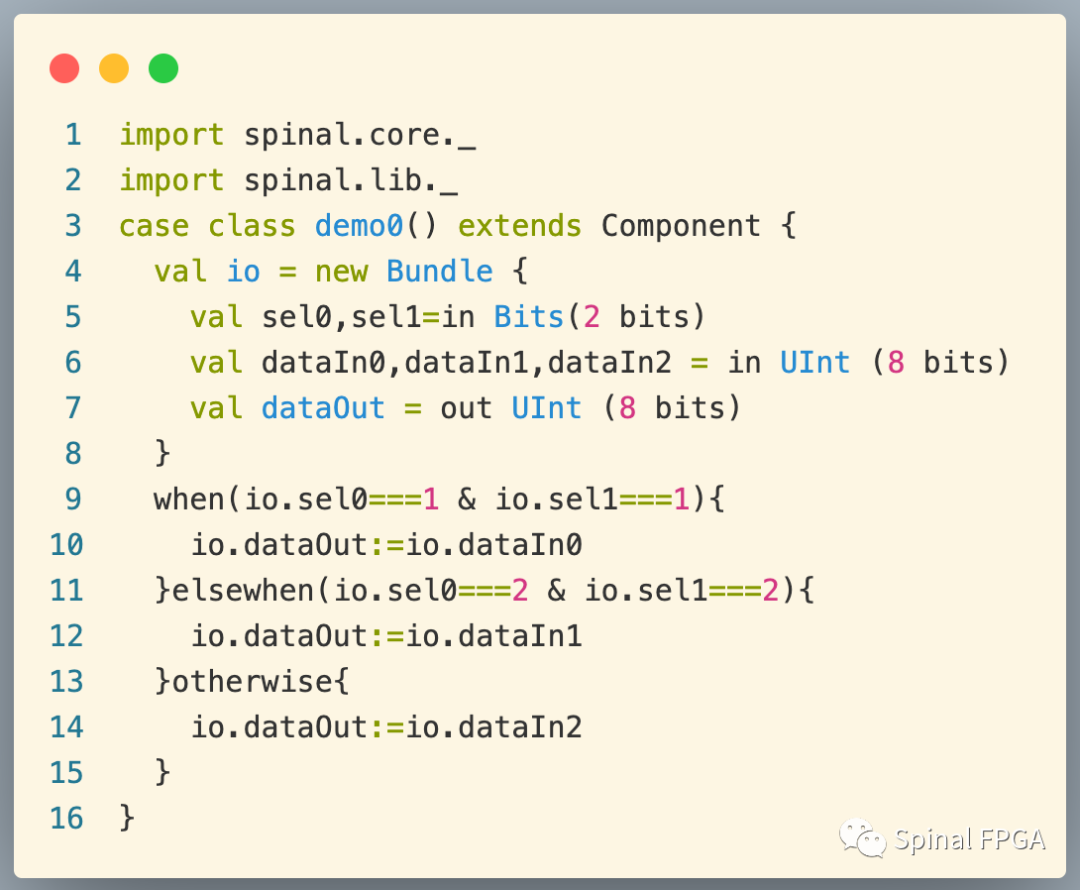

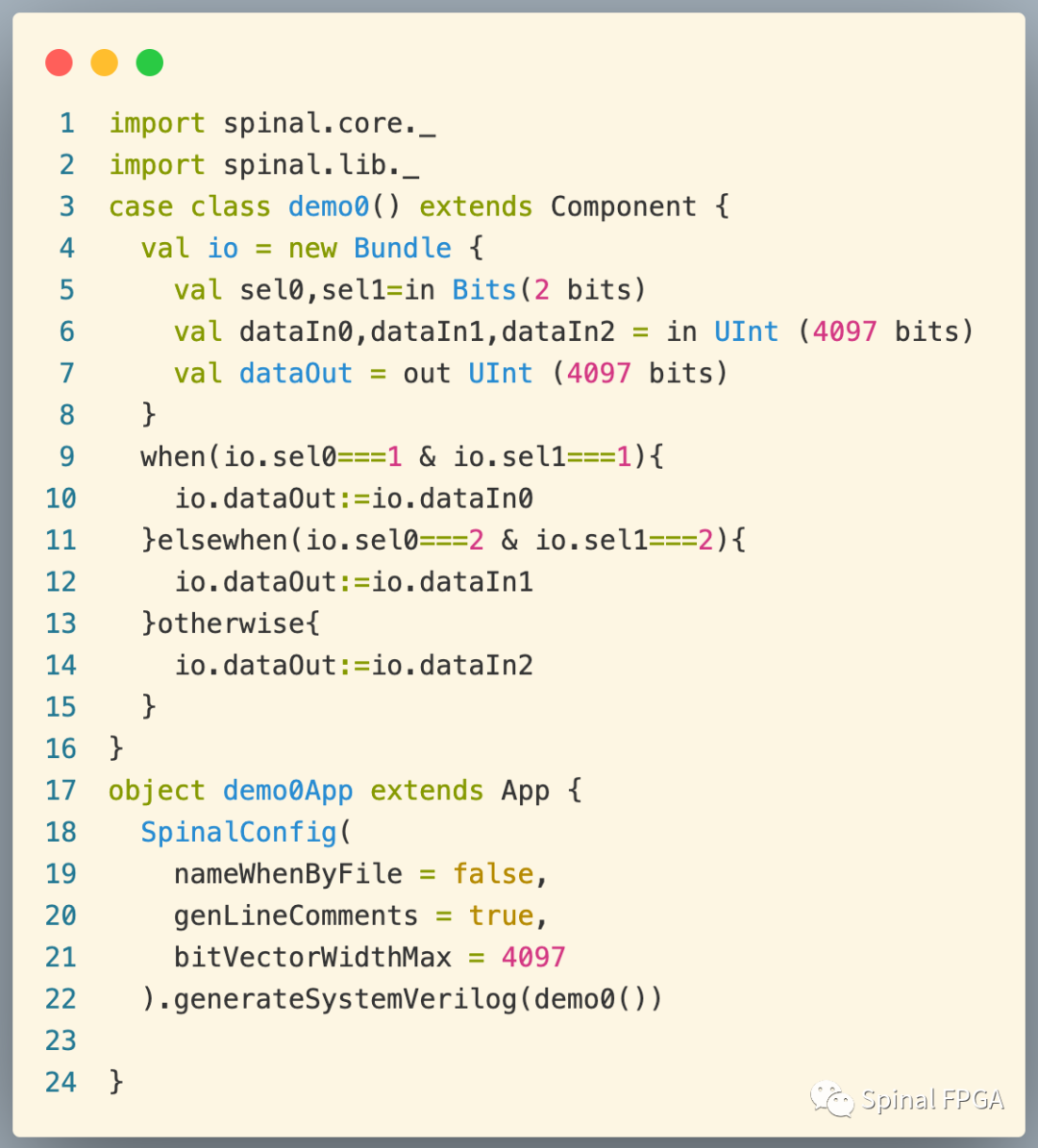

测试代码如下:

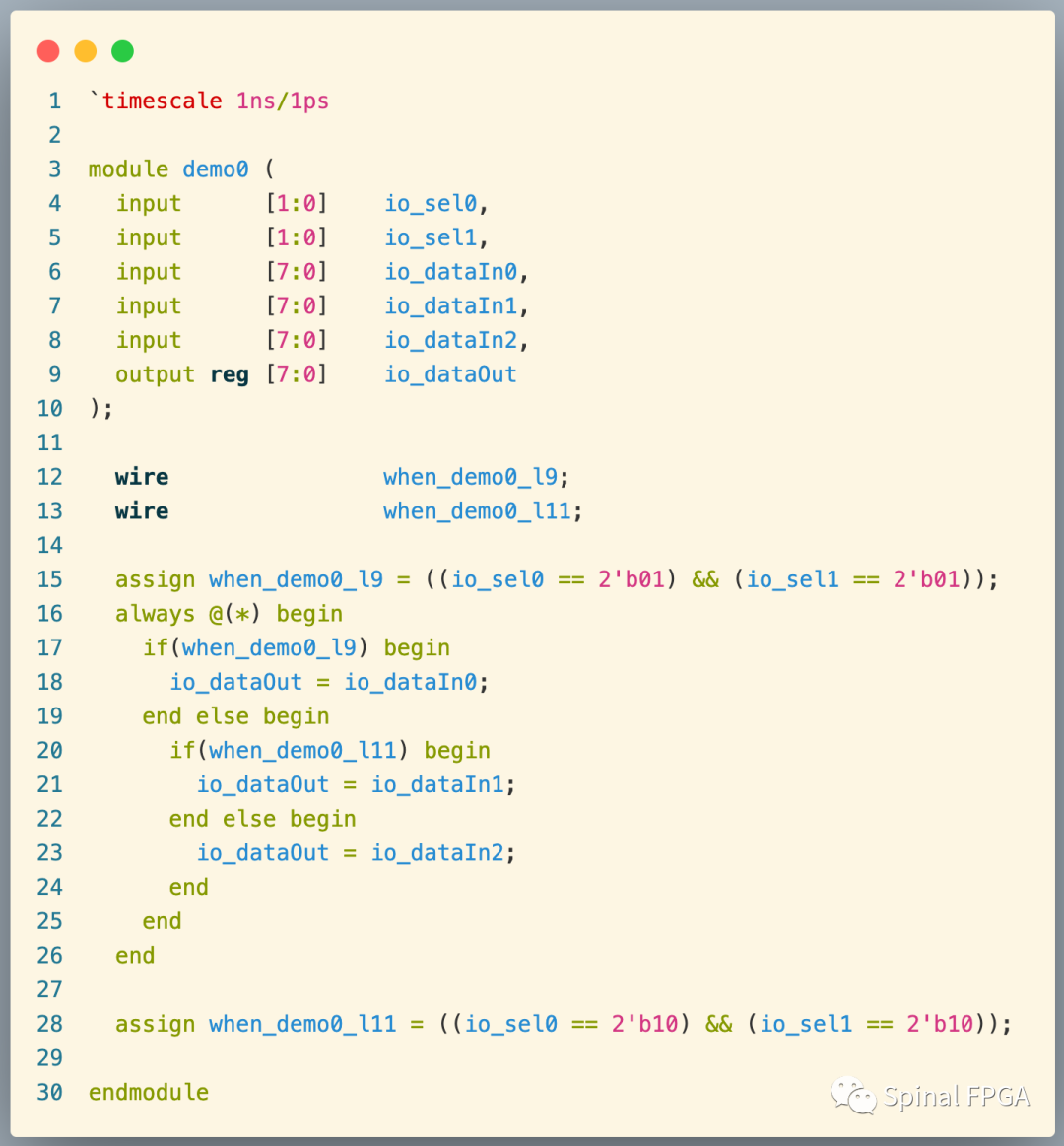

当我们采用SpinalSystemVerilog(demo0())的方式生成RTL代码时其生成的代码风格如下:

在SpinalHDL中对于when的使用,when中所包含的条件往往会生成以一个when+fileName+行号的变量来替代,看起来无非代码多了几行,并不影响功能。

因为有行号的引入,我们一旦对SpinalHDL代码中这部分代码哪怕是添加了几行注释也会引起生成代码的部分修改,虽然不影响功能,但对于那些喜欢看RTL代码的人就显得略显得不爽了。

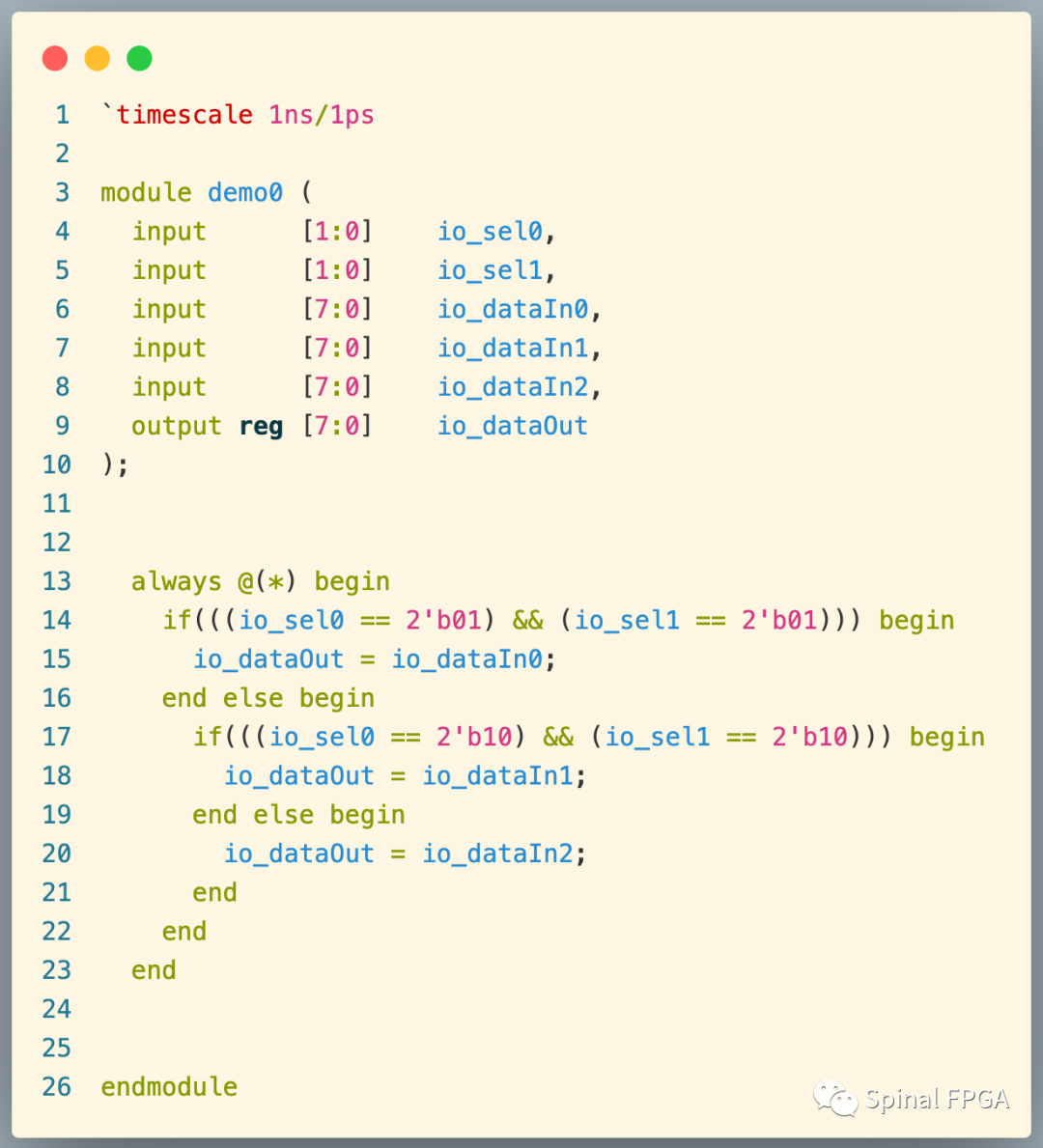

对于when的使用,可以在生成RTL代码时采用下面的形式来生成:

SpinalConfig( nameWhenByFile = false ).generateSystemVerilog(demo0())

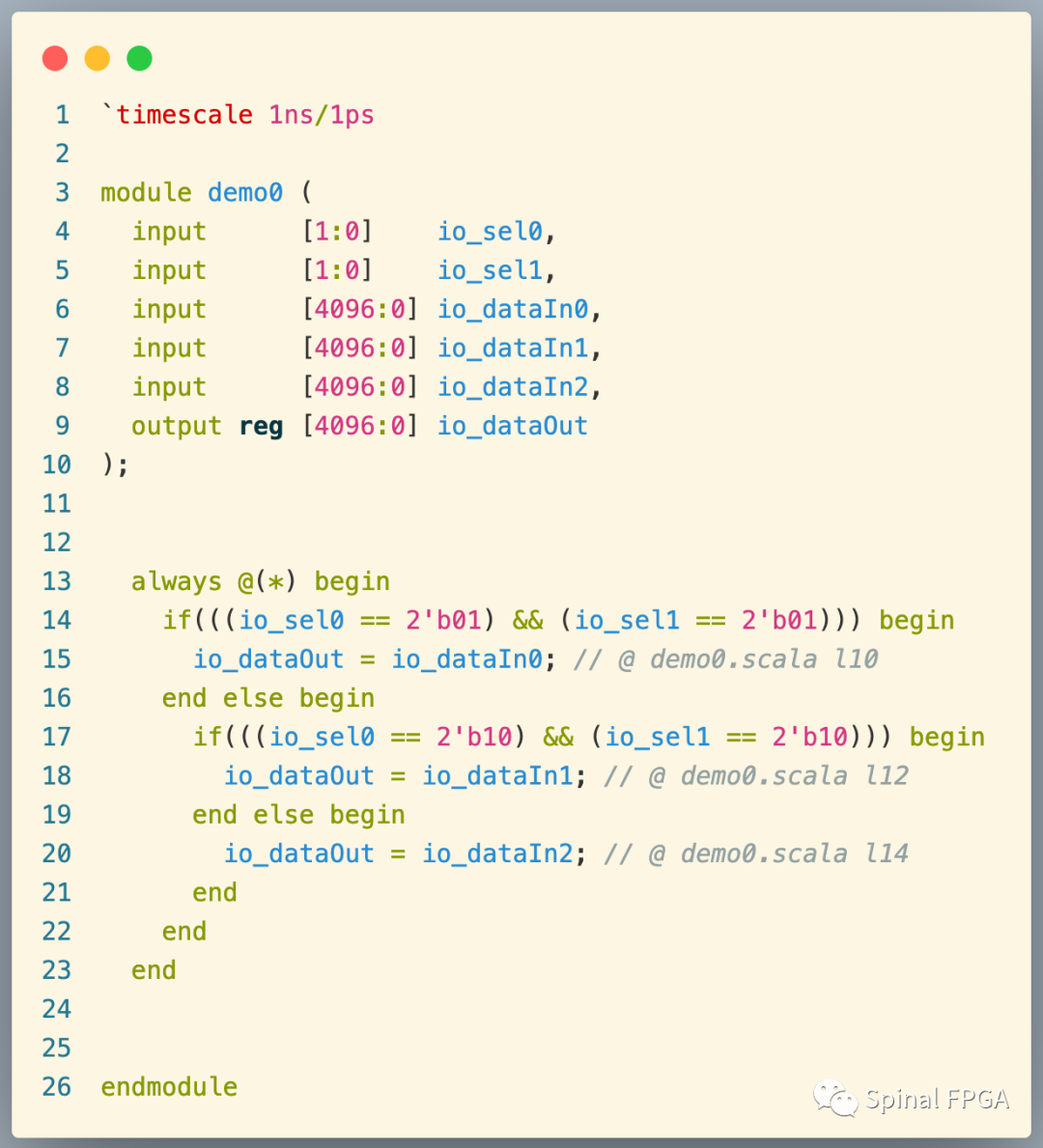

生成代码如下:

如此生成的代码不会再对when语句声明单独的变量,代码看起来和那些采用Verilog写代码的人毫无差异吧~

这对于生层的RTL尽可能减少非必要的信号名称变化。

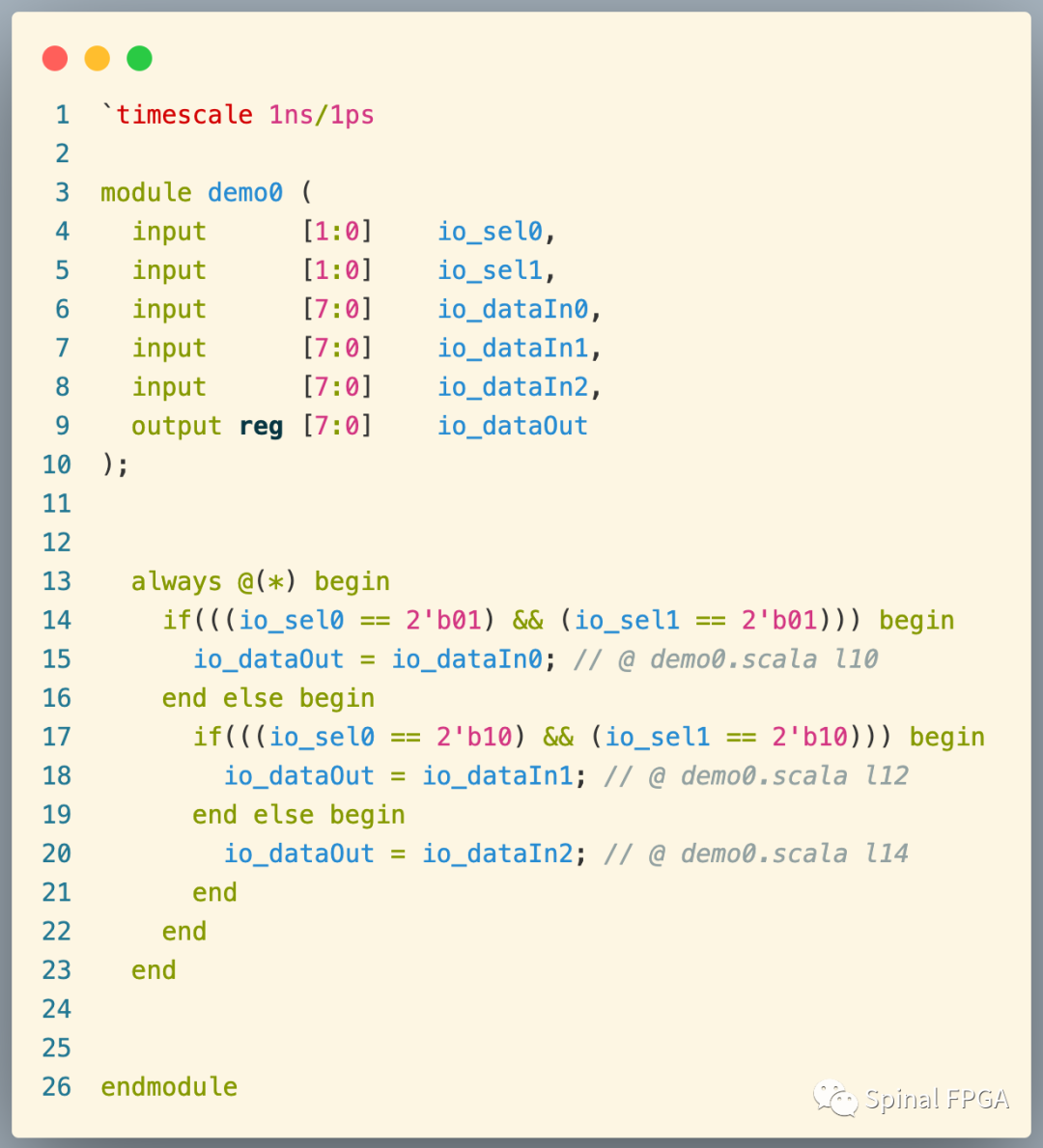

》genLineComments

更近一步,对于代码生成时采用下面的形式生成:

SpinalConfig(

nameWhenByFile = false,

genLineComments = true

).generateSystemVerilog(demo0())

此时生成的代码风格如下:

当genLineComments声明为true时,在生成RTL代码中会标注映射对应的SpinalHDL代码行号,这对于初学者在对比生成的RTL代码学习SpinalHDL还是非常的有帮助~

》bitVectorWidthMax

SpinalHDL中对于信号位宽默认是最大不超过4096(Intel DDR校准控制IP里面就有信号位宽就是4096 bit位宽),当设计里定义了信号 位宽超过4096,则会在生成RTL代码时报错,可通过SpianlConfig中的bitVectorWidthMax对最大位宽进行修改:

审核编辑:刘清

-

在SpinalHDL中如何快速地实现总线连接2022-11-28 1469

-

安规三项2021-08-03 6646

-

关于SpinalHDL中的验证覆盖率收集简单说明2022-06-24 3557

-

在SpinalHDL中关于casez的使用2022-07-06 4627

-

在SpinalHDL中的代码组织结构如何实现Component参数化设计呢2022-07-21 2552

-

请问SpinalHDL中的Area到底是什么意思2022-07-22 2424

-

如何在SpinalHDL里启动一个仿真2022-07-26 4047

-

三项闪联国际标准文本明年2月公布2009-12-29 887

-

iOS 14和tvOS 14系统更新,HomeKit迎来三项重要功能2020-03-11 5352

-

在SpinalHDL中的对应关系及声明形式2022-07-03 2546

-

SpinalHDL中Bundle数据类型的转换2022-10-17 2224

-

针对电子设备中基于MEMS显示的三项预测2022-11-02 555

-

国际认证三项电池CTL决议最新动态2023-08-29 2267

-

不同型号的三项电容可以串联吗?2023-11-15 3526

-

浅析SpinalHDL中Pipeline中的复位定制2024-03-17 1923

全部0条评论

快来发表一下你的评论吧 !