SiC MOSFET:栅极-源极电压的浪涌抑制方法-浪涌抑制电路

模拟技术

描述

在上一篇文章中,简单介绍了SiC功率元器件中栅极-源极电压中产生的浪涌。从本文开始,将介绍针对所产生的SiC功率元器件中浪涌的对策。本文先介绍浪涌抑制电路。

关于SiC功率元器件中栅极-源极间电压产生的浪涌,在之前发布的Tech Web基础知识 SiC功率元器件 应用篇的“SiC MOSFET:桥式结构中栅极-源极间电压的动作”中已进行了详细说明。

浪涌抑制电路

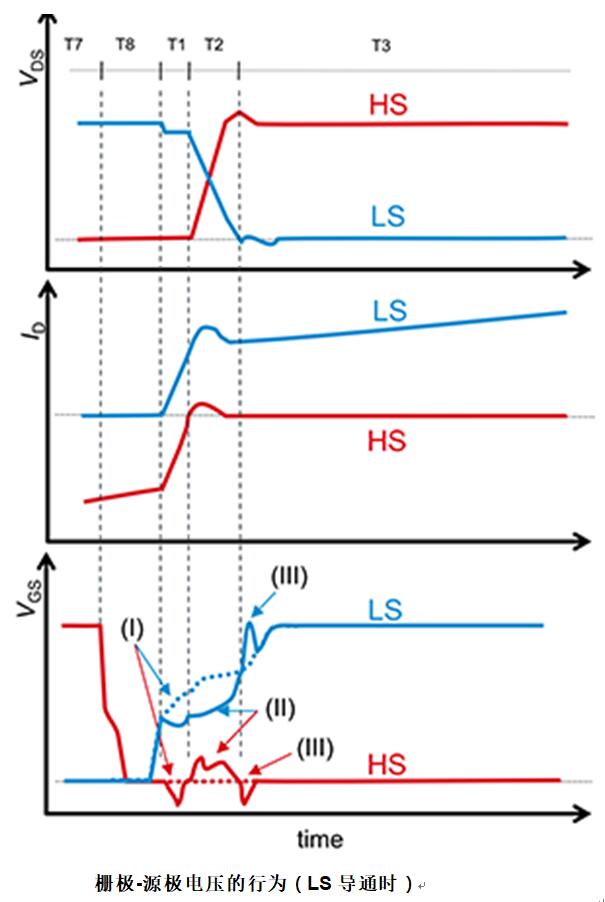

如上一篇所述,SiC功率元器件中栅极-源极电压(VGS)的正浪涌在开关侧和非开关侧均有发生,但是尤其会造成问题的是在LS(低边)导通时的非开关侧(HS:高边)的事件(II)。右侧的波形图与上一篇中给出的波形图相同。

其原因是开关侧已经处于导通状态,因此,当非开关侧的正浪涌电压超过SiC MOSFET的栅极阈值电压(VGS(th))时,HS和LS会同时导通并流过直通电流。

只是由于SiC MOSFET的跨导比Si MOSFET的跨导小一个数量级以上,因此不会立即流过过大的直通电流。所以即使流过了直通电流,也具有足够的冷却能力,只要不超过MOSFET的Tj(max),基本上没有问题。然而,直通电流毕竟是降低系统整体效率的直接因素,肯定不是希望出现的状态,因此就有必要增加用来来抑制浪涌电压的电路,以更大程度地确保浪涌电压不超过SiC MOSFET的VGS(th)。

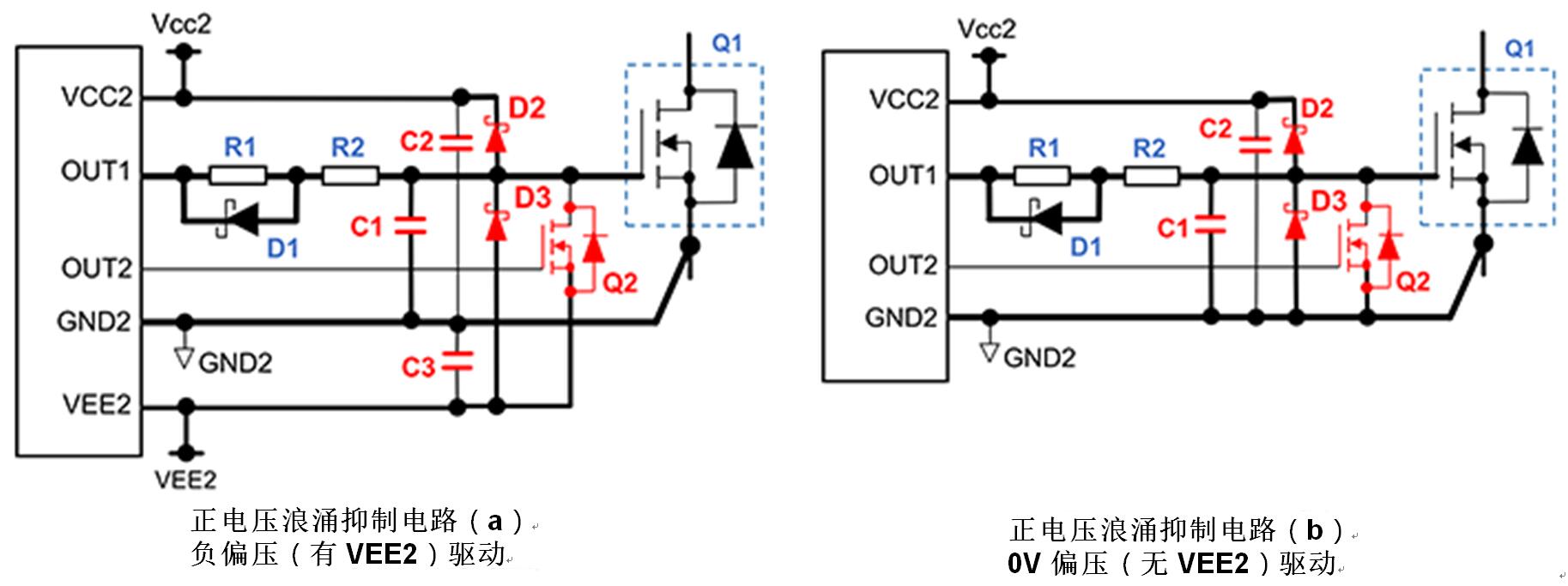

抑制电路的示例如下。这些电路图是在SiC MOSFET的普通驱动电路中增加了浪涌抑制电路后的电路示例。抑制电路(a)是使用关断用的驱动电源VEE2时的电路,而抑制电路(b)是不使用VEE2的示例。在这两个电路中,VCC2都是导通用的驱动电源,OUT1是SiC MOSFET的导通/关断信号,OUT2是镜像钳位 控制信号,GND2是驱动电路的GND。

另外,下表中列出了所添加的抑制电路的功能。添加了上面电路图中红色标记的部件。

| 効用 | 符号 | 说明 |

|---|---|---|

| 抑制正浪涌 | D2 (C2) | 抑制开关侧导通时的正浪涌电压(C2是旁路电容器) |

| 抑制负浪涌 | D3 (C3) | 抑制开关侧和非开关侧的负浪涌(C3是旁路电容器) |

| 抑制正/负浪涌 | Q2 | 抑制非开关侧的正负浪涌 |

| 抑制误导通 | C1 | 抑制非开关侧的正浪涌 |

由于D2和D3通常会吸收数十ns的脉冲,因此需要尽可能将其钳制在低电压状态 ,为此通常使用肖特基势垒二极管(SBD)。另外,选择SOD-323FL等底部电极型低阻抗封装产品效果更好。

从下一篇开始会一一详细介绍。

关键要点:

・在开关侧和非开关侧均会出现SiC功率元器件中栅极-源极电压(VGS)的正浪涌,但是尤其需要解决的是SiC功率元器件LS导通时在非开关侧(HS)出现的正浪涌问题。

・由于应用SiC功率元器件时,基本都需要包括其他浪涌在内的浪涌抑制对策,因此需要增加浪涌抑制电路。

审核编辑:汤梓红

-

如何消除或抑制浪涌电流?抑制浪涌电流的方法有哪些?2023-09-04 13613

-

R课堂 | SiC MOSFET:栅极-源极电压的浪涌抑制方法-总结2023-04-13 2367

-

什么是栅极-源极电压产生的浪涌2023-02-28 1740

-

SiC MOSFET:栅极-源极电压的浪涌抑制方法-正电压浪涌对策2023-02-09 2103

-

测量SiC MOSFET栅-源电压时的注意事项2022-09-20 20048

-

为产品的可靠运行保驾护航的浪涌抑制器2022-04-02 8059

-

浅谈栅极-源极电压产生的浪涌2021-06-12 3793

-

栅极是源极电压产生的浪涌吗?2021-06-10 3192

-

全SiC模块栅极误导通的处理方法2018-11-27 2435

-

防浪涌电路图----浪涌电流抑制电路2018-01-11 70865

-

抑制变频器中的微浪涌电压方法2011-08-04 5377

全部0条评论

快来发表一下你的评论吧 !